ONE INDUSTRIAL AVENUE, LOWELL, MASSACHUSETTS 01851, TEL. (617) 459-5000, TWX 710 343-6769, TELEX 94-7421

The Buffered Asynchronous Communications Controller adds data transmission and reception capabilities to the standalone computer capabilities of several Wang systems. The controller's integrated microprocessor and multicharacter input/output buffers simplify telecommunications control procedures and reduce central processor requirements. With the controller, a Wang System can be user-programmed to emulate a variety of asynchronous terminals (e.g., a Teletype® terminal or an IBM 2741 Selectric<sup>®</sup> Typewriter Terminal), or to communicate with another comparablyequipped Wang system. Alternatively, Wang-developed asynchronous communications software is available.

### **FEATURES**

The controller has built-in microcode residing in a read only memory and also has a 1K-byte random access memory for input/output data buffering, storage of initialization information (including code translation tables and a communication control vector), and storage of current status information. Thus, separate tasks related to data transmission/reception can be performed concurrently by the controller and the central processor.

The controller supports asynchronous transmission rates from 50 to 9600 bits per second. Any one of the following rates can be set under program control via the initializing communication control vector: 50, 75, 100, 110, 134.5, 150, 200, 300, 600, 1200, 1800, 2400, 3600, 4800, 7200 or 9600 bps. Also, the following character formatting options can be selected via the communication control vector: parity (odd, even or no), the number of data bits (5, 6, 7 or 8), and the number of stop bits (1, 1.5

The controller performs operations such as the following:

- telecommunications control and data substitution for characters received in buffering

- code translation

- full or half duplex operation

- automatic insertion and removal of shift characters

- detection of received timeouts

- break signal detection and transmission

automatic delays following transmission of up to four specified characters

- sensing the secondary received data, and setting the secondary transmitted data modem signals (also called reverse or supervisory channel data signals).

Some of these features are discussed briefly in the information which follows.

### **Code Translation**

If required for a particular application, two 256-byte code translation tables (one for data transmission operations and the other for reception operations) can be loaded into the controller memory to allow interchange of data between the central processor and the controller in the Wang system's USASCII code set, regardless of the transmission code set.

### Insertion and Removal of Shift Characters

If a particular code is included in the communication control vector, the controller automatically inserts and removes shift characters, thereby eliminating the need to program each operation. Such a feature is useful when transmitting and receiving data in a code set which utilizes shift characters, e.g., when emulating an IBM 2741 terminal.

#### Status Information

The current status regarding transmission errors, break signal reception, and modem signals can be requested and received at any time. Available information with respect to received data consists of character parity and framing errors, received timeouts, and buffer overrun conditions. Available modem signals are Data Set Ready, Secondary Received Data, and Received Line Signal Detector.

## **Other Control Functions**

The controller can send and receive break signals to interrupt transmissions to or from a host computer. Also, the controller can send a disconnect signal to the modem under program control.

### CENTRAL PROCESSOR COMPATIBILITY

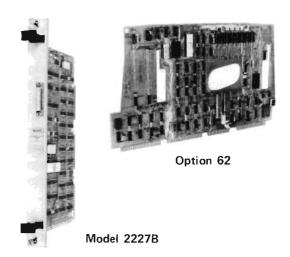

The Buffered Asynchronous Communications Controller is available in physically different but functionally equivalent versions, called the Model 2227B and Option 62. If a Wang system is equipped with a *separately housed* central processor, such as a 2200T, VP, or MVP, the Model 2227B controller is the proper choice. If a Wang system is equipped with a *console-housed* central processor, the Option 62 controller is the proper choice.

# **SPECIFICATIONS**

#### **Power Requirements**

Supplied by the central processor.

# **Electrical Connection**

A 25-pin RS-232-C, CCITT V.24 compatible female plug facilitates hookup of a modem.

# **SPECIFICATIONS (Cont.)**

### Cable

A 12-foot (3.6m) cable, equipped with 25-pin RS-232-C compatible male connectors on each end, is supplied as an accessory.

## **Asynchronous Transmission Rates**

50, 75, 100, 110, 134.5, 150, 200, 300, 600, 1200, 1800, 2400, 3600, 4800, 7200 or 9600 bits per second.

# **Character Format Options**

Parity: odd, even, or no.

Number of Data Bits: 5, 6, 7 or 8. Number of Stop Bits: 1, 1.5 or 2.

### **Communication Mode**

Full or half duplex.

### Compatible Modems

Bell 103, 202, or 212 type, or equivalent. Null modem, available from Wang, for direct communications link.

Standard Warranty Applies

## **ORDERING SPECIFICATIONS**

An asynchronous communications controller with a microprocessor and built-in microcode capable of implementing the following operations: code translation, full or half duplex operation, automatic insertion and removal of shift characters, substitution of characters received in error, and automatic removal of received null characters. A 1K-byte RAM must be provided for storage of initialization information and current information including status and buffered input/output data. The controller must be available in a version physically suitable for installation in the central processor of the Wang system to be used for data communications.

Wang Laboratories reserves the right to change specifications without prior notice.

LABORATORIES, INC