# DATAPRODUCTS (300/600 LPM) MASTER SUPPORT and LOGISTICS VOLUME I

Models: 300 LPM PRINTERS

2273V-1 2273-1 5573

**600 LPM PRINTERS**

2273-2 5574

### **PREFACE**

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with instructions to operate, troubleshoot and repair the B300 and B600 LPM Line Printers.

The following are the Wang model numbers for the B300/B600 Band Printers.

| 5573    | 300LPM | serial printer          |

|---------|--------|-------------------------|

| 5574    | 600LPM | serial printer          |

| 2273-1  | 300LPM | parallel printer        |

| 2273-2  | 600LPM | parallel printer        |

| 2273V-1 | 300LPM | parallel remote printer |

All the printer models listed above are configured with the following options.

Maximum print columns (132)

DAVFU: Direct access vertical format unit

Standard pedestal (acoustical cabinet not used)

Universal 50/60Hz and domestic 60Hz only power supplies are used

Dataproducts Centronics compatible interface, WLI part number 726-1108, OEM

part number 257265-001.

### Second Edition (October 1984)

This edition of the OEM manual is the new converted number for and obsoletes 741-0434. Appendix B (OEM to Wang cross reference tables) has been added to this document. The material in this document may be used only for the purpose stated in the Preface. Updates and/or changes to this document will be published as Publications Update Bulletins (PUB's) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

O Copyright WANG Labs., Inc. 1979, 1984

### **B-SERIES**

# MASTER SUPPORT AND LOGISTICS MANUAL

VOLUME I

300 LPM, 600 LPM, AND 1000 LPM LINE PRINTERS **GENERAL DESCRIPTION**

THEORY OF OPERATION

© Dataproducts Corp. 1982

6200 CANOGA AVENUE WOODLAND HILLS, CALIFORNIA 91365 **MAINTENANCE**

All rights reserved. No part of this document may be reproduced without the express permission of Dataproducts Corporation.

The material in this document is for informational purposes and is subject to change without notice.

### SPECIAL NOTE TO READER

Despite every reasonable effort by Dataproducts Corporation, a manual of this scope may contain errors, omissions, or ambiguities. To a large extent, we depend upon feedback from our users to correct this situation. We urge you, therefore, to let us know how you think this manual can be improved. The best way to do this is to use the Reader's Comment Sheet located at the back of the manual.

### **RELATED PUBLICATIONS**

| <u>Title</u>                                                                                | Publication<br>Number |

|---------------------------------------------------------------------------------------------|-----------------------|

| Operator's Guide, B-Series Line Printers,<br>Models 300 LPM/600 LPM                         | 255136                |

| Operator's Guide, B-Series Line Printers, with Acoustic Cabinet                             | 267720                |

| Maintenance Guide, B-Series Line Printers,<br>Models 300 LPM/600 LPM                        | 255137                |

| Maintenance Guide, B-Series Line Printers,<br>Models 300 LPM/600 LPM, with Acoustic Cabinet | 267714                |

| Maintenance Guide, B-Series Line Printers,<br>Model 1000 LPM                                | 267701                |

| Schematics Package, B-Series Line Printers,<br>Models 300 LPM/600 LPM                       | 255122                |

| Schematics Package, B-Series Line Printers, Model 1000 LPM                                  | 267709                |

### Ordering Information

The publications above may be ordered as follows:

For orders by telephone, call

(213) 887-8033

For orders by telex, use

67 4473 DATAPRO LSA

For orders by mail, address to

DATAPRODUCTS CORPORATION 21300 Roscoe Boulevard Canoga Park, California 91304 ATTN: Material Services

### TRAINING INFORMATION

## DATAPRODUCTS HAS A VARIETY OF TRAINING FORMATS AVAILABLE TO MEET YOUR EDUCATIONAL NEEDS:

THE B-SERIES PRINTER TRAINING COURSE: A 5 day analysis of the B-Series Line Printers, ideal for Teachers, Engineers, Support Personnel, or others requiring an in-depth understanding of B-Series Line Printer technology. Regularly scheduled classes are conducted in Woodland Hills, California. Special classes may be conducted at your facility.

THE B-SERIES INSTRUCTOR TRAINING GUIDE: The Instructor Training Guide provides all necessary information to accurately conduct a training course on Dataproducts B-Series Line Printers. The guide provides the instructor with overall course strategy, detailed theory of operation, lecture preparatory notes, laboratory directions and sample problems, exams, exam answer sheets, and viewgraph slide masters.

THE B-SERIES STUDENT TRAINING GUIDE: Used by the student in conjunction with the training course, this text provides pictorial aids which simplify concepts.

THE B-SERIES SLIDE/CASSETTE TRAINING PROGRAM: This Slide/Cassette Program delivers a sound module-level understanding of the B-Series printers, enabling the trainee to perform all required maintenance, calibrations and adjustments, disassembly and reassembly, and to troubleshoot and resolve printer problems in a logical and orderly way. Lecture and laboratory are presented via photographic slides and tape cassettes. Each program includes a B-Series Maintenance Guide and a slide/cassette Student Guide.

FOR REGISTRATION OR ORDERING INFORMATION, CALL:

DATAPRODUCTS

TECHNICAL EDUCATION CENTER

(213) 887-8489

Telex: 67-4473

### PRODUCT REPAIR AND REFURBISHMENT

Dataproducts Corporation provides comprehensive repair services for all product lines.

### CCA and Sub-Assembly Repair

Circuit card and sub-assemblies are tested and repaired utilizing components and assembly/test procedures which meet or exceed original product specification.

### Printer Repair and Refurbishment

Printer refurbishment programs are structured to provide basic repairs or to completely rebuild to original specifications.

### Custom Programs

Dedicated personnel are available to discuss your repair needs and to develop custom programs tailored to your requirements.

For pricing and additional information contact:

Dataproducts Corporation Customer Services Division 21300 Roscoe Boulevard Canoga Park, CA 91304

Attention: Repair and Refurbishment

Telephone: (213) 888-4079

Telex: 67-4473

### TABLE OF CONTENTS

| Section |           | <u>Title</u>                                   | Page |

|---------|-----------|------------------------------------------------|------|

| I       | GENERAL   | DESCRIPTION                                    |      |

|         | 1.1 Intro | oduction                                       | 1-1  |

|         | 1.1.1     | Contents and Format                            | 1-1  |

|         | 1.1.2     |                                                | 1-1  |

|         |           | ter Design                                     | 1-1  |

|         | 1.2.1     |                                                | 1-5  |

|         | 1.2.2     |                                                | 1-5  |

|         | 1.2.3     | - 0                                            | 1-5  |

|         |           | embly Description                              | 1-11 |

|         | 1.3.1     |                                                | 1-11 |

|         | 1.3.2     |                                                | 1-16 |

|         | 1.3.3     |                                                | 1-17 |

|         | 1.3.4     |                                                | 1-19 |

|         | 1.3.5     |                                                | 1-23 |

|         | 1.3.6     |                                                | 1-25 |

|         | 1.3.7     | 7 Fan Assemblies                               | 1-25 |

|         | 1.3.8     | 8 Harness Assemblies                           | 1-26 |

|         | 1.4 Opti  | ions and Accessories                           | 1-27 |

|         | 1.4.      | Multiple Band Sensing and Character Sets       | 1-27 |

|         | 1.4.2     |                                                | 1-27 |

|         | 1.4.2     |                                                | 1-27 |

|         | 1.4.      | •                                              | 1-28 |

|         | 1.4.      | 5 Input/Output Harness Assemblies              | 1-29 |

|         | 1.4.6     | 6 Tape Controlled Vertical Format Unit (TCVFU) | 1-30 |

|         | 1.4.7     | 7 Direct Access Vertical Format Unit           |      |

|         |           | (DAVFU)                                        | 1-30 |

|         | 1.4.      | 8 Forms Length Selector Assembly               | 1-30 |

|         | 1.4.      |                                                | 1-31 |

|         | 1.4.      | 10 Elapsed Time Meter Assembly                 | 1-31 |

|         | 1.4.      | 11 Line Filter Assembly                        | 1-31 |

|         | 1.4.      | 12 Pedestal Assembly and Paper Shelf Assembly  | 1-31 |

|         | 1.4.      | •                                              | 1-32 |

|         | 1.4.      | · · · · · · · · · · · · · · · · · · ·          | 1-32 |

|         | 1.4.      |                                                | 1-33 |

| II      | THEORY    | OF OPERATION                                   |      |

|         |           | oduction                                       | 2-1  |

|         | 2.2 Syst  | tem Interface                                  | 2-1  |

|         | 2.2.      |                                                | 2-3  |

|         | 2.2.      |                                                | 2-6  |

|         | 2.2.      |                                                | 2-6  |

|         | 2.2.      | 4 Serial System Interface                      | 2-10 |

### TABLE OF CONTENTS (Cont'd)

| <u>Section</u> |          |         | <u>Title</u>                                    | Page  |

|----------------|----------|---------|-------------------------------------------------|-------|

|                | 2.3      | Circuit | Card Assembly Architecture and Functions        | 2-15  |

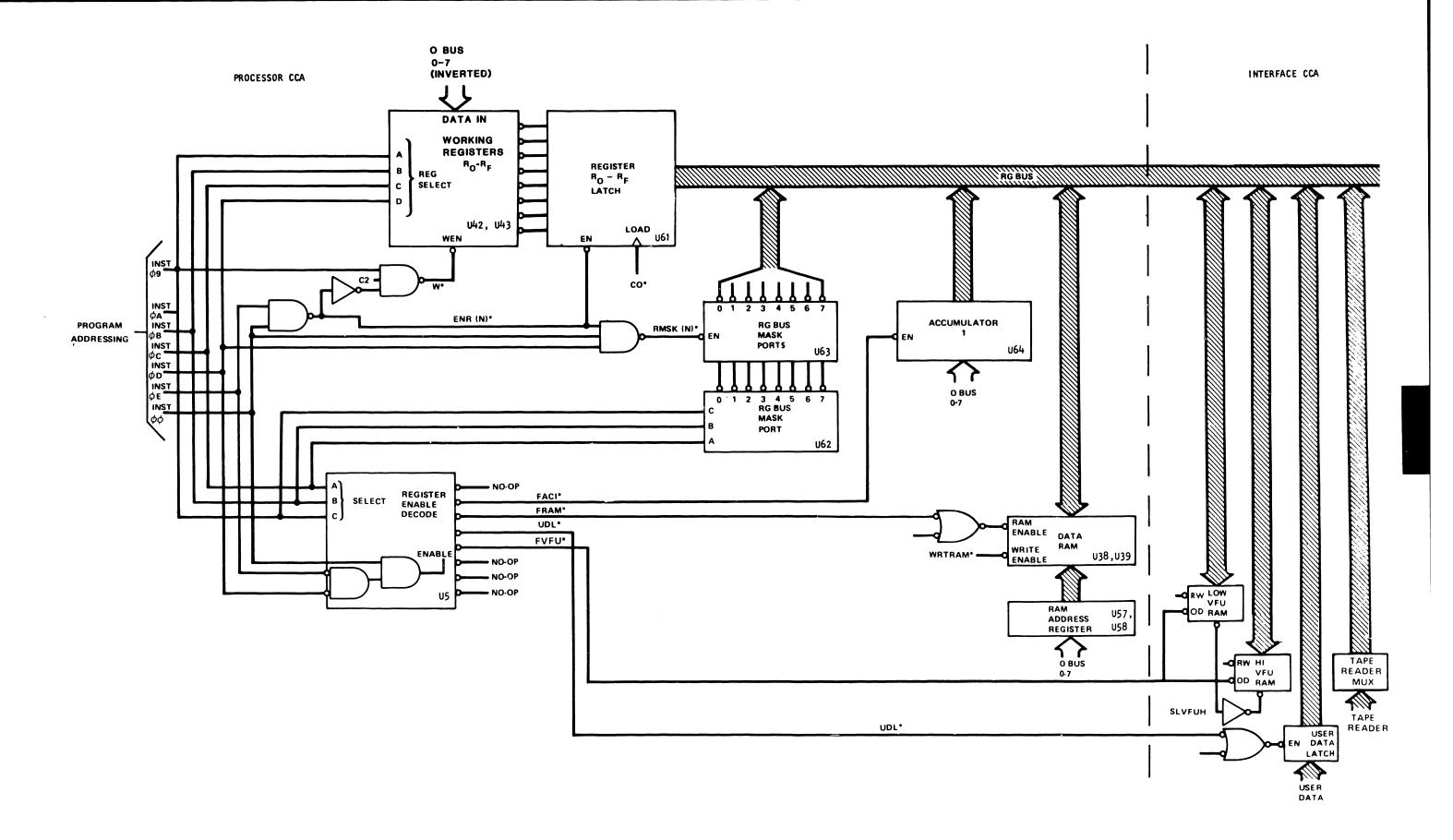

|                |          | 2.3.1   | Interface CCA                                   | 2-16  |

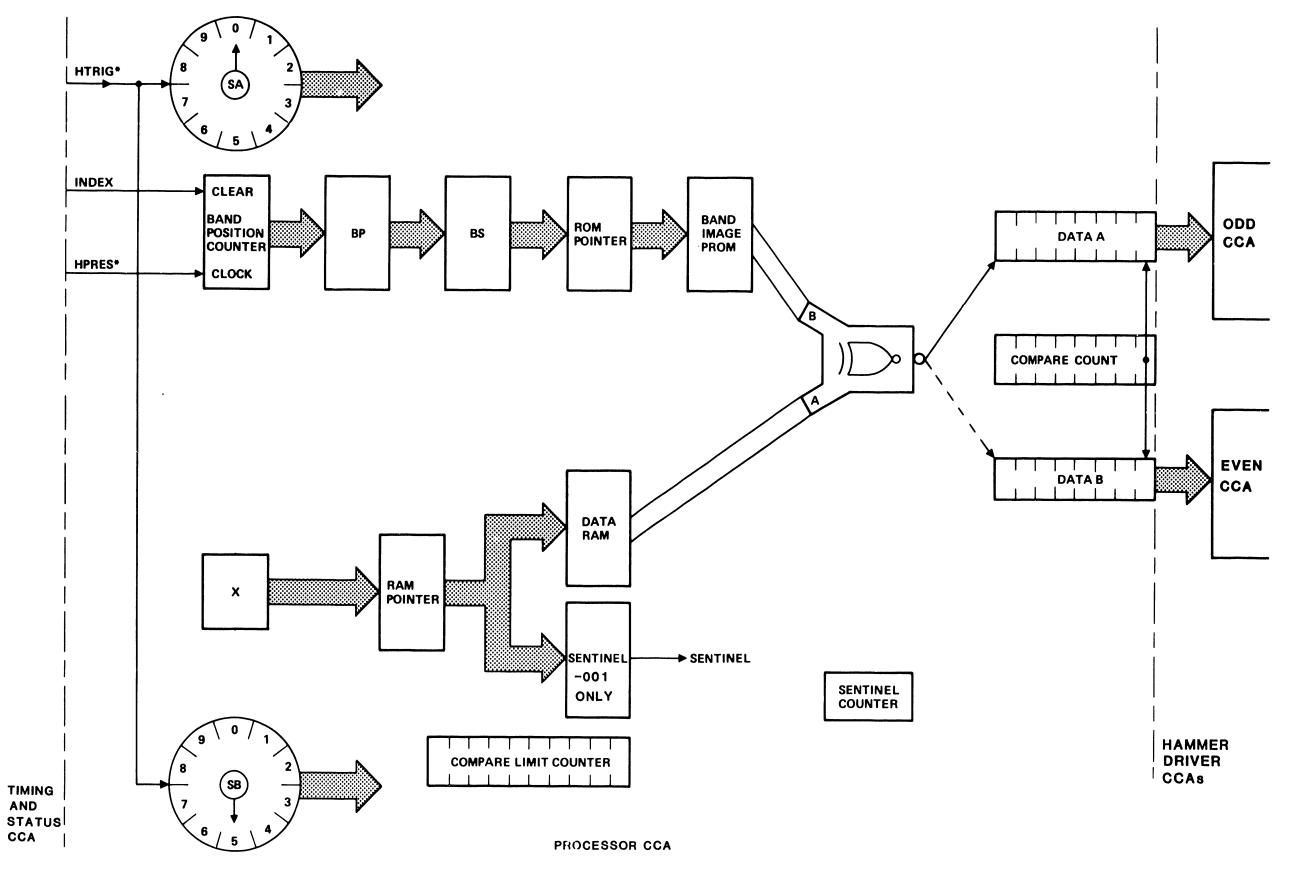

|                |          | 2.3.2   | Processor CCA                                   | 2-72  |

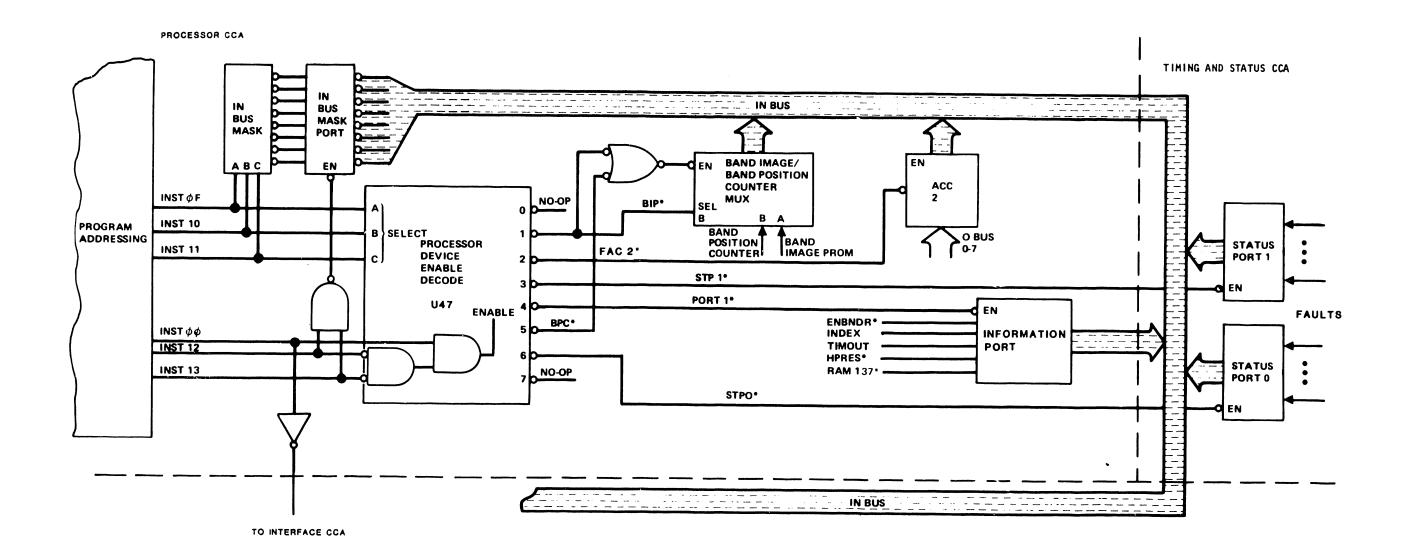

|                |          | 2.3.3   | Timing and Status CCA                           | 2-119 |

|                |          | 2.3.4   | Hammer Driver CCA                               | 2-131 |

|                |          | 2.3.5   | Power Board CCA                                 | 2-137 |

|                |          | 2.3.6   | Mother Board CCA                                | 2-146 |

|                | 2.4      | Printer | Subsystems                                      | 2-146 |

|                |          | 2.4.1   | Character Band Drive and Ribbon Drive Subsystem | 2-147 |

|                |          | 2.4.2   | Paper Clamp and Paper Feed Subsystem            | 2-149 |

|                |          | 2.4.3   | Print Subsystem                                 | 2-152 |

|                |          | 2.4.4   | Power Subsystem                                 | 2-162 |

|                | 2.5      | Format  | Control                                         | 2-102 |

|                |          | 2.5.1   | Configuration Switches                          | 2-171 |

|                |          | 2.5.2   | Control Panel Assembly                          | 2-171 |

|                |          | 2.5.3   | Forms Length Selector Switch (FLSS)             | 2-171 |

|                |          | 2.5.4   | Tape Controlled Vertical Format Unit            | 2-171 |

|                |          | 2.5.5   | Direct Access Vertical Format Unit              | 2-172 |

|                | 2.6      |         | n Description                                   | 2-173 |

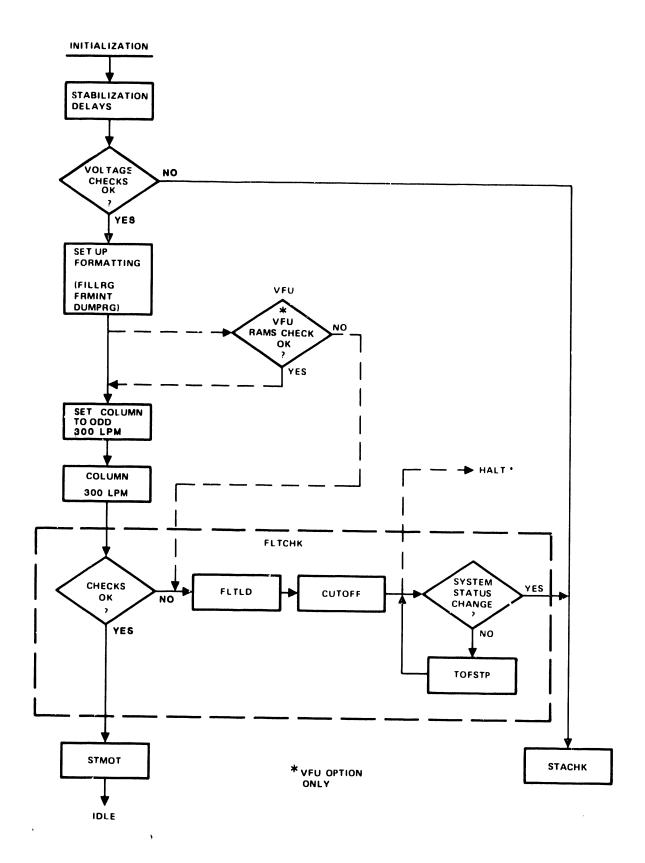

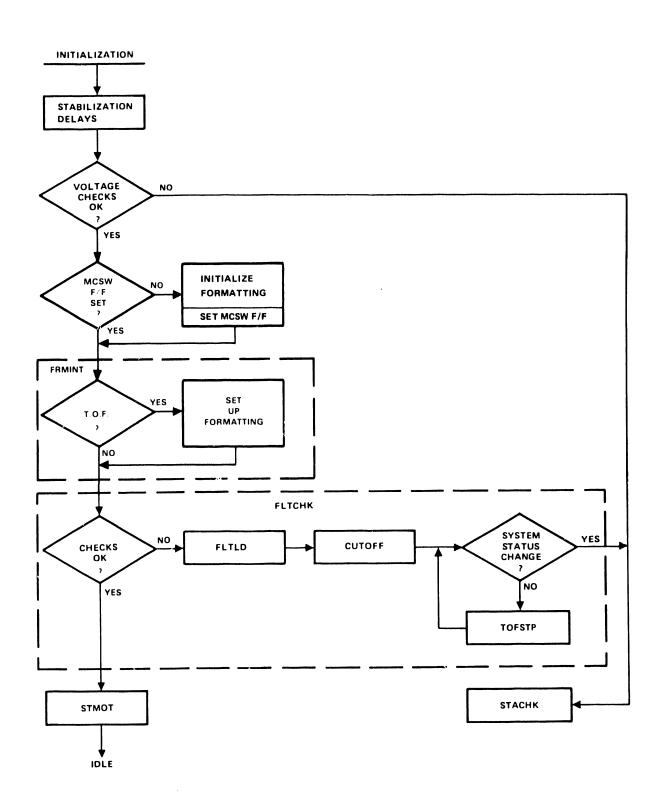

|                | 2.0      | 2.6.1   | Initialization Routine                          | 2-174 |

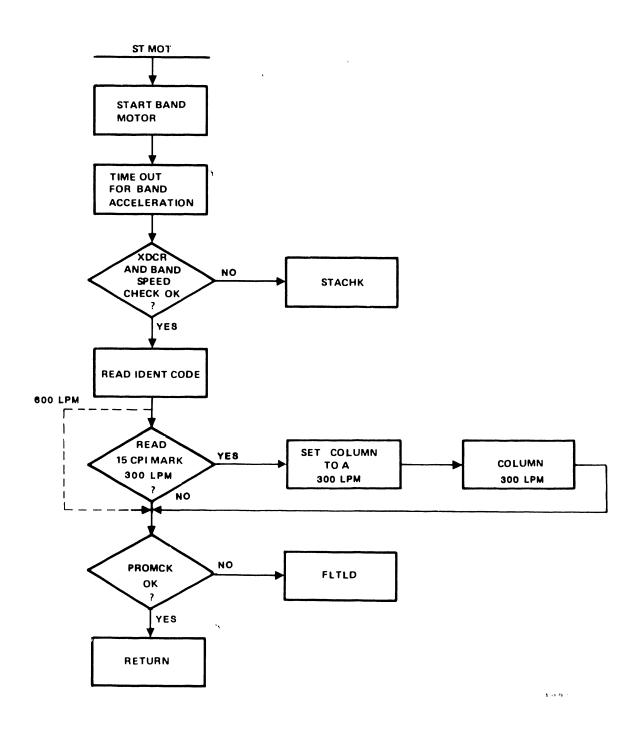

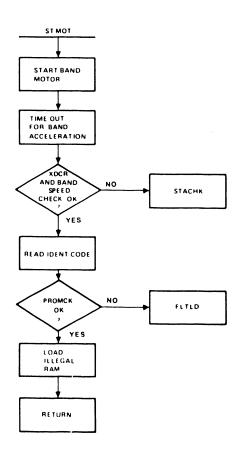

|                |          | 2.6.2   | Start Motor Routine (STMOT)                     | 2-177 |

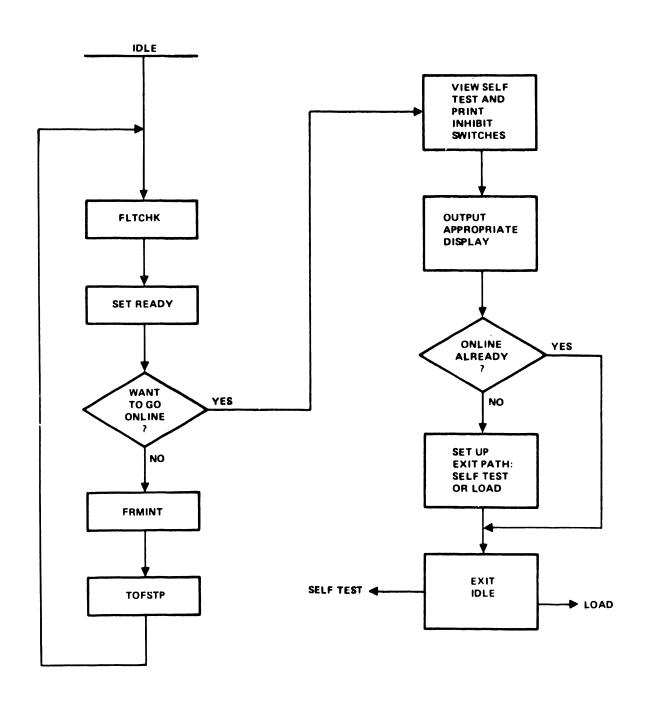

|                |          | 2.6.3   | Idle Routine                                    | 2-181 |

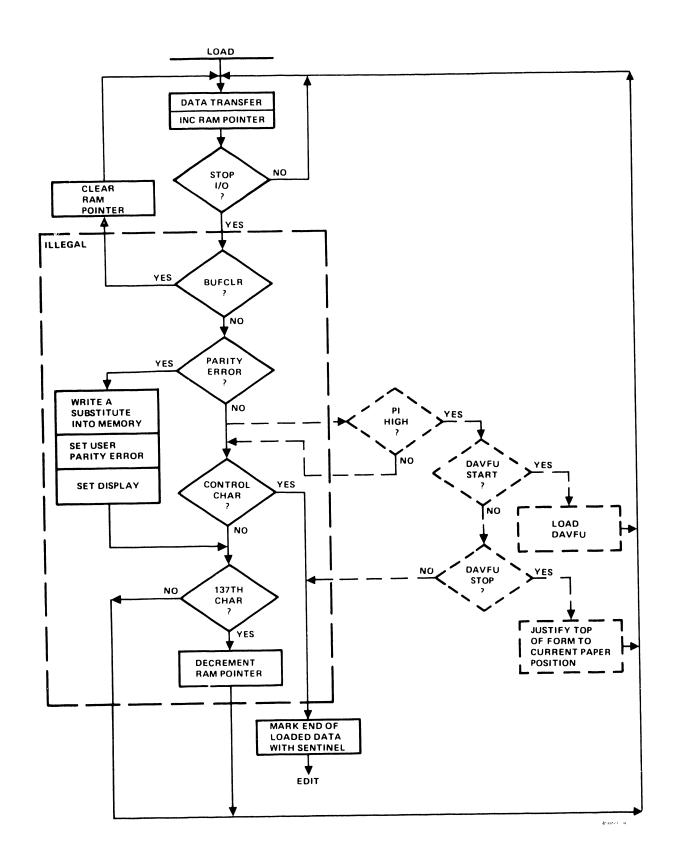

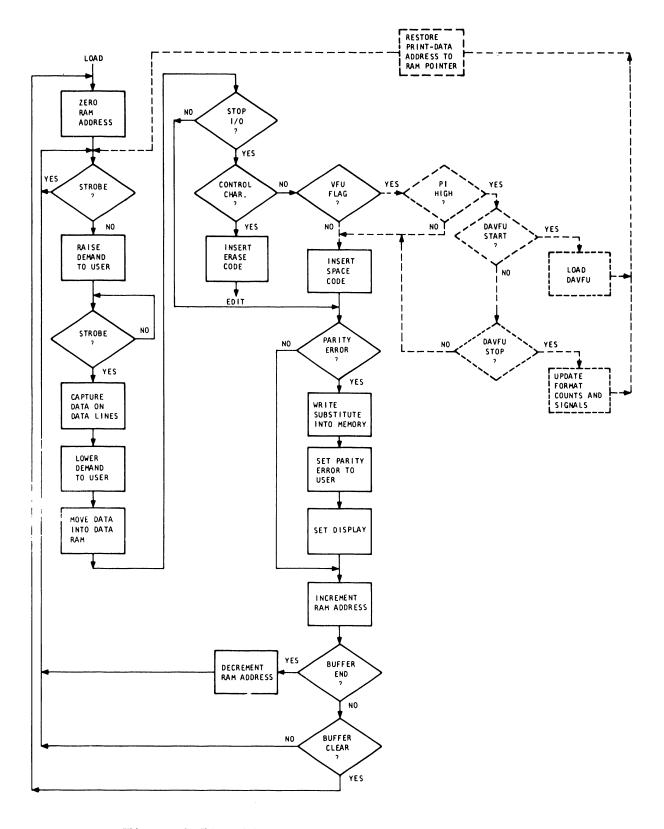

|                |          | 2.6.4   | Data Load Routine                               | 2-184 |

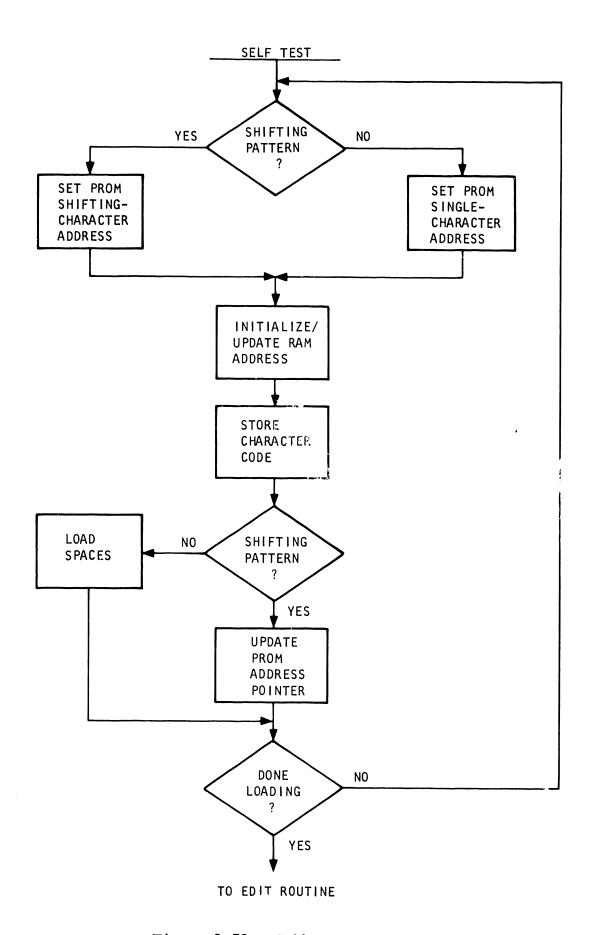

|                |          | 2.6.5   | Self-Test Routine                               | 2-136 |

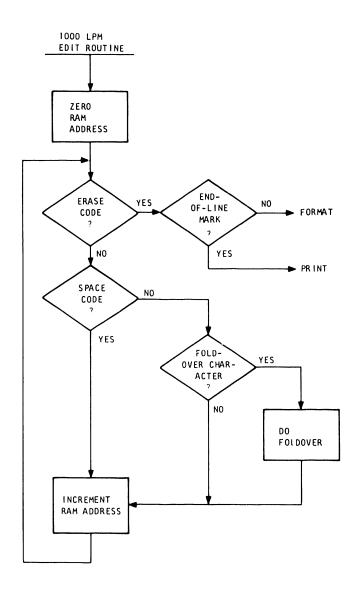

|                |          | 2.6.6   | Edit Routine                                    | 2-192 |

|                |          | 2.6.7   | Print Routine                                   | 2-197 |

|                |          | 2.6.8   | Format and Move Paper Routines                  | 2-197 |

|                |          | 2.6.9   |                                                 |       |

|                |          | 2.0.7   | System Status Check (STACHK) Routine            | 2-209 |

| Ш              |          | TENANC  |                                                 |       |

|                | 3.1      | Introdu |                                                 | 3-1   |

|                | 3.2      | Recomr  | mended Tools and Equipment                      | 3-1   |

|                | 3.3      | Adjustn | nent Procedures                                 | 3-2   |

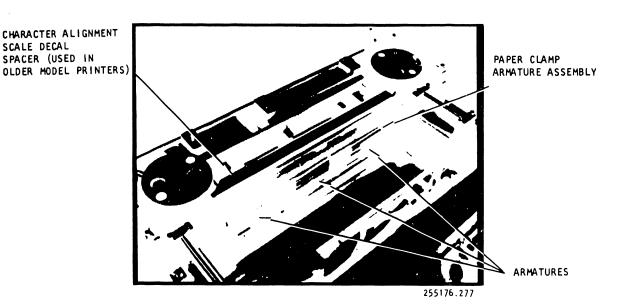

|                |          | 3.3.1   | Paper Clamp Armature Assembly Adjustment        | 3-3   |

|                |          | 3.3.2   | Platen Adjustment                               | 3-6   |

|                | 3.4      |         | al and Replacement Procedures                   | 3-8   |

|                | <i>.</i> | 3.4.1   | AC Power Switch Removal/Replacement             |       |

|                |          | • • •   | (without Acoustic Cabinet)                      | 3-9   |

|                |          | 3.4.2   | AC Power Switch and AC Distribution             |       |

|                |          |         | Harness Removal/Replacement (with               |       |

|                |          | 2 4 2   | Acoustic Cabinet)                               | 3-10  |

|                |          | 3.4.3   | Control Panel Removal/Replacement (without      |       |

|                |          |         | Acoustic Cabinet)                               | 3-12  |

### TABLE OF CONTENTS (Cont'd)

| Section |               | <u>Title</u>                                                                      | Page       |

|---------|---------------|-----------------------------------------------------------------------------------|------------|

|         | 3.4.4         | Control Panel Assembly Removal/ Replacement (with Acoustic Cabinet)               | 3-16       |

|         | 3.4.5         | Hammer Bank Assembly Removal/ Replacement                                         | 3-19       |

|         | 3.4.6         | Interlock Transition CCA Removal/ Replacement                                     | 3-22       |

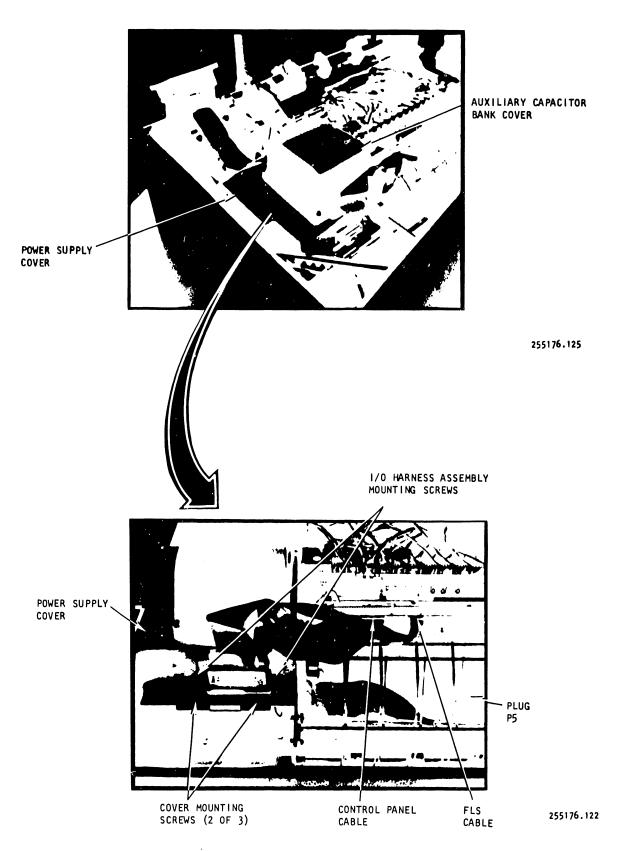

|         | 3.4.7         | I/O Harness Assembly Removal/<br>Replacement (Printers in Standard                | 3-23       |

|         | 3.4.8         | Cabinet)  I/O Harness Assembly Removal/Replacement (Printers in Acoustic Cabinet) | 3-25       |

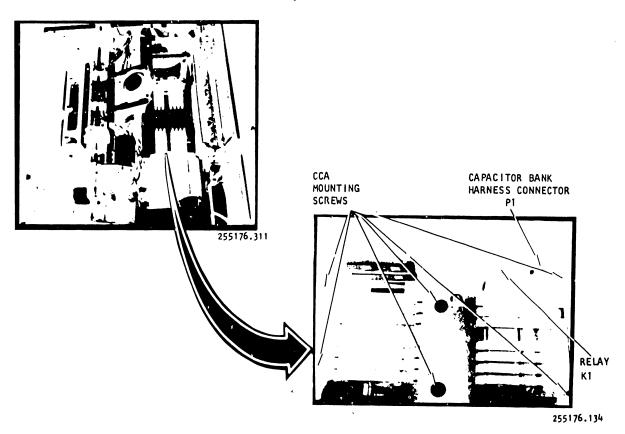

|         | 3.4.9         | Mother Board CCA Removal/Replacement                                              | 3-27       |

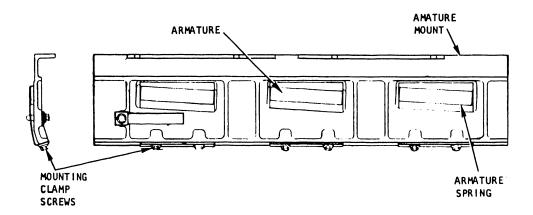

|         | 3.4.10        | 300 LPM Paper Clamp Armature Removal/                                             |            |

|         | 3.4.11        | Replacement                                                                       | 3-29       |

|         | 3.4.12        | Removal/Replacement                                                               | 3-31       |

|         | 3.4.13        | Removal/Replacement                                                               | 3-32       |

|         | 7.4.17        | (300 LPM and 600 LPM Printers Only)                                               | 3-34       |

|         | 3.4.14        | Paper Entrance Cover Removal/Replacement .                                        | 3-36       |

|         | 3.4.15        | 600 LPM/1000 LPM Paper Low Switch                                                 |            |

|         |               | Assembly Removal/Replacement                                                      | 3-37       |

|         | 3.4.16        | Paper Motion Sensor Removal/Replacement                                           | 3-38       |

|         | 3.4.17        | Platen Removal/Replacement                                                        | 3-40       |

|         |               | LIST OF ILLUSTRATIONS                                                             |            |

| Figure  |               | <u>Title</u>                                                                      | Page       |

| 1-1     | 300 LPM Print | er                                                                                | 1-2        |

| 1-2     |               | er with Pedestal (Front View)                                                     | 1-3        |

| 1-3     |               | nter with Acoustic Cabinet                                                        | 1-4        |

| 1-4     |               | Printer without Acoustic Cabinet, Major                                           |            |

|         |               | nd Subassemblies Block Diagram                                                    | 1-6        |

| 1-5     |               | Printer with Acoustic Cabinet, Major Assemblies                                   |            |

| 1-6     | 1000 LPM Prin | nblies Block Diagram                                                              | 1-7<br>1-8 |

| 1-7     |               | n Overview Block Diagram                                                          | 1-9/1-10   |

| 1-7     | •             | Drive/Ribbon Drive Assembly                                                       | 1-7/1-10   |

| 1-8     |               | d Drive/Ribbon Drive Assembly                                                     | 1-14       |

| 2-1     |               | ssembly Connector Types                                                           | 2-2        |

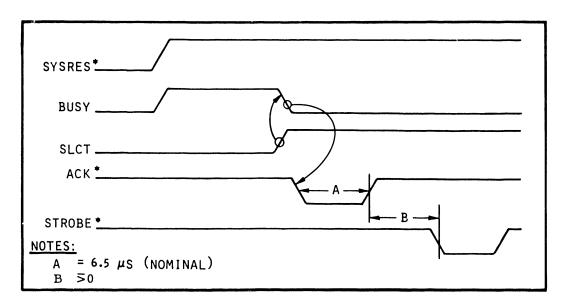

| 2-2     |               | Short Line/Long Line Handshake Routine                                            | 2-3        |

### LIST OF ILLUSTRATIONS (Cont'd)

| Figure       | <u>Title</u>                                                                                            | Page              |

|--------------|---------------------------------------------------------------------------------------------------------|-------------------|

| 2-3          | Short Line and Long Line Interface Timing Diagram                                                       | 2-4               |

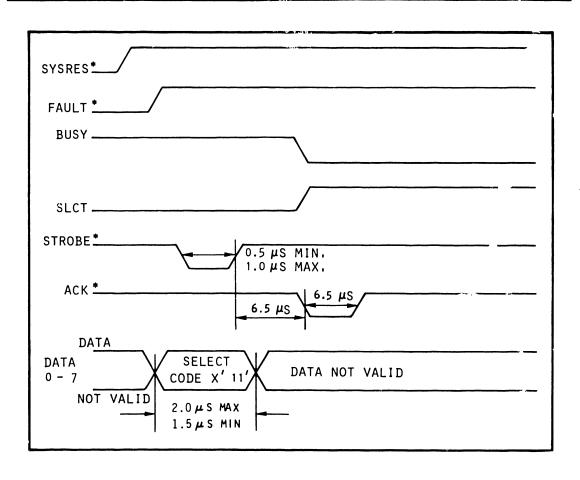

| 2-4          | Flow Diagram, Centronics-Compatible Handshake Routine                                                   | 2-7               |

| 2-5          | Centronics-Compatible Interface Select Timing Via ON/OFF                                                |                   |

| 2 (          | LINE Switch                                                                                             |                   |

| 2-6          | Centronics-Compatible Interface Select Timing Via Data Bus .                                            | 2-8               |

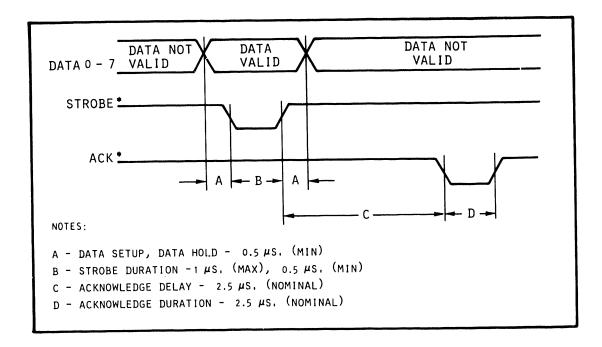

| 2-7          | Centronics-Compatible Interface Data Transfer Timing                                                    |                   |

| 2-8          | without BUSY                                                                                            | 2-9               |

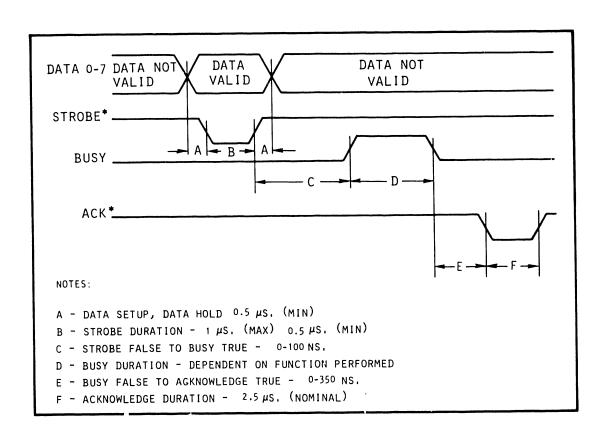

| 2-8<br>2-9   | Centronics-Compatible Interface Data Transfer with BUSY                                                 |                   |

| 2-10A        | Serial System Interface Components                                                                      | 2-11              |

| 2-10A        | Flow Diagram, Serial System Interface Communications                                                    |                   |

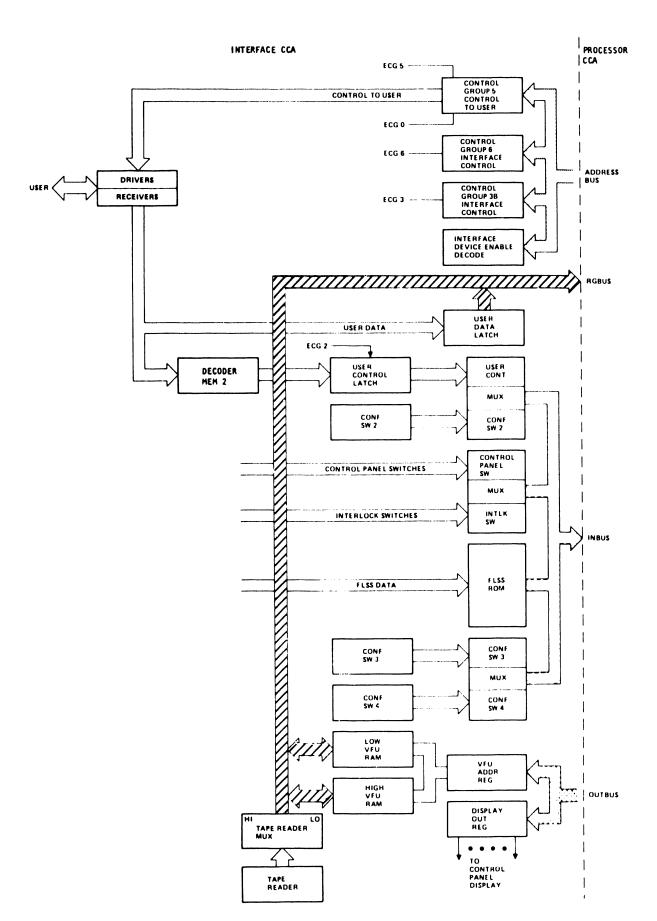

| 2-11         | Flow Diagram, Serial System Interface Communications Circuit Card Assembly Device and Bus Block Diagram | 2-15              |

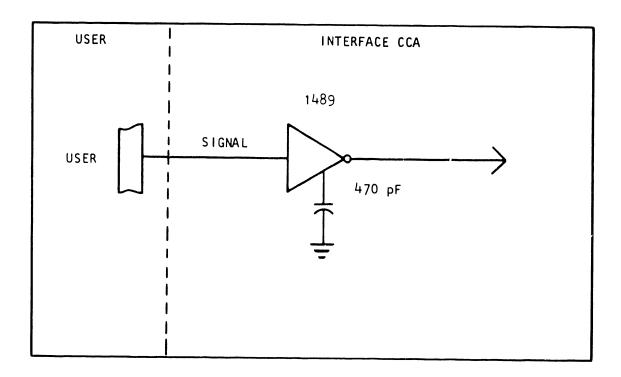

| 2-12         | Typical Short Line Interface Receiver Circuit                                                           | 2-17/2-18<br>2-20 |

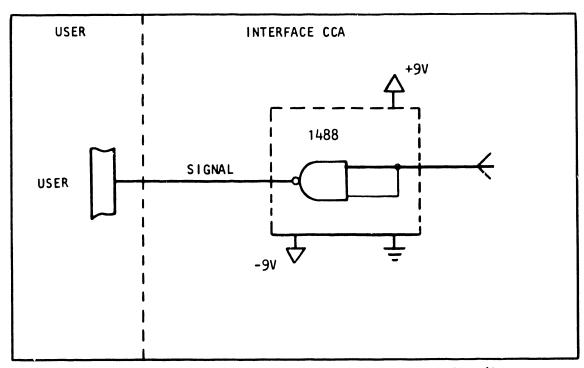

| 2-13         | Typical Short Line Interface Driver Circuit                                                             | 2-20              |

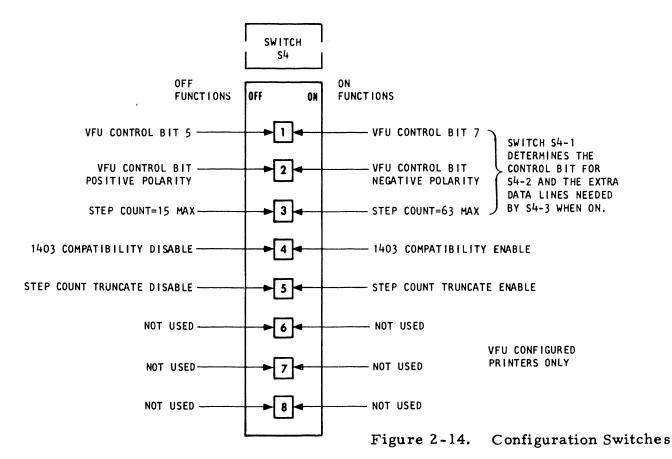

| 2-14         | Configuration Switches                                                                                  |                   |

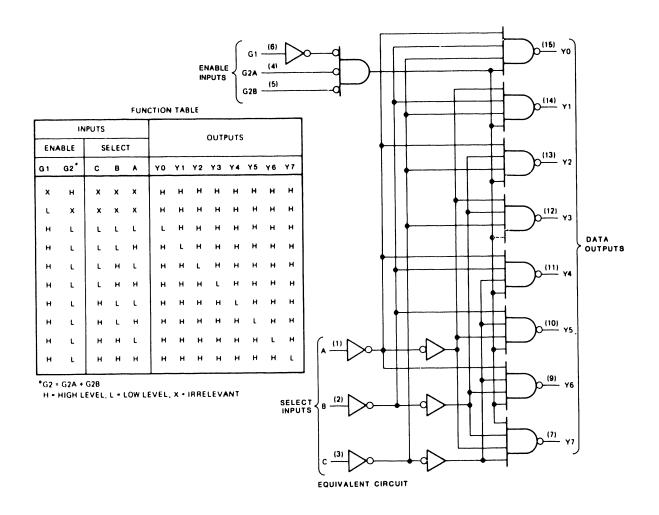

| 2-15         | Interface Device Enable Decoder (74LS138)                                                               | 2-21/2-22         |

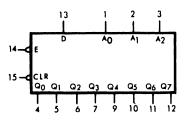

| 2-16         | Control Group 0 Latch (74259)                                                                           | 2-29              |

| 2-17         | Short Line Interface CCA Block Diagram                                                                  | 2-33              |

| 2-18         | Typical Long Line Interface Receiver Circuit                                                            | 2-36              |

| 2-19         | Typical Long Line Interface Circuit                                                                     | 2-36              |

| 2-20         | Typical Centronics-Compatible Interface Receiver Circuits                                               | 2-38              |

| 2-21         | Typical Centronics-Compatible Interface Driver Circuits                                                 | 2-38              |

| 2-22         | Centronics-Compatible Interface Block Diagram                                                           | 2-46              |

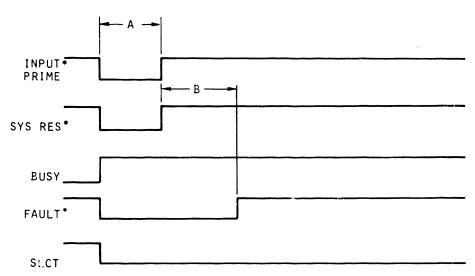

| 2-23         | INPUT PRIME Timing                                                                                      | 2-49              |

| 2-24         | Typical RS232C Receiver Circuit                                                                         | 2-51              |

| 2-25         | Typical RS232C Transmitter Circuit                                                                      | 2-52              |

| 2-26         | 20 mA Current Loop Receiver Circuit                                                                     | 2-52              |

| 2-27         | 20 mA Active Current Loop Transmitter Circuit                                                           | 2-53              |

| 2-28         | 20 mA Passive Current Loop Transmitter Circuit                                                          | 2-54              |

| 2-29         | Serial Interface Memory Map                                                                             |                   |

| 2-30         | Serial Interface Block Diagram                                                                          | 2-64              |

| 2-31         | Serial Interface CCA Functional Flow Diagram                                                            | 2-69              |

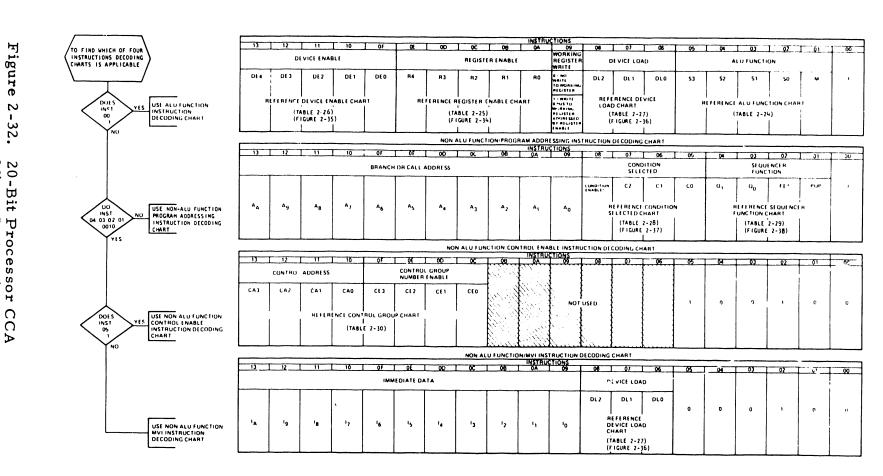

| 2-32         | 20-Bit Processor CCA, Micro-Instruction Types (300 LPM and                                              |                   |

| 2 22         | 600 LPM Only)                                                                                           | 2-74              |

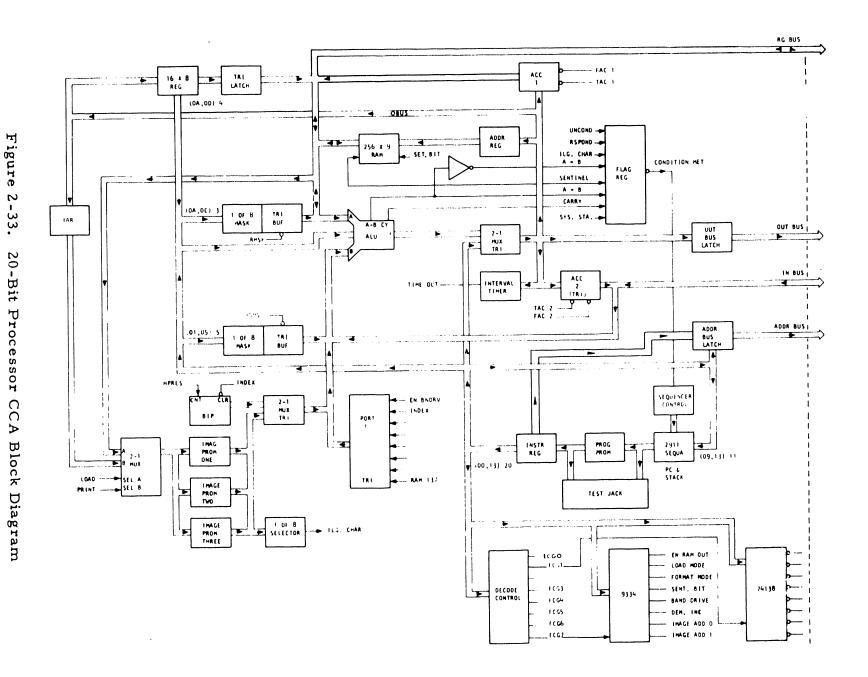

| 2-33         | 20-Bit Processor CCA Block Diagram                                                                      |                   |

| 2-34<br>2-35 | Register Enable Network                                                                                 |                   |

| 2-36         | Device Enable Network                                                                                   |                   |

| 2-36         | Device Loading Network                                                                                  |                   |

| 2-38         |                                                                                                         | 2-89/2-90         |

| 2-70         | 20-Bit Processor CCA Microsequencer Function Selector and Sequencer                                     | 2-91              |

| 2-39         | Instruction Cycle Timing                                                                                |                   |

| 2-40         | 24-Bit Processor CCA Micro-Instruction Types (1000 LPM                                                  | 2-101             |

| 13           | Printers)                                                                                               | 2 102/2 104       |

| 2-41         | 24-Bit Processor CCA Block Diagram                                                                      | 2-103/2-104       |

| 2-42         | 24-Bit Processor Instruction Cycle Timing                                                               | 2-103             |

| 2-43         | Timing and Status CCA Block Diagram                                                                     | 2-120             |

### LIST OF ILLUSTRATIONS (Cont'd)

| Figure                | <u>Title</u>                                           | Page    |

|-----------------------|--------------------------------------------------------|---------|

| 2-44                  | Fault Detection System                                 |         |

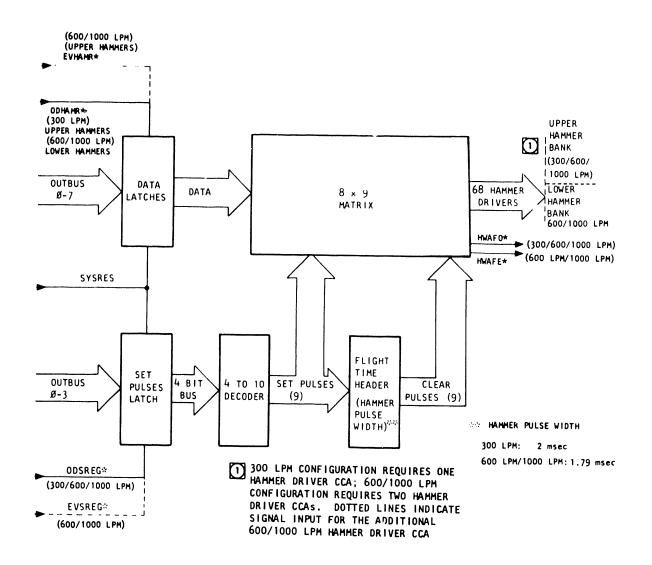

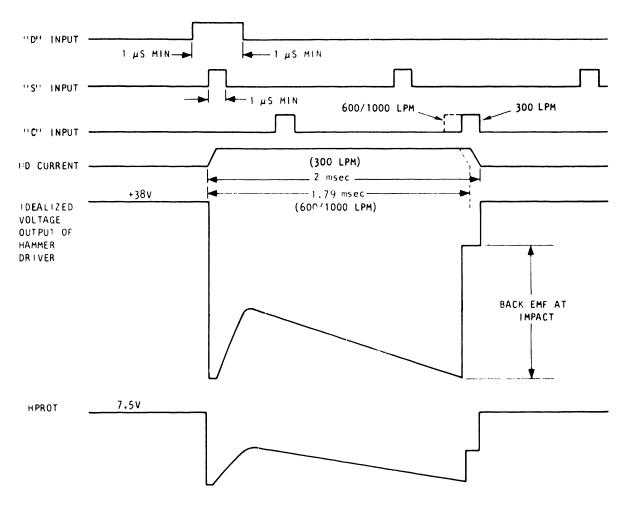

| 2-45                  | Hammer Driver CCA Block Diagram                        |         |

| 2-46                  | Hammer Timing Diagram (Ideal)                          |         |

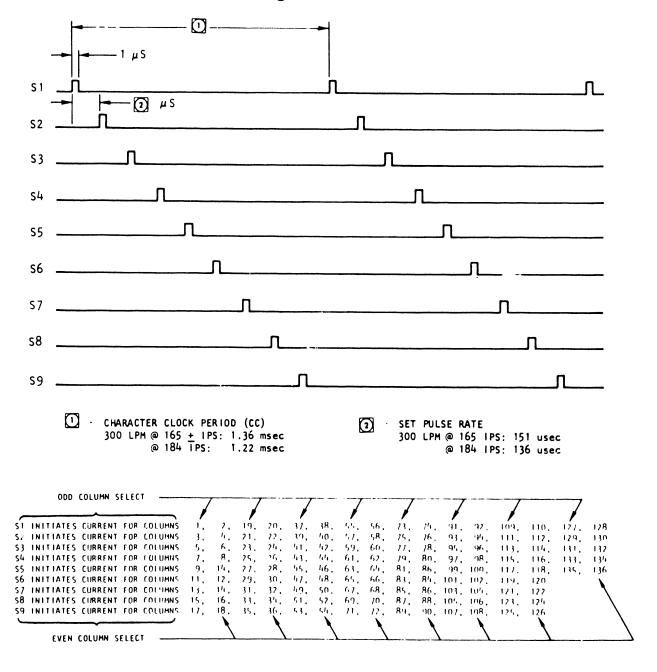

| 2-47                  | 300 LPM Set Pulse Timing Diagram                       |         |

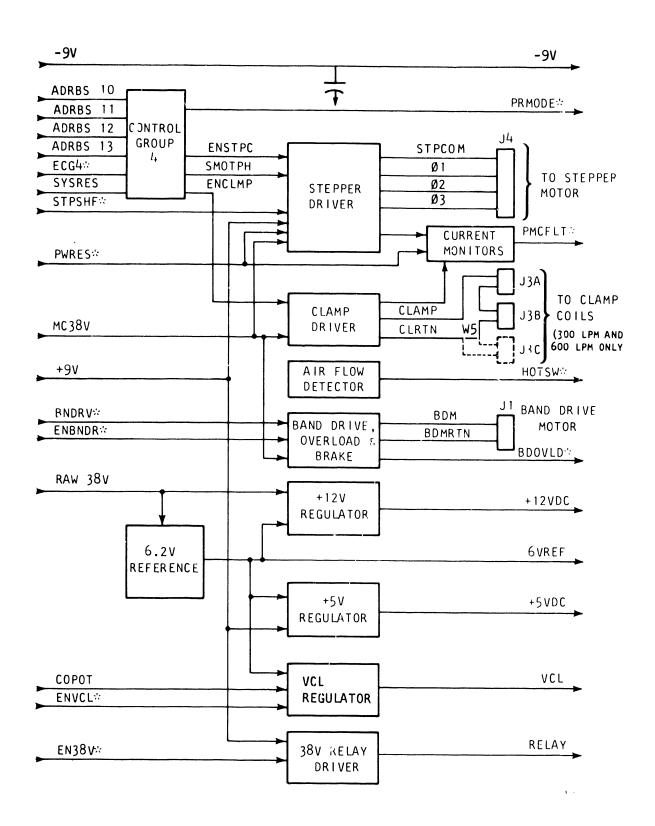

| 2-48                  | Power Board CCA Block Diagram                          |         |

| 2-49                  | 600 LPM/1000 LPM Hammer Firing Sequence                |         |

| 2-50                  | Typical Stepper Motor Timing Diagram                   |         |

| 2-51                  | Character Band/Ribbon Drive Subsystem Block Diagram    |         |

| 2-52                  | Paper Clamp/Paper Feed Subsystem Block Diagram         |         |

| 2-53                  | Paper Clamp/Paper Feed Drive Subsystem Diagram         |         |

| 2-54                  | Print Subsystem Block Diagram                          | 2-153   |

| 2-55                  | 300 LPM Physical Relationship of the Band Column and   | 2-154   |

| 2.57                  | Hammers                                                |         |

| 2-56                  | 300 LPM Print Hardware Analogy                         |         |

| 2-57                  | Hammer Fire Operation                                  | 2-177   |

| 2-58                  | 600 LPM and 1000 LPM Physical Relationship of the Band | 2-161   |

| 2-59                  | Column and Hammer                                      |         |

| 2-39                  | Power Subsystem Block Diagram                          |         |

| 2-60                  | 600 LPM and 1000 LPM Print Analog                      |         |

| 2-61<br>2-62          | 115 VAC, 60 Hz Power Supply Block Diagram              |         |

| 2-62                  | Universal Power Supply Block Diagram                   |         |

| 2-63<br>2-64          | +38V Regulator Block Diagram                           |         |

|                       | Program Overview                                       |         |

| 2-65<br>2-66          |                                                        |         |

| 2-66<br>2-67          | 24-Bit Processor CCA Initialization Routine            |         |

| 2-67<br>2-68          | 24-Bit Processor Start Motor Routine                   |         |

| 2-68<br>2-69          | 20-Bit and 24-Bit Processor Idle Routine               |         |

| 2-69<br>2-70          | 20-Bit Processor Load Data Routine                     |         |

| 2-70                  | 24-Bit Processor Load Data Routine                     |         |

| 2-71                  | Self Test Routine                                      |         |

| 2-72<br>2-73          | Edit Routine                                           |         |

| 2-73<br>2-74          | 300 LPM Print Routine                                  |         |

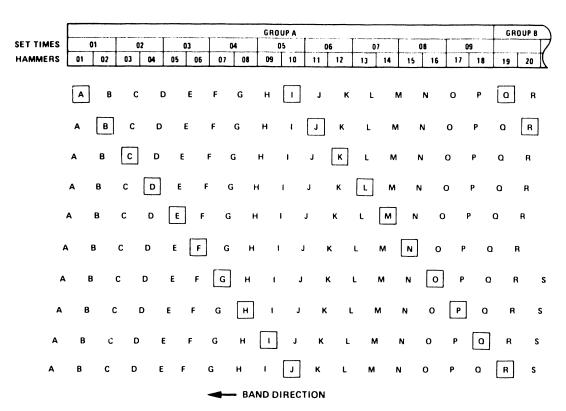

| 2-74<br>2-75          | 300 LPM Hammer Groups                                  |         |

| 2-75<br>2-76          | 600 LPM and 1000 LPM Print Routine                     |         |

| 2-76<br>2 <b>-</b> 77 | Format and Move Paper Routine                          |         |

| 2-77<br>2-78          | System Status Check Routine                            |         |

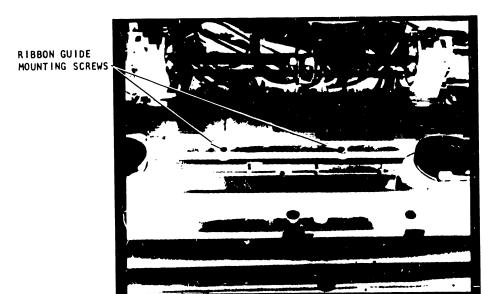

| 3-1                   | Paper Clamp Armature Assembly with Screw-Mounted       | . 2-210 |

| J-1                   | Ribbon Guide                                           | . 3-3   |

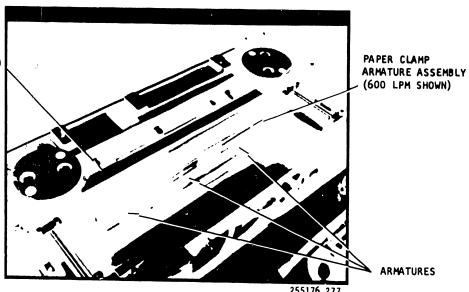

| 3-2                   | Paper Clamp Armature Assembly                          | . 3-4   |

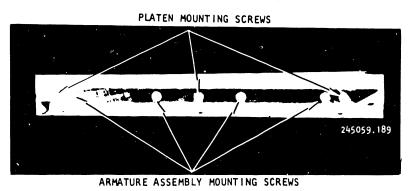

| 3-3                   | Armature Assembly Mounting Hardware                    |         |

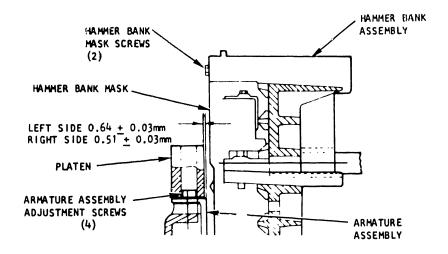

| 3-4                   | Paper Clamp Armature Assembly Adjustment               |         |

| 3-5                   | Paper Clamp Armature Assembly Adjustment Check         |         |

| 3-6                   | Platen Assembly Adjustment                             |         |

| 3-7                   | AC POWER Switch Removal/Replacement                    | . 3-10  |

| 3-8                   | Acoustic Cabinet AC Power Cord and Power Distribution  | . 3-11  |

| 3-9                   | Control Panel Assembly Location                        | . 3-13  |

### LIST OF ILLUSTRATIONS (Cont'd)

| Figure                                                                                                                                  | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 3-10<br>3-11<br>3-12                                                                                                                    | Control Panel Assembly Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-14<br>3-15                                                                                                                        |

| 3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20<br>3-21<br>3-22<br>3-23<br>3-24<br>3-25<br>3-26<br>3-27<br>3-28<br>3-29    | Replacement Hammer Bank Assembly Removal/Replacement Hammer Bank Removal/Replacement Hammer Bank Actuator Assembly Position Interlock Transition CCA I/O Harness Assembly, Printers in Standard Cabinet I/O Harness Assembly, Printers in Acoustic Cabinet Mother Board CCA 300 LPM Paper Clamp Armature Assembly Paper Clamp Armature Assembly (Thick Platen) 600 LPM Paper Clamp Armature Assembly 300 LPM Paper Clamp Solenoid Assembly 600 LPM Paper Clamp Solenoid Assembly Removal/ Replacement Paper Entrance Cover Assembly 600 LPM and 1000 LPM Paper Low Switch Paper Motion Sensor Removal/Replacement Platen Platen without Screw-Mounted Ribbon Guide                                                                                                                        | 3-17<br>3-19<br>3-20<br>3-21<br>3-22<br>3-24<br>3-26<br>3-30<br>3-31<br>3-33<br>3-34<br>3-35<br>3-36<br>3-38<br>3-39                |

|                                                                                                                                         | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                     |

| <u>Table</u>                                                                                                                            | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                |

| 1-1<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5A<br>2-5B<br>2-5C<br>2-5D<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11A<br>2-11B<br>2-11C<br>2-11D | Electronics Assembly, Standard Circuit Card Complement Short Line and Long Line I/O Connector Pin Assignments Centronics-Compatible I/O Connector Pin Assignments Serial I/O Connector Pin Assignments Serial to Parallel Interfacing Signals Configuration Switch S1 Settings Configuration Switch S2 Settings Configuration Switch S3 Settings Configuration Switch S4 Settings Interface Device Enable Decoder Signals Control Group 0 Decode and Functions Control Group 3 Decode and Functions Control Group 5 Decode and Functions Control Group 6 Decode and Functions Centronics-Compatible Interface Switch S1 Settings Centronics-Compatible Interface Switch S2 Settings Centronics-Compatible Interface Switch S3 Settings Centronics-Compatible Interface Switch S4 Settings | 1-19<br>2-5<br>2-10<br>2-12<br>2-13<br>2-23<br>2-24<br>2-25<br>2-26<br>2-28<br>2-30<br>2-31<br>2-31<br>2-37<br>2-39<br>2-40<br>2-41 |

### LIST OF TABLES (Cont'd)

| <u>Table</u> | <u>Title</u>                                              | <u>Page</u>  |

|--------------|-----------------------------------------------------------|--------------|

| 2-12         | Control Group 0 Decode and Functions                      | 2-42         |

| 2-13         | Control Group 2 Decode and Functions                      | 2-43         |

| 2-14         | Control Group 3 Decode and Functions                      | 2-43         |

| 2-15         | Control Group 5 Decode and Functions                      | 2-44         |

| 2-16         | Control Group 6 Decode and Functions                      | 2-45         |

| 2-17         | Centronics-Compatible Printer Control Codes               | 2-47         |

| 2-18         | Centronics-Compatible Status Code Displays                | 2-50         |

| 2-19A        | Serial Interface CCA Configuration Switch Settings        | 2-54         |

| 2-19B        | Serial Interface CCA Protocol Configuration Switch        |              |

|              | Settings                                                  | ` 2-56       |

| 2-19C        | Serial Interface CCA Baud Rate Configuration Switch       |              |

|              | Settings                                                  | 2-57         |

| 2-20         | Short Line Interface CCA Switch Settings for Use with the | 0.50         |

|              | Serial Interface without VFU                              | 2-58         |

| 2-21         | Centronics-Compatible Interface CCA Switch Settings for   | 2.50         |

|              | Use with the Serial Interface with VFU                    | 2-59         |

| 2-22         | Device Enabling and Addressing                            | 2-63         |

| 2-23         | Printer Control Codes                                     | 2-65         |

| 2-24         | ALU Function Control                                      | 2-76         |

| 2-25         | Register Enable Control                                   | 2-77<br>2-83 |

| 2-26         | Device Enable Control                                     | 2-83<br>2-84 |

| 2-27         | Device Load Control                                       | 2-84<br>2-84 |

| 2-28         | Conditional Address Inputs                                | 2-84         |

| 2-29         | Microsequencer Control                                    | 2-87         |

| 2-30         | Function Control Group                                    | 2-93         |

| 2-31         | Control Group 1 Decode Function                           | 2-93         |

| 2-32         | Control Group 7 Decode Function                           | 2-99         |

| 2-33         | Switch Configuration for Band Time Out                    | 2-106        |

| 2-34         | RGBUS Enable Control                                      | 2-107        |

| 2-35<br>2-36 | INBUS Enable Control                                      | 2-108        |

| 2-36<br>2-37 | Load to Control                                           | 2-108        |

| 2-37<br>2-38 | Conditional Input Instructions                            | 2-109        |

| 2-39         | Microsequencer Control                                    | 2-111        |

| 2-40         | Function Control Groups                                   | 2-112        |

| 2-40         | Control Group 1 Decode and Functions                      | 2-113        |

| 2-41         | Control Group 7 Decode and Functions                      | 2-114        |

| 2-43         | Data RAM Page Selection                                   | 2-116        |

| 2-44         | Optional Switch Configuration for Band Time-Out           | 2-118        |

| 2-45         | Timing and Status CCA Timing Characteristics              | 2-121        |

| 2-46         | Print Column Selection Decode                             | 2-126        |

| 2-47         | Fault and Status Enable                                   | 2-127        |

| 2-48         | Unconditional Fault Signal Level                          | 2-128        |

| 2-49         | Control Group 4 Decode and Functions                      | 2-143        |

| 2-50         | Input Voltage and Frequency Configurations                | 2-167        |

| 2-51         | Reduced Print Speed Data Load                             | 2-193        |

| 3-1          | Recommended Tools and Equipment                           | 3-1          |

| 3-2          | Adjustment Procedures                                     | 3-2          |

| 3_3          | Removal/Replacement Procedures                            | 3-8          |

# SECTION GENERAL DESCRIP-TION

### SECTION I

### GENERAL DESCRIPTION

### 1.1 INTRODUCTION

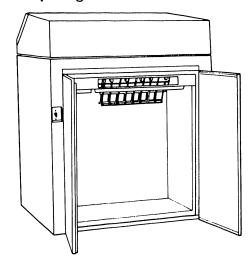

The B-Series Band Printers, manufactured by Dataproducts Corporation in Woodland Hills, California, are medium speed, impact-type, solid font line printers that utilize a continuous character band. The Master Support and Logistics Manual describes the three printers (300 LPM, 600 LPM, and 1000 LPM) presently available in this series. See figures 1-1 through 1-3 for photographs of the three printers available.

### 1.1.1 Master Support and Logistics Manual Contents and Format

Designed primarily for use by personnel at central depot-level facilities, the Master Support and Logistics Manual provides descriptive and operational information in greater depth and detail than the Operator's Guide and Maintenance Guide currently shipped with a majority of the printers. It is divided into two (2) volumes with a comprehensive alphabetical index in volume II. Volume I consists of the following sections:

Section I - General Description

Section II - Theory of Operation

Section III - Maintenance

Alphabetical Index

Volume II includes the following sections:

Section IV - Troubleshooting

Section V - Logic Diagrams

Section VI - Illustrated Parts Lists

Alphabetical Index

### 1.1.2 Section Contents

This section provides general background information on printer design, purpose and operation. The operation of major assemblies and subassemblies are discussed and available options and accessories are described.

### 1.2 PRINTER DESIGN

The B-Series printers are compact, horizontal font, 132 column impact printers designed to provide a minimum throughput of 285 lines per minute for the 300 LPM model, 650 for the 600 LPM model, and 1000 for the 1000 LPM model when using a standard 64-character ASCII set. The operator-changeable font carrier (hereafter referred to as the character band) consists of a continuous steel band

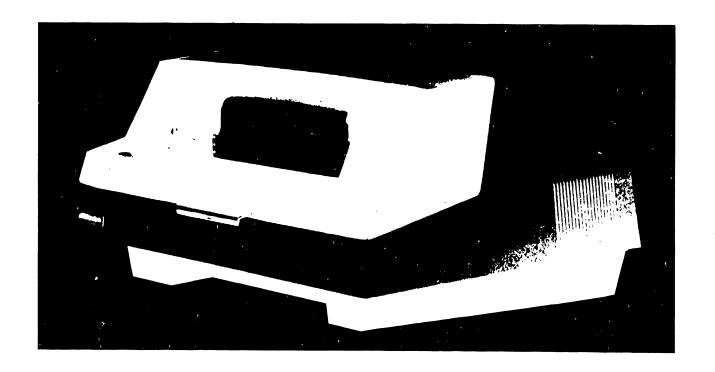

Figure 1-1. 300 LPM Printer

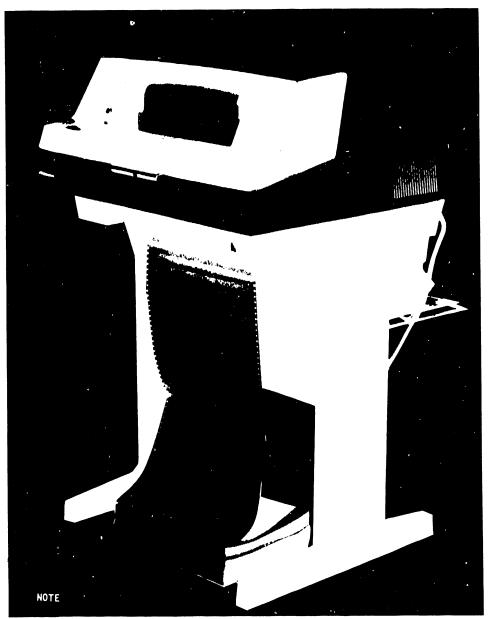

THE PEDESTAL IS AN OPTIONAL ACCESSORY FOR THE 300 LPM PRINTER. THE STANDARD 600 LPM PRINTER IS SHIPPED WITH THE PEDESTAL, BUT MAY BE TABLE-MOUNTED.

Figure 1-2. 600 LPM Printer with Pedestal (Front View)

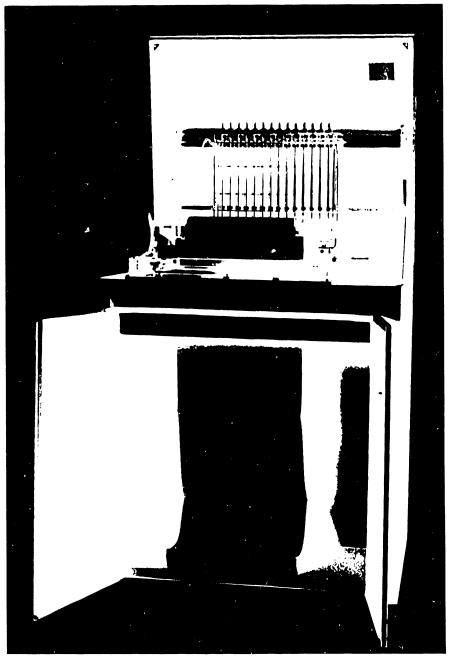

NOTE: AS AN OPTION, THE 300 LPM AND 600 LPM MAY BE ORDERED MOUNTED IN THE ACOUSTIC CABINET.

Figure 1-3. 1000 LPM Printer with Acoustic Cabinet

containing 208 characters for the 300 LPM and 416 characters for the 600 LPM and 1000 LPM printers. A variety of options and accessories are available to efficiently configure the printers to meet specific application requirements.

### 1.2.1 Purpose

The B-Series printers are general purpose output devices for use on electronic information-processing systems, such as small business applications, data communications/data entry terminals, and dedicated minicomputer based systems, where reliable operation in a heavy duty cycle environment is needed. The built-in self test and diagnostic display are designed to maximize the operator's capacity to maintain the printer and to reduce field maintenance expense.

### 1.2.2 Organization

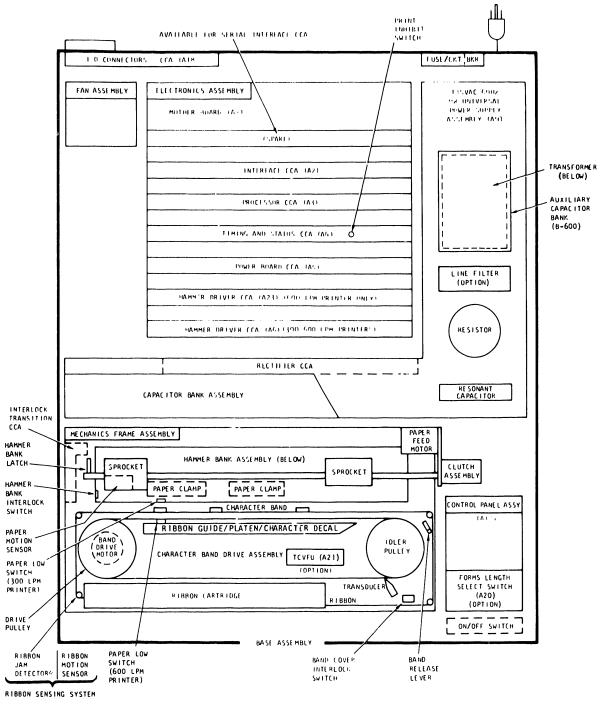

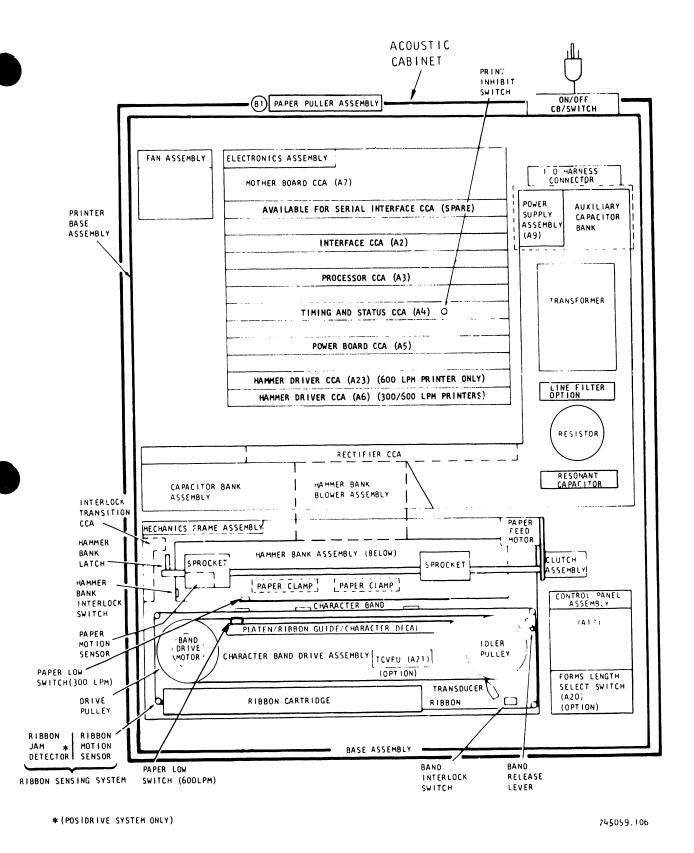

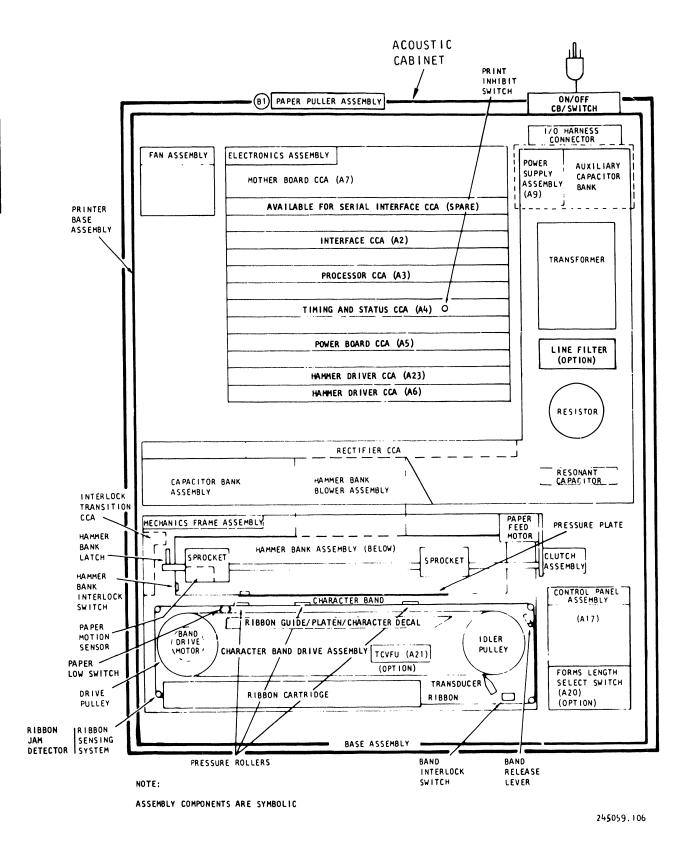

The basic printer consists of seven (7) major assemblies and their related subassemblies. Each of the major assemblies is fully described in paragraph 1.3. Figures 1-4 through 1-6 provide assembly block diagrams for the 300 LPM and 600 LPM printers without the acoustic cabinet, the 300 LPM and 600 LPM printers with the acoustic cabinet, and the 1000 LPM printer which is available only with the acoustic cabinet.

### 1.2.3 System Overview

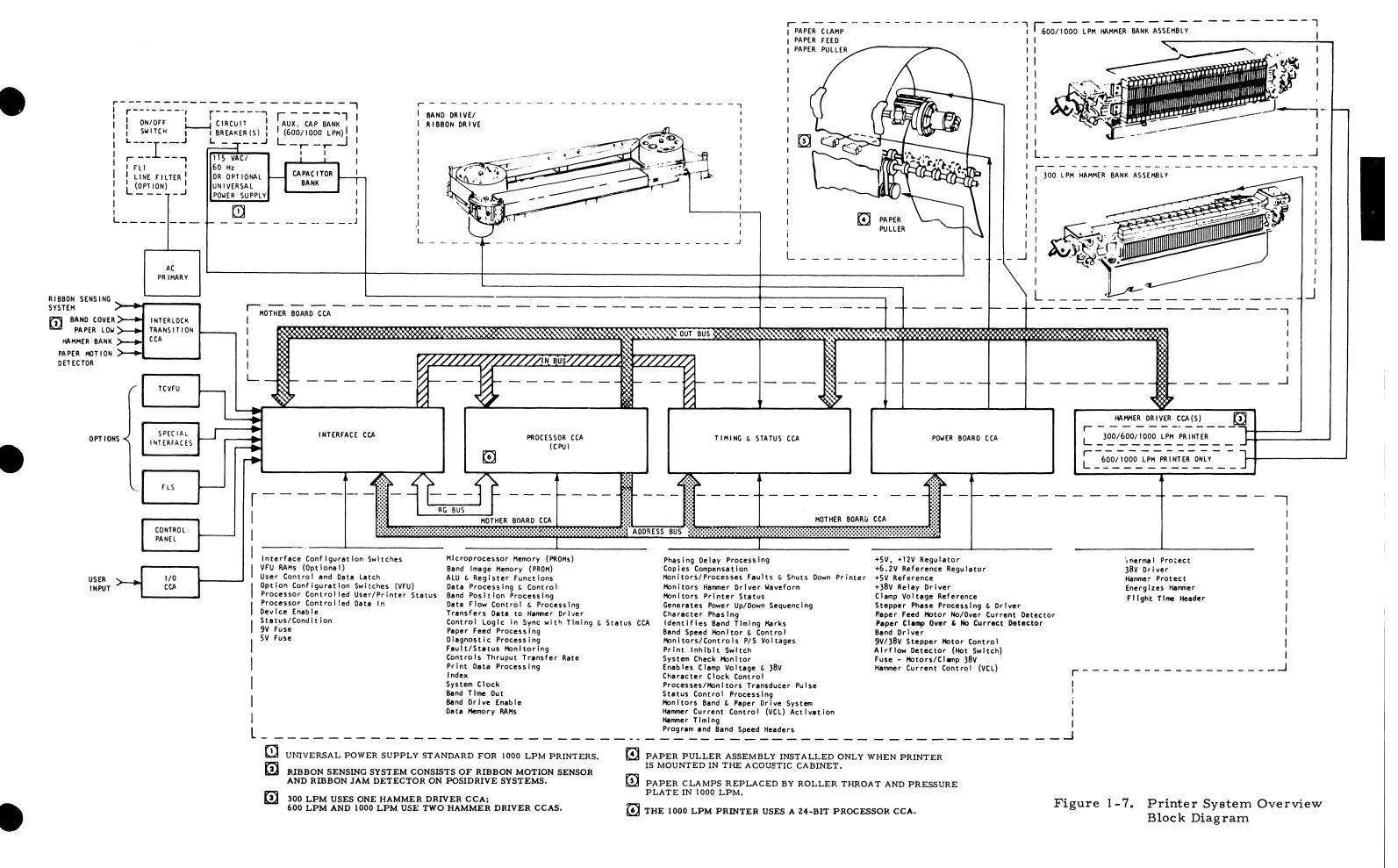

The printer system, comprised of the assemblies described in paragraph 3.1, accepts user data, processes the data for a line of print, prints the data and moves paper according to a programmed format. A dedicated microprocessor contained on the Processor CCA controls the logical, electrical and mechalical functions of the printer and provides diagnostic testing to detect and indicate malfunctions. Figure 1-7 furnishes an overview of the printer system in block diagram format.

Communication between the user system and the standard printer depends on an interlocked "handshaking" arrangement. After the printer has been powered up, is ready, and is placed on line, it informs the user that it is on line and ready to receive data, which it subsequently demands by raising the demand transmission line. The user system acknowledges the demand by transmitting a data or control character and a strobe or timing signal that dictates when the character should be accepted.

The printer responds to the user input by dropping its demand and accepting the data or control character. After accepting the user input, the printer loads it into memory and repeats its demand for data.

This handshaking process continues until the user transmits a control character which defines the previous data as a line of print. The printer then terminates its interfacing with the user system and proceeds to perform a series of programmed routines which will produce a line of print. These routines include Idle, Load, Edit, Print, Format, and Move Paper. A System Status Check routine periodically monitors the printer's condition in order to report any status change or fault which might interfere with printer operation. Detailed explanations of the program routines can be found in paragraph 2.6.

# (POSIDRIVE SYSTEMS ONLY)

245059 106

Figure 1-4. 300/600' LPM Printer without Accustic Cabinet

Major Assemblies and Subassemblies Block Diagram

Figure 1-5. 300/600 LPM Printer with Acoustic Cabinet

Major Assemblies and Subassemblies Block Diagram

Figure 1-6. 1000 LPM Printer Major Assemblies and Subassemblies Block Diagram

### 1.3 ASSEMBLY DESCRIPTION

The assemblies described in the following paragraphs are the major functional components of the printer system. Illustrations and parts lists are provided in section VI of volume II.

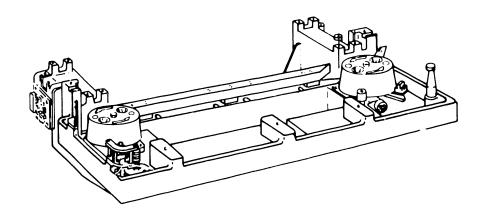

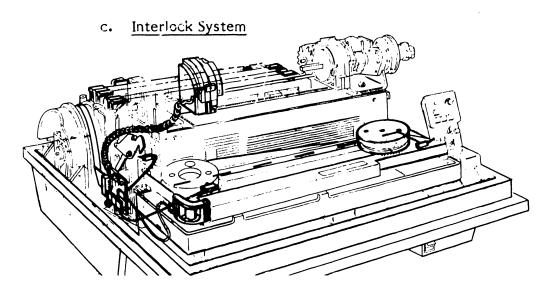

### 1.3.1 Mechanics Frame Assembly

The Mechanics Frame Assembly includes the Character Band/Ribbon Drive Assemblies, the Platen and the Interlock System Circuit Card Assembly, which are engaged in the mechanical tasks of moving the character band, moving the ribbon, sensing the character position, and monitoring the interlock system switches and sensors. At the present time, one of two (2) alternate Mechanic Frame Assemblies are used in 300 LPM and 600 LPM model printers. The differences between the two are most obvious in the type of character band/ribbon drive assembly installed. Each assembly is described below.

### a. Character Band/Ribbon Drive Assemblies

The character band and ribbon drive components form a single subassembly with the ribbon cartridge acting as a slave to the character band drive. Movement of the ribbon is achieved with a capstan roller coupled to the band drive motor shaft. At the present time, two types of character band/ribbon drive systems may be installed in the printers. Their differences are noted in the descriptions which follow; the function of the two systems is identical.

1. Character Band Drive System- The character band drive system consists of a DC motor, a drive pulley, an idler pulley, two edge guide bearings, a character band, and a protective band cover. The DC motor is coupled directly to the drive pulley and causes the band to rotate in a counterclockwise direction at a constant velocity. The character band is mounted over the tapered drive and idler pulleys and is biased downward to ride lightly on the edge guide bearings.

The major differences between the two band drive assemblies currently installed in the B-Series printers are in the mounting of the band drive motor, the band drive motor itself, and in the construction of the drive and idler pulleys. In one, the band drive motor is fixed in the Mechanics Frame Assembly, and the band drive and idler pulleys are of solid two piece construction. This system is referred to as the O-Ring assemblies system.

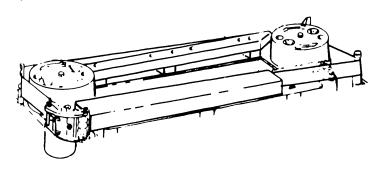

In the other band drive assembly, the band drive motor and idler yoke are trunnion-mounted, and the drive and idler pulleys are solid, single piece units. This system is referred to as the Posidrive assemblies system and is installed in all 1000 L.'M model printers and most later model 300 LPM and 600 LPM printers. Figures 1-8 and 1-9 illustrate the alternate band drive assemblies.

The operator-changeable character band is a continuous steel band with raised characters and timing, index and identification marks. Perforations above and between characters provide minimum stress relief and give the top edge a scalloped appearance. An eccentric on the idler pulley allows the operator to release tension on the band for band replacement. The band transducer senses the character band identification, timing and index marks and generates a signal to the Timing and Status CCA during band notion.

2. <u>Ribbon Drive System</u> - The ribbon drive system consists of the ribbon cartridge, drive rollers, ribbon motion sensor, and ribbon guides. The ribbon cartridge contains a continuous loop of ribbon and snaps onto the ribbon cartridge locating buttons on the band drive casting. Ribbon is then fed around the ribbon guides, past the print station, and through the Ribbon Pivot Arm Assembly which contains the ribbon motion sensor and the ribbon rollers.

Ribbon drive is achieved by the belt-coupling of the ribbon capstan roller to the band drive motor shaft. Ribbon drive operates as a slave to the band drive and causes the ribbon to move simultaneously with the band. The driven capstan roller, along with the contra-rotating idler roller, pulls the ribbon past the print station and compresses it in even folds into the ribbon cartridge. A ribbon motion sensor located in the Ribbon Pivot Arm Assembly monitors ribbon motion.

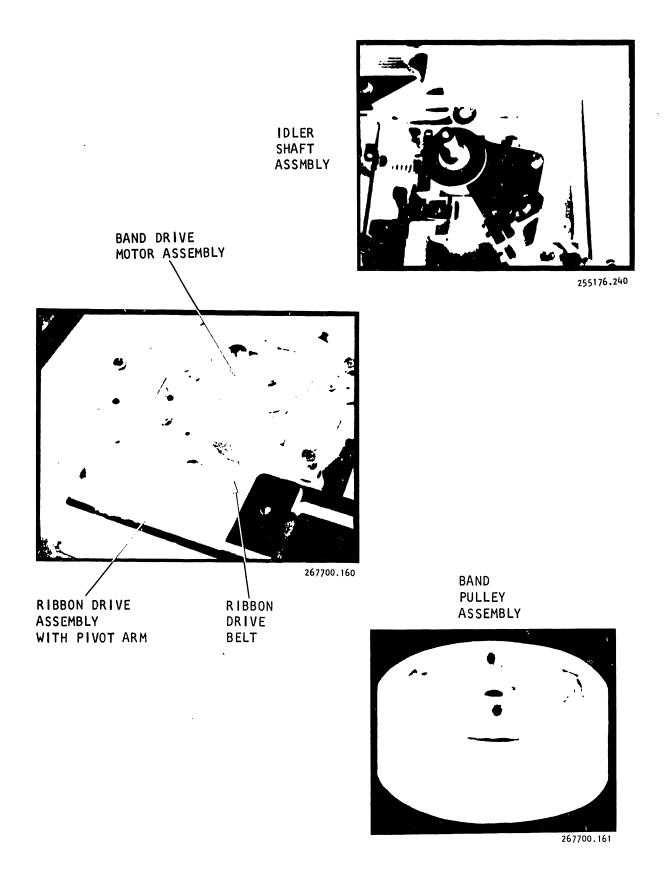

Alternate ribbon drive systems exist for the 300 LPM and 600 LPM model printers. Figures 1-8 and 1-9 illustrate the components of the two systems. The O-ring system uses a clear composition O-ring belt to drive the ribbon capstan roller. The Posidrive system uses a toothed drive belt, a roller arm to provide tension on the drive belt, and a microswitch to detect ribbon jams. All 1000 LPM models and most later model 300 LPM and 600 LPM printers have the Posidrive system installed.

245058.610

BAND DRIVE MOTOR ASSEMBLY

RIBBON DRIVE O-RING

BAND PULLEY ASSEMBLY

Figure 1-8. O-Ring Band Drive/Ribbon Drive Assembly

Figure 1-9. Posidrive Band Drive/Ribbon Drive Assembly

The ribbon consists of a continuous loop of ink-impregnated nylon contained in a cartridge capable of storing the total length of the ribbon except that portion which is passing in front of the print station. The cartridge is held in place by the tension of preformed, snap action, button receptacles molded into the bottom of the cartridge. The button receptacles mate with two metal buttons mounted to the band casting.

The ribbon is guided diagonally across the print station in a path determined by a ribbon guide mounted to the platen and by fixed position guides attached to the printer frame. The ribbon guide and a ribbon mask attached to the platen minimize the possibility of extraneous ink smear on paper forms.

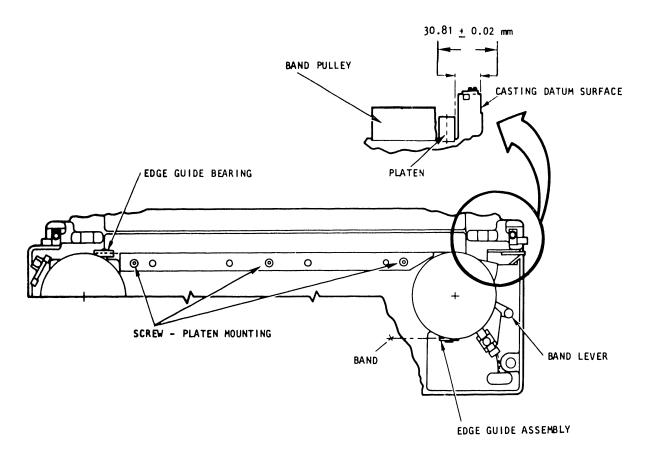

### b. Platen

The platen is a hard, chrome-plated or vespel-lined, machined steel bar precisely set on the band deck casting. It serves as a guide and inpact surface when the hammer strikes against the character band during the printing operation. The position of the platen determines the throat opening for the paper path and provides a base line for setting the hammer flight time. Once adjusted, the platen should not be removed or readjusted except at a properly equipped repair depot.

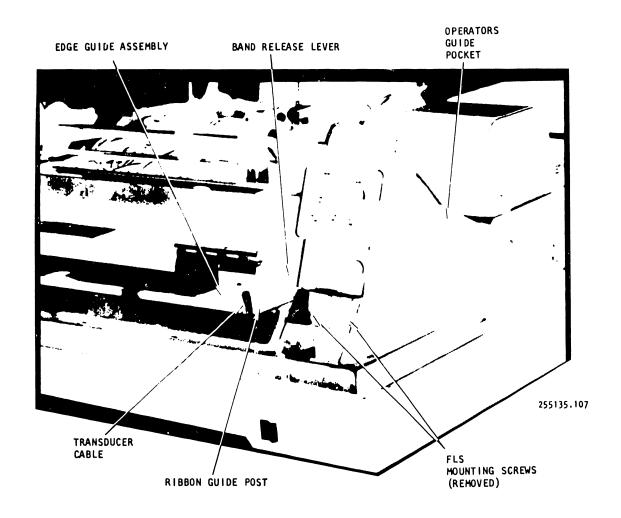

The Interlock System consists of the Interlock Transition CCA, the band cover interlock, the hammer bank interlock, the paper low switch, the paper motion sensor, and the Ribbon Sensing System. The system functions to alert the printer to a number of mechanical faults which will prevent its operation.

The Interlock Transition CCA is mounted on the Mechanics Frame Assembly to the left of the Hammer Bank Assembly. All system switches and sensors are channelled through it to the Interface CCA. The following conditions cause the control panel status indicators to display a fault code for operator interpretation and intervention: an untensioned band, an open band cover or hammer bank, printer out of paper, and lack of ribbon motion or paper motion. The Posidrive system provides an additional microswitch in the Ribbon Sensing System to detect ribbon jam.

### 1.3.2 Paper Feed/Paper Clamp Assemblies

The Paper Feed and Paper Clamp Assemblies are those assemblies concerned with moving and holding the paper forms. All 1000 LPM model printers, and those 300 LPM and 600 LPM models installed in acoustic cabinets, have an additional Paper Puller Assembly to assist in uniformly feeding paper to the rear of the printer. The Paper Feed Assembly is mounted on top of the Hammer Bank Assembly, and the Paper Clamp Assembly is mounted beneath the hammer bank and the platen.

### a. Paper Feed Assembly

The Paper Feed Assembly consists of two (2) pin feed sprockets mounted on a drive shaft and a phase-controlled stepper motor connected to the drive shaft clutch assembly by a toothed timing drive belt. Under microprocessor control, the stepper motor advances paper forms at either single or multiple line rates. When the printer is on line, paper movement is initiated automatically when data line instruction commands, LF, FF, CR, are received by the printer. When the printer is off line, the operator can single step or slew paper by momentarily pressing the control panel PAPER STEP or TOP OF FORM switches.

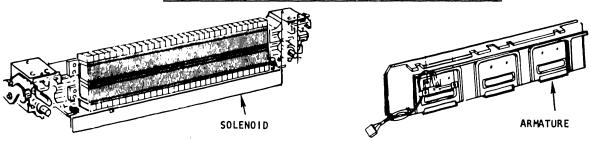

### b. Paper Clamp Assembly/Pressure Roller Assembly

The Paper Clamp Assembly consists of a Solenoid Clamp Assembly mounted beneath the Hammer Bank Assembly and an Armature Clamp Assembly installed beneath the platen. The armature clamps are spring-loaded and positioned to maintain a slight constant tension on the paper within the print station. The clamps are electromagnetically energized by the solenoids during the print routine to prevent blousing of multipart forms and lateral paper movement.

267700.149

The 1000 LPM model printers are equipped with a Pressure Roller Assembly and a pressure plate in place of the armature clamps and solenoids used in the 300 LPM and 600 LPM crinters. The Pressure Roller Assembly is positioned beneath the platen, and under normal conditions, will never need readjustment. The pressure plate is installed beneath the Hammer Bank Assembly and adjusted to provide 500 to 750 grams of pull-through force upon the paper. No electrical current is required by this type of assembly.

Forms are loaded from the bottom of the printer, up through the paper throat (between the platen and the hammer bank mask), and over the two (2) pin feed sprockets on the paper feed drive shaft. A Paper Support Assembly guides the paper to the paper exit at the rear of the printer. The 1000 LPM, and the 300 LPM and 600 LPM printers in acoustic cabinets, are provided with a Paper Puller Assembly. Five (5) individual, easily released rollers are used to vary tension on the paper and to ensure that forms are uniformly fed into the rear cabinet compartment.

A paper motion sensor mounted on the left hand pin feed sprocket detects lack of form motion. The paper low switch, located in the paper throat, detects paper low conditions.

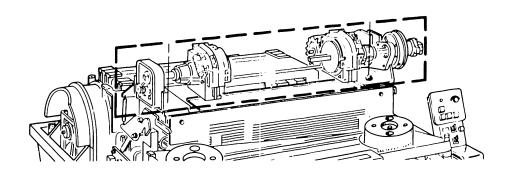

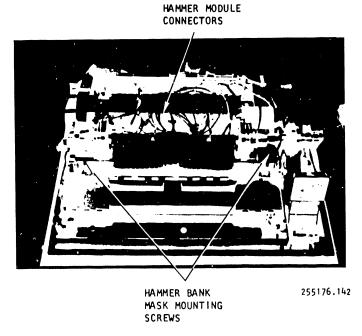

### 1.3.3 Hammer Bank Assembly

The Hammer Bank Assembly, the Hammer Driver CCA(s), the platen, and the character band provide the mechanics for carrying out the print operation. The 300 LPM hammer bank differs from the 600 LPM and 1000 LPM hammer bank; the characteristics of each are described below.

### a. 300 LPM Hammer Bank Assembly

The 300 LPM Hammer Bank Assembly consists of 17 hammer modules interleaved with 17 permanent magnet modules and mounted on a common frame. There are four (4) double column spanning hammers on each of the modules. The hammer coils or flags are positioned in the gaps between the magnets. Upon application of coil current, the hammer is driven out of its slot to impact the paper form upon the ribbon and the character band. The platen serves as a back stop for the band.

Each hammer's flight time (from excitation to impact) is determined by its interacting backstop screw located in the rear of the hammer bank. A single Hammer Driver CCA located in the electronic assembly card cage contains the current drivers for the hammers.

In the standard mode of operation (10 characters per inch), one hammer spans two column positions for a total of 132 columns. In the optional 15 characters per inch, one hammer spans three column positions. An optional 136 column printout is also available.

### b. 600 LPM and 1000 LPM Hammer Bank Assembly

The 600 LPM and 1000 LPM Hammer Bank Assembly consists of an upper and a lower hammer bank. Each bank is made up of 17 hammer modules interleaved with 17 permanent magnet modules. There are four (4) single column spanning hammers on each of the 17 upper and 17 lower modules (34 total). The hammer coils are positioned in the gaps between the magnets. The two banks are fastened together with the hammers aligned horizontally for the odd/even print column registration. The upper bank contains the hammers for the even numbered print columns; the lower bank contains those for the odd numbered print columns.

Two Hammer Driver CCAs, located in the electronic assembly card cage, contain the current drivers for the hammers. Current is carried through the flexure springs of the hammer to its coil where the magnetic field interacts to drive the hammer toward the character band. When the current is removed, the flexure springs return the hammer to a rest position against the adjustable backstop screw which determines the flight time of the hammer.

The 600 LPM and 1000 LPM model printers are equipped only for the standard 10 characters per inch mode of operation. A separate hammer is provided for each print column. The optional 136 column printout is made available by using two (2) Hammer Driver CCAs that contain extra current drivers for the extra columns.

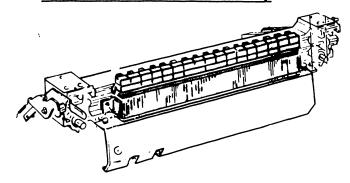

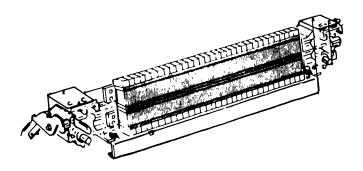

The standard Electronics Assembly (depending upon printer model) consists of five (5) or six (6) circuit card assemblies plugged into a Mother Board CCA and held in place by vertical guides. Ejector keys, attached to each CCA, aid in their removal from the Mother Board CCA connectors.

Circuitry on the circuit card assemblies processes the user data and signals, and generates internal signals to produce band/ribbon drive, paper motion, and hammer firing. Table 1-1 lists the standard card complement for each of the printer models. The detailed operation of the CCAs is discussed in section II.

TABLE 1-1. ELECTRONICS ASSEMBLY, STANDARD CIRCUIT CARD COMPLEMENT

| Circuit Card Assembly                                                                                                                      | Ref. Design.                                 | 300 LPM          | 600 LPM          | 1000 LPM         |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|------------------|------------------|

| Mother Board (300 LPM) Mother Board (600/1000 LPM) Interface 20-Bit Processor 24-Bit Processor Timing and Status Power Board Hammer Driver | A7<br>A7<br>A2<br>A3<br>A3<br>A4<br>A5<br>A6 | X<br>X<br>X<br>X | X<br>X<br>X<br>X | X<br>X<br>X<br>X |

|                                                                                                                                            |                                              | x                | X<br>X           | X<br>X           |

### a. Mother Board CCA

245058A.1003/4

255137.131

The Mother Board CCA functions as a common bus for the transmission of required voltages and signals to and between circuit card assemblies. Two different Mother Board CCAs are used in the B-Series printers. The 300 LPM model circuit card contains six (6) pairs of 60-pin edge card connectors, XA1-XA6, into which the Electronic Assembly circuit cards are plugged. The 600 LPM and 1000 LPM circuit card contains seven (7) pairs of 60-pin edge card connectors, XA1-XA6 and XA23. The XA1 slot is reserved as a spare for use with the optional serial interface and other special customer configurations. A relay to transfer the +38 volts is also mounted on the Mother Board CCA, and connectors are provided for Capacitor Bank Harness Assembly and the optional Elapsed Time Meter Assembly.

### b. Interface CCA

255176.196

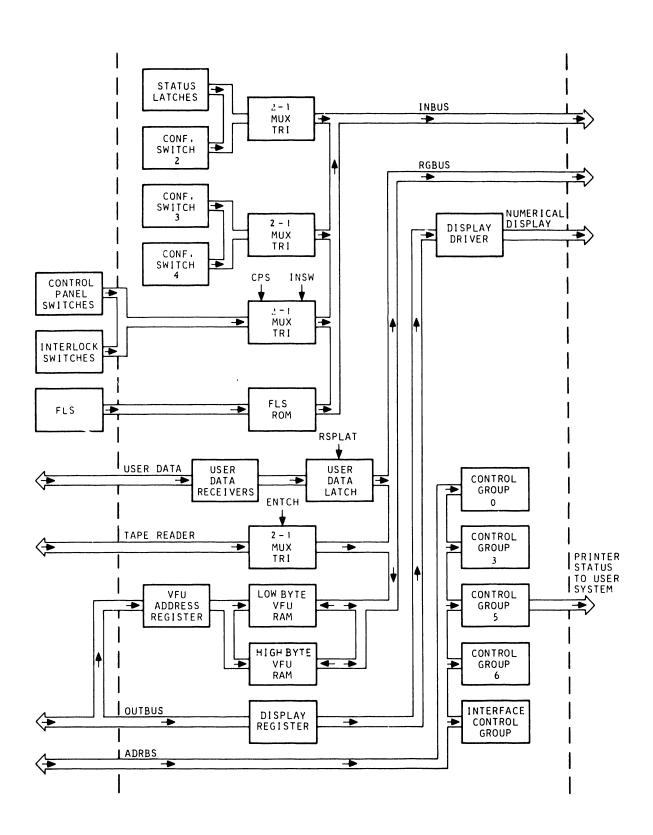

The Interface CCA acts as an input/output buffer to the Processor CCA for the user system, the control panel, the system interlocks, and the optional Forms Length Selector Assembly, Tape Controlled Vertical Format Unit (TCVFU) and the Direct Access Vertical Format Unit (DAVFU). A variety of logic and format options are made available by two (2) configuration switches mounted on the circuit card. Four (4) configuration switches are used when a VFU option is installed.

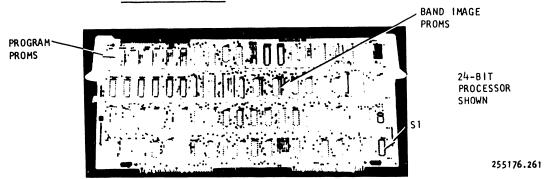

### c. Processor CCA

The Processor CCA functions as the computing center of the printer system and directs the printer to execute its program instructions. PROMs installed on the circuit card house the master program. Five (5) program PROMs are used in the 300 LPM and 600 LPM model printers. The 24-bit Processor CCA, used in the 1000 LPM printer, requires six (6) PROMs and has sockets for six (6) additional PROMs to meet special programming requirements.

Sockets are provided for three (3) additional PROMs which supply band image information. At least one band image PROM must be installed, and its band image code must match the code etched on the character band for the printer to initialize.

In addition, a switch (S1), mounted on the circuit card, provides for variable band time-out. Band time-out is the number of revolutions of the character band which occur between the time printable data is received and the time the band drive system is disabled because no further printable data has been transmitted.

### d. Timing and Status CCA

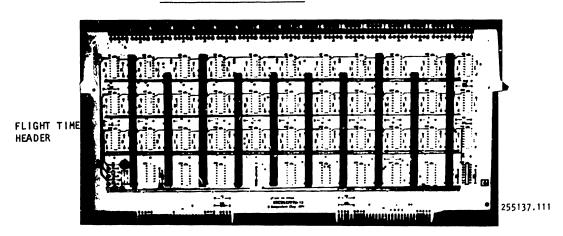

The Timing and Status CCA functions as an intermediary and monitor for the Processor CCA. It notifies the Processor CCA and the Power Board CCA of the presence or loss of power by generating the power up and power down reset sequences of the printer system. As an intermediary between the analog band drive system and the digital control of the Processor CCA, it amplifies and digitizes the transducer (character band sensor) input to provide the time base required to control hammer fire. Band speed is monitored and controlled by the high speed clock of the Processor CCA in conjunction with the band timing clock.

Status changes related to the power supply voltages, the transducer, the band drive, hammer fire, and the paper feed drive are reported to the Processor CCA for interpretation and reaction. The Timing and Status CCA will override all processor controls and automatically shut down the printer system, if monitoring of the airflow, the 5 volts or the system clock indicates a fault condition.

In addition, timing and status circuitry provides for character phasing and copies compensation for optimum print output. Under program direction, correct column spacing control is furnished for the 300 LPM model printers which have double spanning hammers and the 10/15 character per inch option. The circuitry is disabled in 600 LPM and 1000 LPM model printers which use single column spanning hammers. Changeable band speed and program headers, installed on the circuit card, program the printer for 300 LPM, 600 LPM, or 1000 LPM operation.

A print inhibit switch, mounted on the circuit card, can be used to disable the paper faults and the hammer driver(s), and prevent firing of hammers. Since the printer continues to function, the print inhibit mode is useful for most maintenance and troubleshooting procedures.

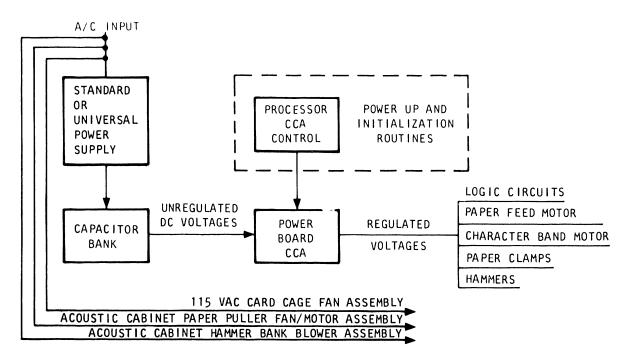

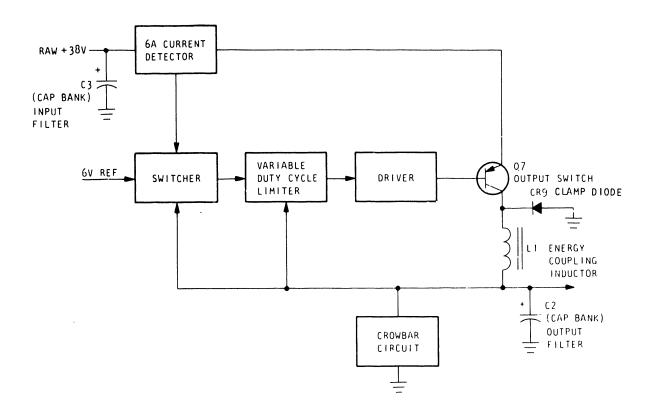

### e. Power Board CCA

255176.197

The Power Board CCA interfaces the Processor CCA to the paper feed drive system and the Timing and Status CCA to the band drive system. It also provides regulated voltages to the printer's analog and digital circuits. By monitoring all voltages, it protects against over-voltage and over-current conditions in the printer system. An air flow monitor senses the presence of moving air within the electronics assembly and signals the Timing and Status CCA when airflow drops below a specified minimum. Regulated voltages are then shut down.

By varying the VCL output in accordance with the control panel copies potentiometer, the current to the hammer drivers, and thus the impact energy of the hammers, is regulated for penetration control.

In 300 LPM and 600 LPM model printers, the two (2) paper clamp solenoid assemblies are plugged into the Power Board CCA. Under program control, the Power Board CCA turns the clamp solenoids on or off as required during the printing and move paper sequences. The 1000 LPM model printer's paper throat assembly requires no electrical connections or control.

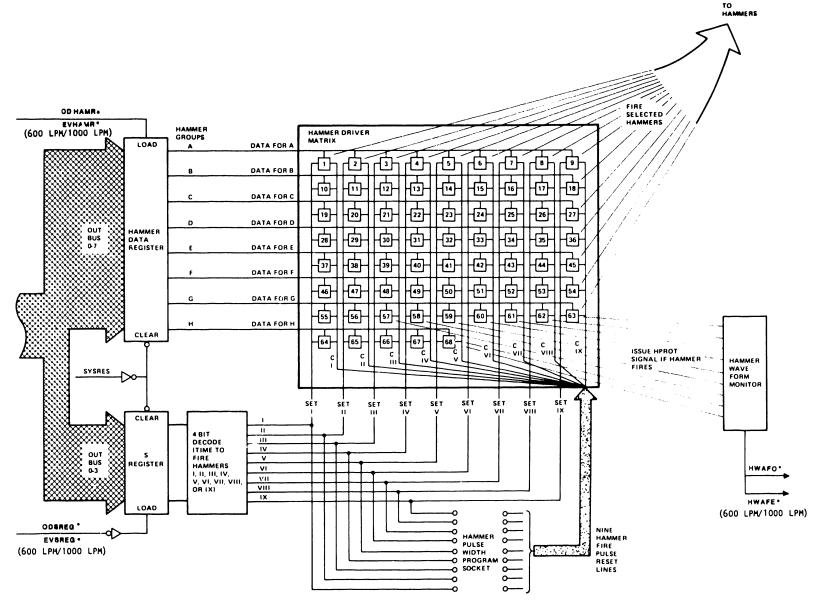

#### f. Hammer Driver CCA

The Hammer Driver CCA is the interface between the Processor CCA and the hammer bank. It contains the circuitry for firing the hammers and detecting hammer misfire. Print data from the Processor CCA is latched and decoded to enable selected hammers to fire. A header, plugged into a socket on the CCA, controls hammer flight time.

The 300 LPM printer has only one (1) Hammer Driver CCA installed in the electronic assembly card cage. The 600 LPM and 1000 LPM printers use two (2) CCAs, one for the upper hammers (A23) and one for the lower hammers (A6). The connectors for the hammer modules are mounted on the top edge of the Hammer Driver CCAs. White and blue module connectors are used to distinguish between upper and lower modules in the 600 LPM and 1000 LPM printers.

#### 1.3.5 Power Supply

The power requirements of the printer system are met by the Power Supply Assembly which provides the following output voltages: Raw +38V, +38V, +9V, -9V, and +9VEW (Early Warning). Overload protection is furnished by the circuit breaker(s) and three (3) fuses mounted on the Rectifier CCA. Two assemblies are currently available for B-Series printers—the standard 115 VAC, 60 Hz or a universal power supply (a 300 LPM and 600 LPM option). Component differences between the two assemblies are detailed in the following paragraphs. Operating descriptions can be found in section II. All 1000 LPM models are equipped with the Universal Power Supply Assembly.

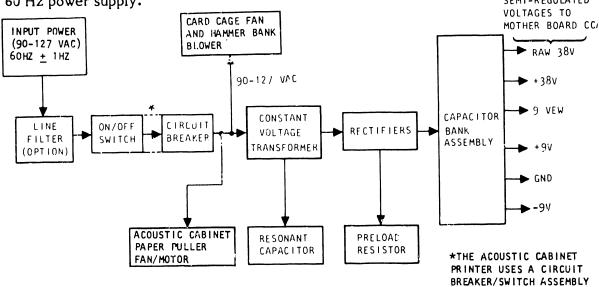

#### a. Standard 115 VAC, 60 Hz Power Supply Assembly

RECTIFIER CCA

267700.164

The Standard 115 VAC, 60 Hz Power Supply Assembly requires an input of 90 to 132 VAC at 60 Hz. The assembly consists of a constant voltage transformer, resonant capacitor, 38 volt preload resistor, AC Power switch, a single circuit breaker, a Rectifier CCA, and a Capacitor Bank Assembly. All 600 LPM models are also equipped with an Auxiliary Capacitor Bank Assembly to handle the additional power requirements of the second Hammer Driver CCA.

When 300 LPM or 600 LPM model printers with the standard power supply are installed in the optional acoustic cabinet, the standard switch and circuit breaker are replaced by a combination switch/circuit breaker mounted in the rear of the cabinet. The Hammer Bank Blower Assembly, utilized in acoustic cabinets, derives its power from the Rectifier CCA. Note that the Paper Puller Assembly motor wiring must be compatible with the 115 VAC, 60 Hz input.

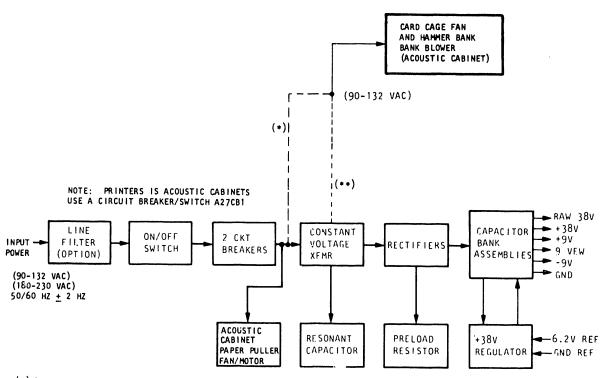

#### b. Universal Power Supply Assembly

RECTIFIER CCA

255137.125

The Universal Power Supply Assembly is designed to operate with inputs of 115 VAC or 230 VAC and 50 Hz or 60 Hz. The assembly consists of a constant voltage transformer, resonant capacitor, 38 volt preload resistor, AC Power Switch, two (2) circuit breakers, a Universal Rectifier CCA with a 38V regulator, and a Capacitor Bank Assembly. All 600 LPM and 1000 LPM models are also equipped with an Auxiliary Capacitor Bank Assembly. The Universal Power Supply Assembly is a standard feature on 1000 LPM printers.

Double sets of plugs and jacks are provided with the universal power supply transformer and Rectifier CCA to accommodate the four (4) combinations of input voltage and frequency. For all printers installed in acoustic cabinets, a reconfiguration of the power supply requires reconfiguration of the Paper Puller Assembly motor wiring to the same voltage and frequency.

When 300 LPM or 600 LPM printers with the universal power supply are installed in the optional acoustic cabinet, the standard switch and circuit breakers are replaced by a combination switch/circuit breaker mounted in the rear of the printer. The cabinet's Hammer Bank Blower Assembly is plugged into the Rectifier CCA.

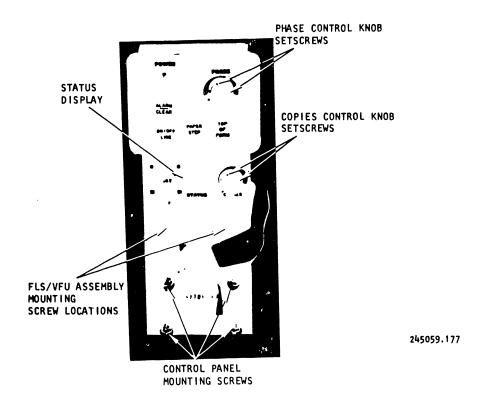

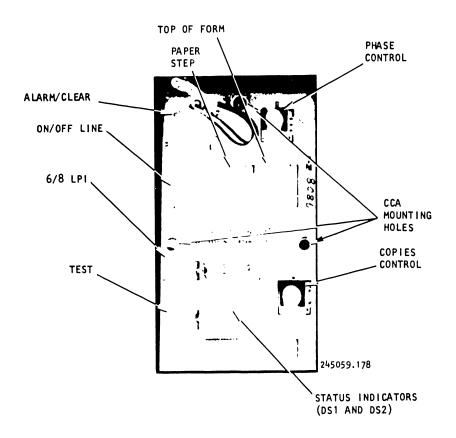

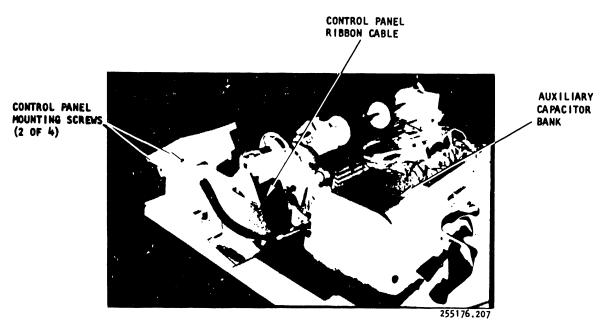

1.3.6 Control Panel Assembly

ACOUSTIC CABINET CONTROL PANEL SHOWN

267700.146

Operator monitoring and control of the printer is aided by the indicators, switches and potentiometers mounted on the Control Panel Assembly. The POWER indicator, ON/OFF LINE switch/indicator, ALARM/CLEAR switch/indicator, PAPER STEP switch, TOP OF FORM switch, and PHASE potentiometer are readily accessible to the operator. By raising the cover door, the COPIES potentiometer, 6/8 LINES switch, TEST (self-test) switch, and STATUS indicators are also accessible. The digital STATUS indicator facilitates diagnosis and identification of problems and malfunctions.

#### 1.3.7 Fan Assemblies

245058A.1003/3

The standard 300 LPM and 600 LPM printers have a single Fan Assembly located in the rear of the printer to provide a constant flow of air over and around the Electronic Assembly card cage and to maintain the operating temperature within a specified range. Failure of the fan to maintain the temperature within the required temperature range will cause an immediate reflex fault that will power down the printer. Power for the Fan Assembly is provided by the AC power source. Printer operation is prevented if the Fan Assembly is not plugged

255176.268

255176.258

All printers installed in an acoustic cabinet have two (2) additional fan assemblies. A Hammer Bank Blower Assembly, positioned over the hammer bank, expels the heat generated by the printing operation. A plenum chamber directs the air flow to the hammer modules. The blower motor is plugged into the Rectifier CCA.

The Paper Puller Assembly motor is cooled by an axial fan attached to the motor assembly. Air is pulled from the cabinet duct and forced over and around the motor to prevent overheating.

#### 1.3.8 Harness Assemblies

STANDARD POWER SUPPLY HARNESS ASSEMBLY SHOWN

255137.133

The printer employs a number of harness and cable assemblies to interconnect the major assemblies, subassemblies and circuit card assemblies. Interconnection diagrams are provided in section V of volume II.

#### 1.4 OPTIONS AND ACCESSORIES

A variety of options and accessories are available to efficiently configure the printer to meet specific application requirements. The following paragraphs briefly describe those options and accessories currently obtainable.

#### 1.4.1 Multiple Band Sensing and Character Sets

A printer is normally provided with one (1) character band and a code-correlated band image PROM. By installing two (2) additional band image PROMs on the Processor CCA, a maximum of three (3) differently configured character bands may be used on the same printer without electronic changes. Note that the character bands and band image PROMs must be matched and that printers cannot be equipped with both USA and UK PROMs.

Standard character bands are available in 48, 64, upper and lower case 96, and 128 character sets. An optional automatic foldover of lower case character codes into appropriate upper case characters may be provided with the 64 character utility band sequence. Consult the appropriate table in section VI of volume II for a descriptive list of the standard character band/PROM sets. Printers configured with the Centronics-Compatible Interface CCA cannot use the 128 character set and do not print the 96th character in the 96 character set. See paragraph 1.4.4, subparagraph b.

A variety of special character and font styles is also available. Unique characters can be designed upon customer request.

#### 1.4.2 Condensed Print

Standard horizontal character spacing for all printer models is ten (10) characters per inch (CPI). The 300 LPM models can be configured to use the condensed print fifteen (15) CPI band/PROM sets. Changing from standard to condensed printing can then be simply a matter of changing the character band when the Multiple Band sensing option is also installed. Since 136 columns are the maximum accepted by the printer, the 15 CPI option reduces the width of the printout.

#### 1.4.3 136 Column Print Capability

A 136 column print capability is available as an option for all standard printer models. Additional circuitry on the Hammer Driver CCA(s) is required to implement the option. This option is <u>not</u> available for 300 LPM and 600 LPM printers configured with either the Centronics-Compatible Interface CCA or the Serial Interface CCA with VFU.

#### 1.4.4 Interface Options

SERIAL INTERFACE

255137.124

In addition to the standard Short Line Interface CCA, optional interface configurations are available to meet special customer requirements. Operation of the most widely used optional interfaces is discussed in section II of this volume.

#### a. Long Line Interface

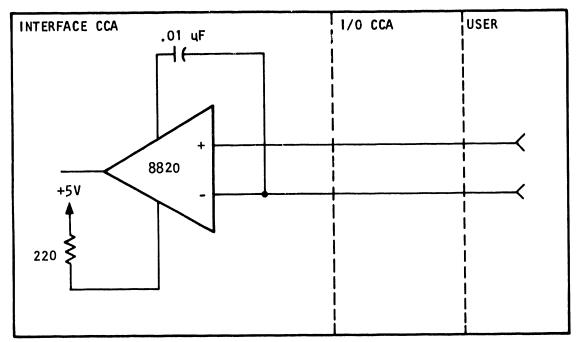

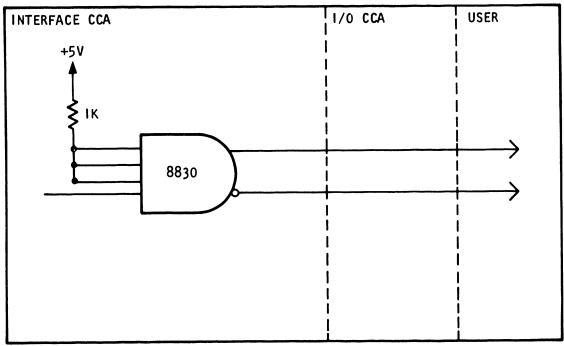

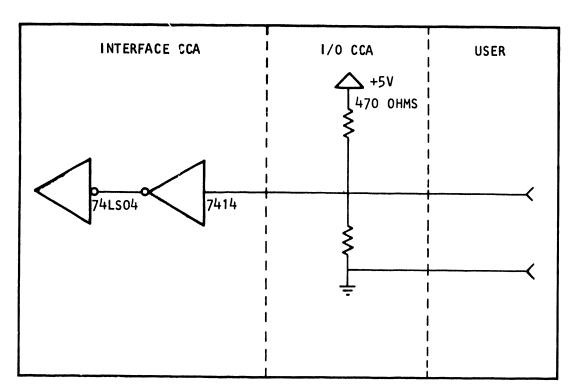

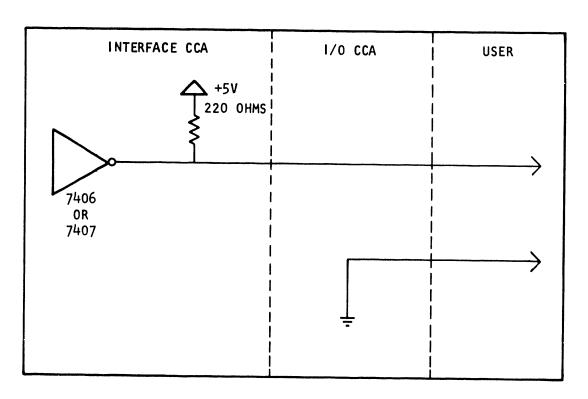

The Long Line Interface allows the interface lines to be extended from the standard 15 meters (49 feet) to 150 meters (492 feet). Integrated circuit differential transmitters and receivers of the DM 8830/8820 class are used. The user must supply similar long line devices at the controller end.

#### b. Centronics-Compatible Interface

The Centronics-Compatible Interface permits operation on most Centronics-Compatible controllers. The VFU option is standard with this interface. In addition, any character set used must be limited to 95 characters maximum; octal 177 is used as a delete code in 300 LPM and 600 LPM models and is switch-selectable in 1000 LPM printers. 300 LPM and 600 LPM printers configured with the Centronics-Compatible Interface CCA cannot support the optional 136 column print capability.

#### c. Serial Interface

The Serial Interface utilizes standard RS232C receivers and drivers, or 20 MA current loops, to receive and transmit data in serial format. The front-ended circuit card assembly is plugged into the spare slot of the Mother Board CCA. The printer can be configured for the VFU option by replacing the standard non-VFU Short Line Interface CCA with the Centronics-Compatible Interface CCA. Since the maximum baud rate available is 19,200, the Serial Interface cannot support the full 1000 lines per minute print rate of the 1000 LPM printer. However, the 300 LPM and 600 LPM printers with the VFU serial configuration cannot support the optional 136 print column.

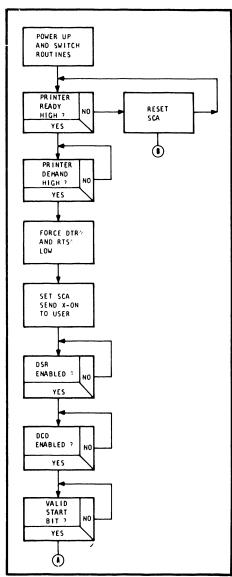

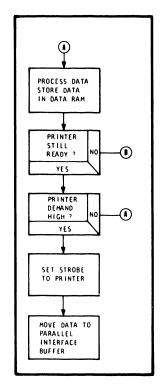

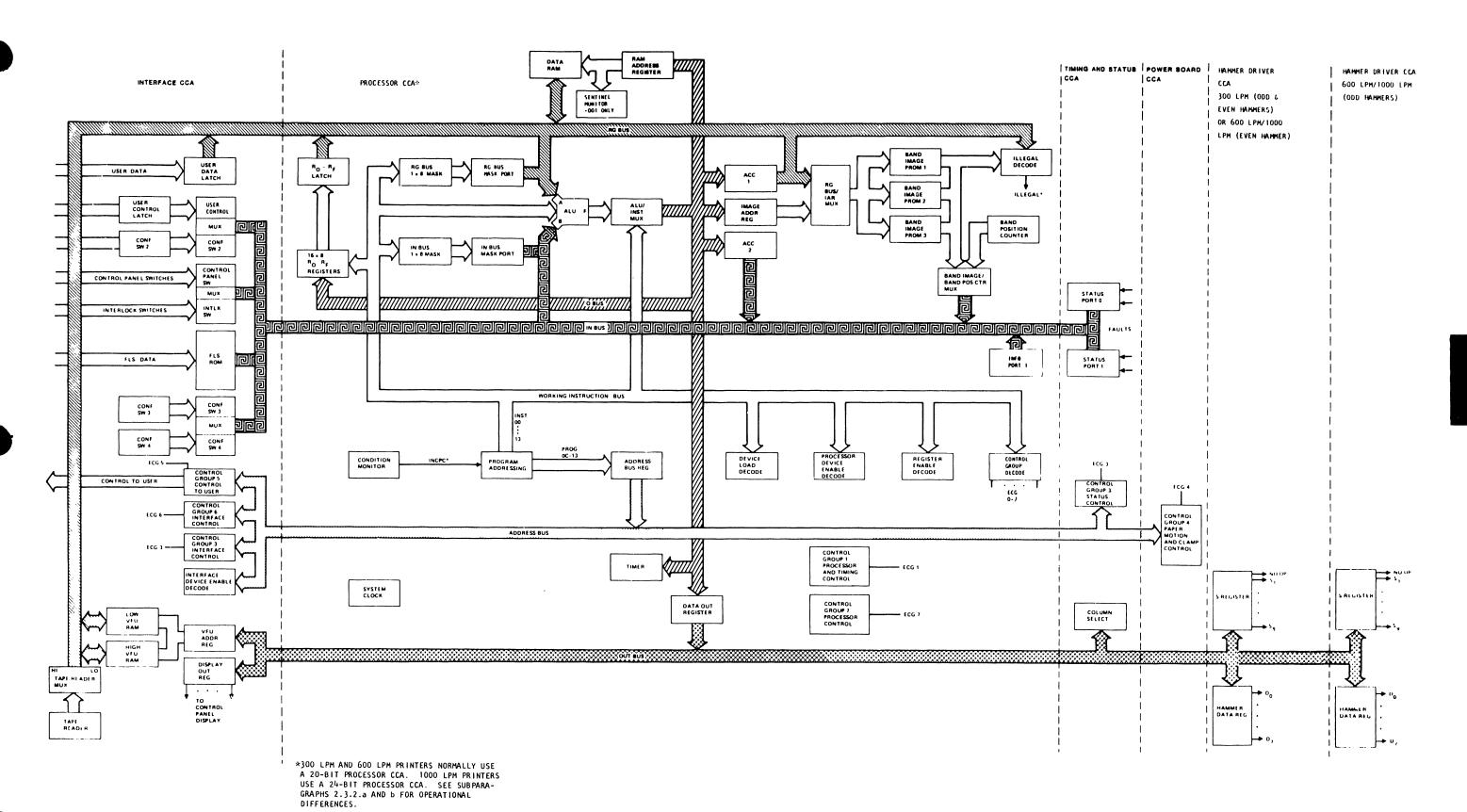

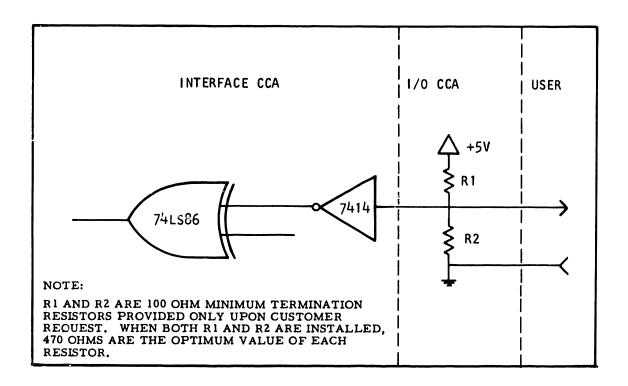

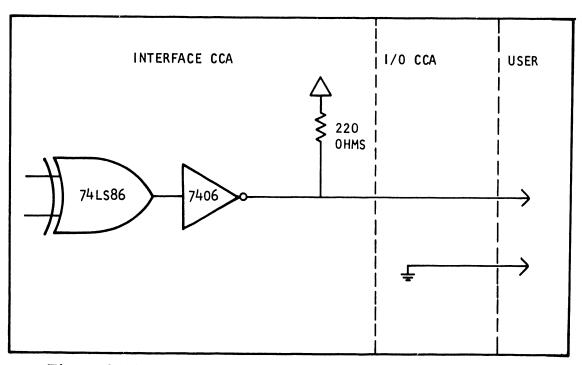

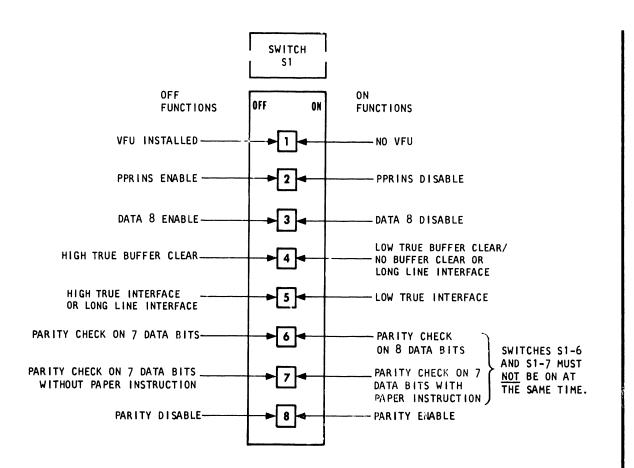

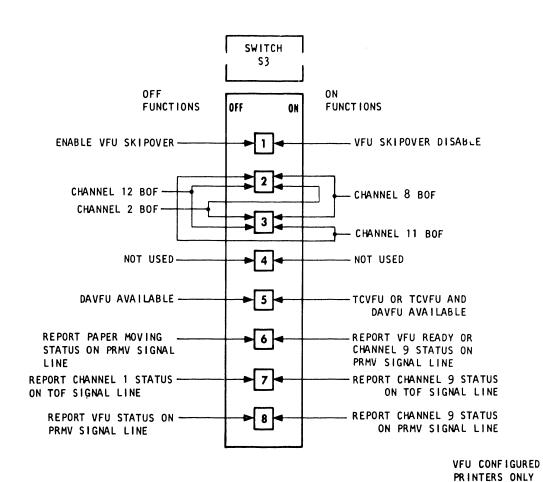

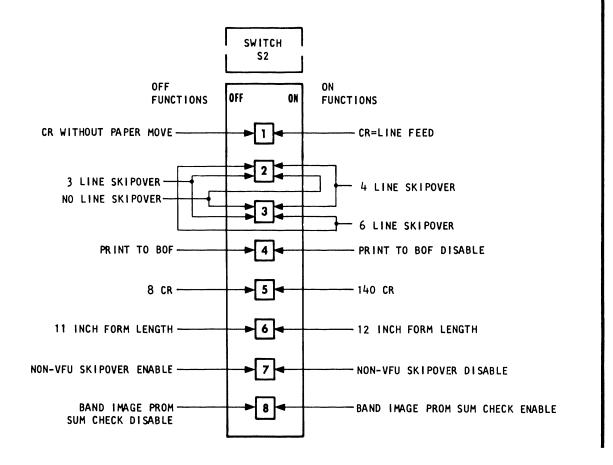

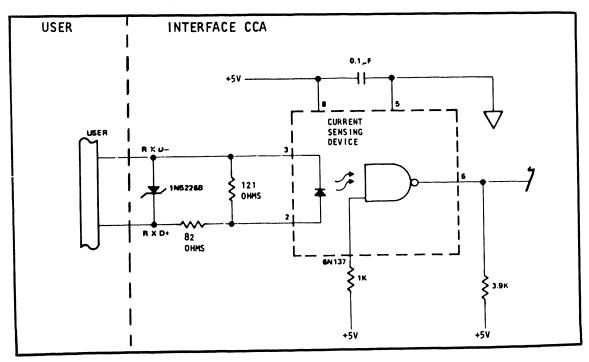

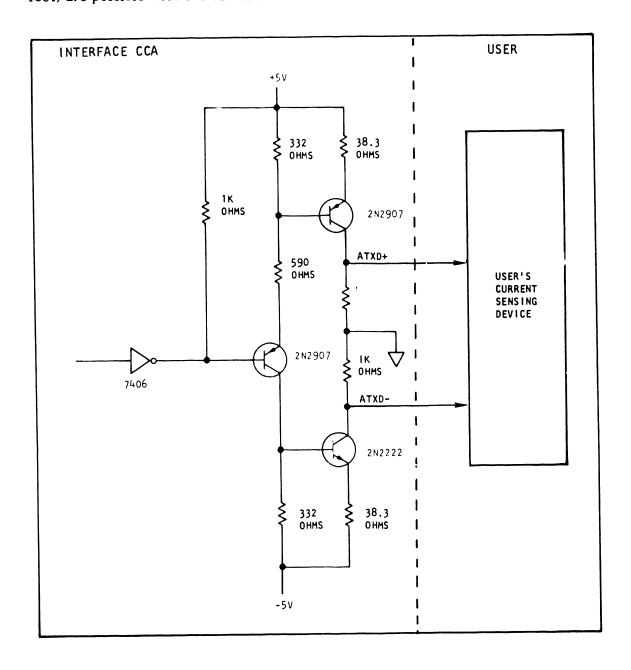

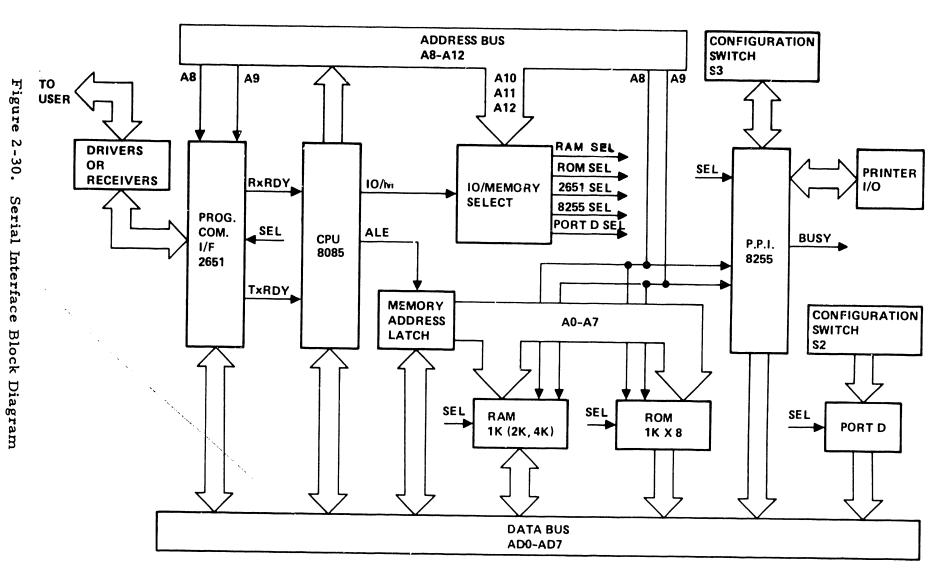

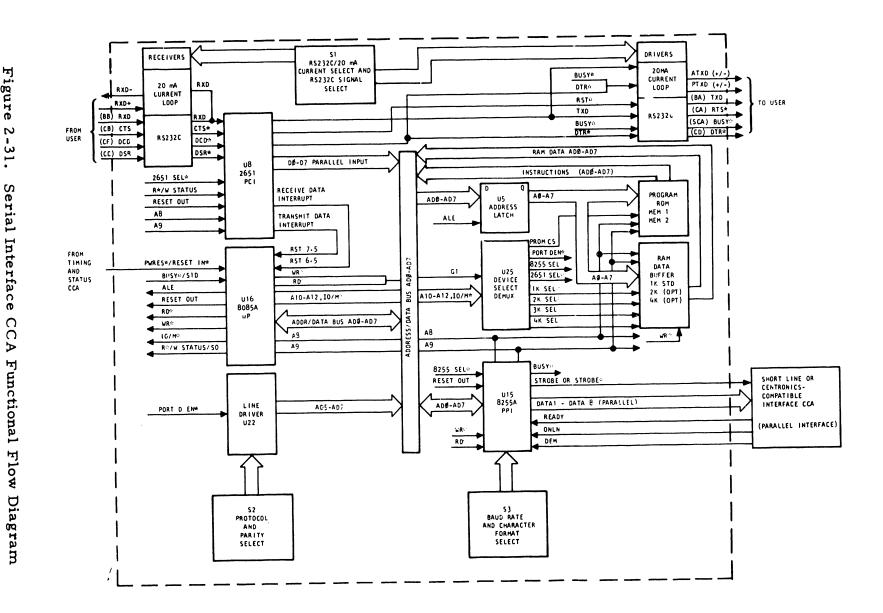

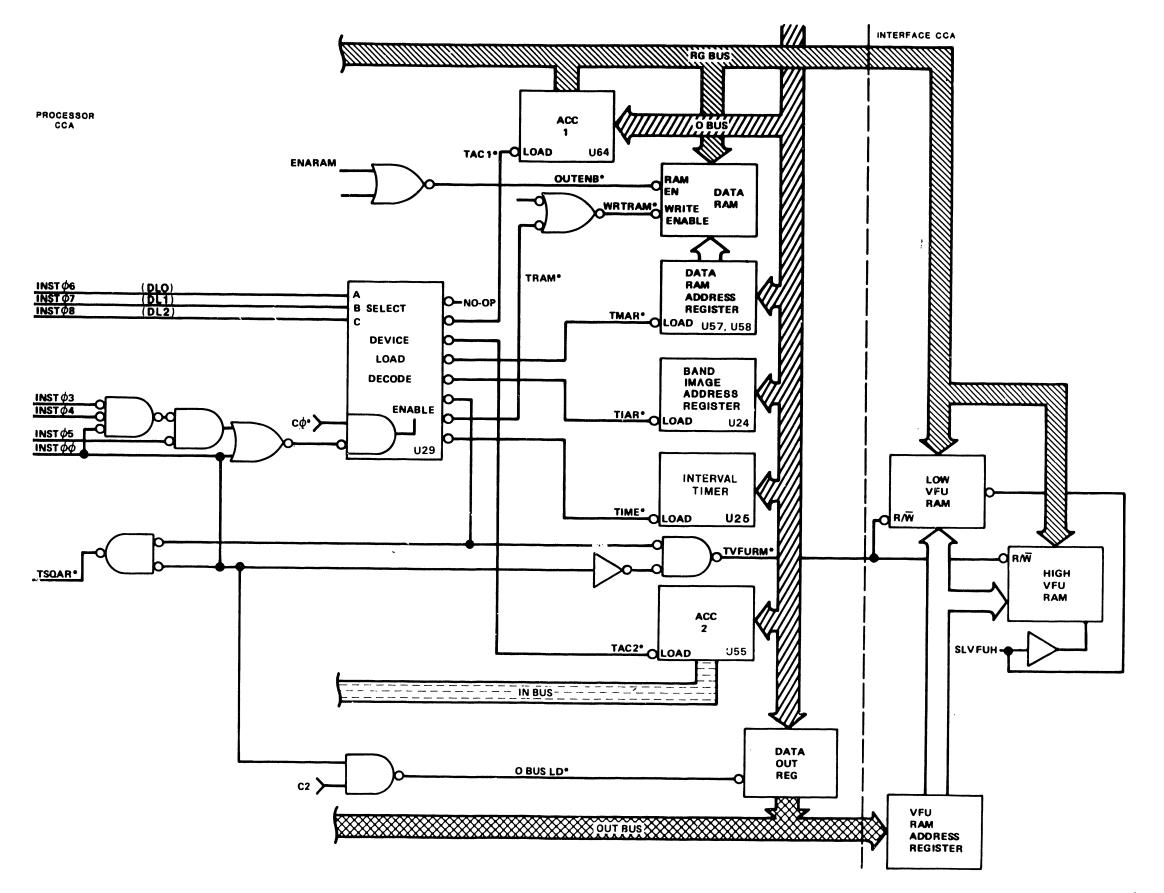

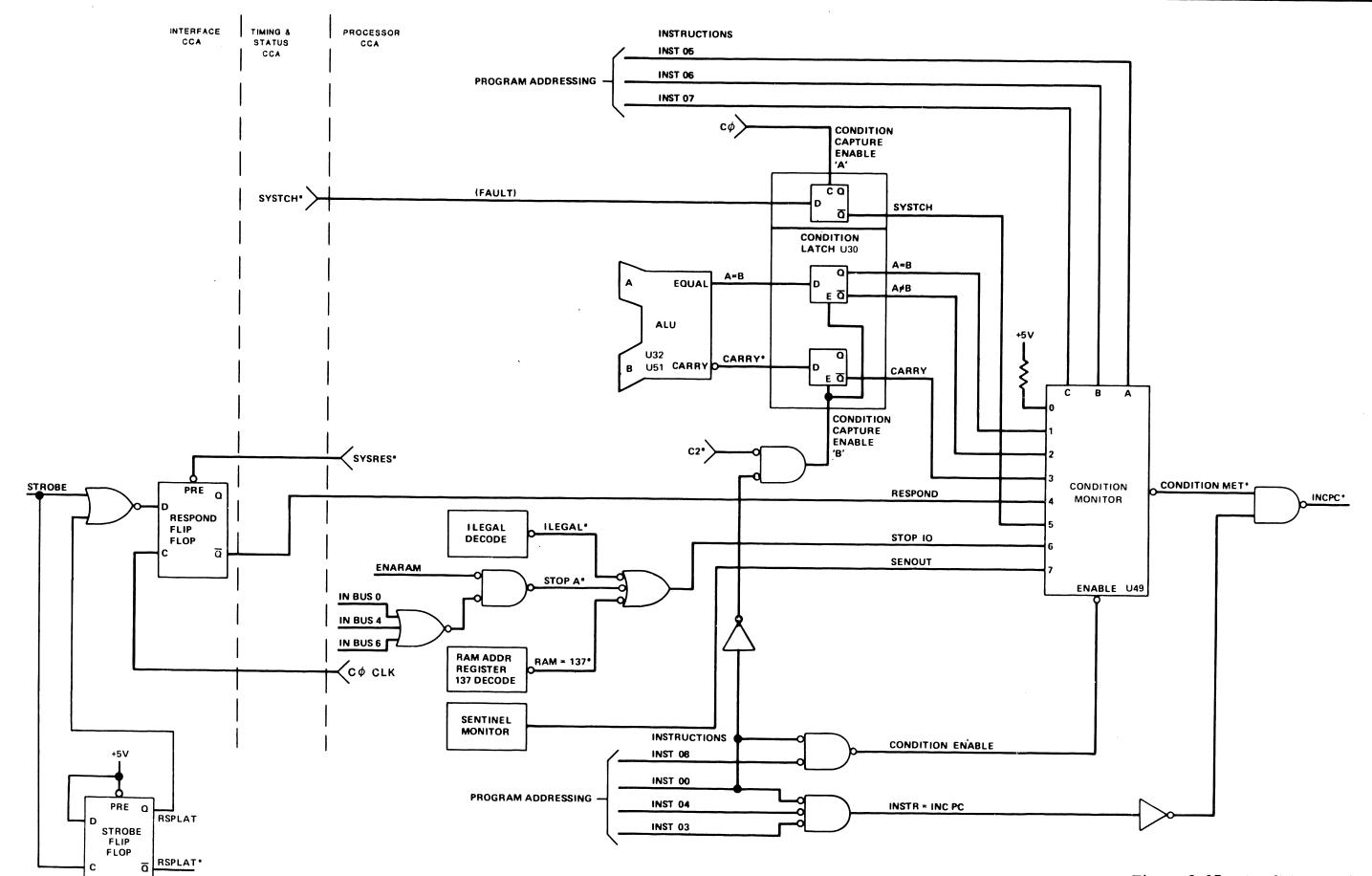

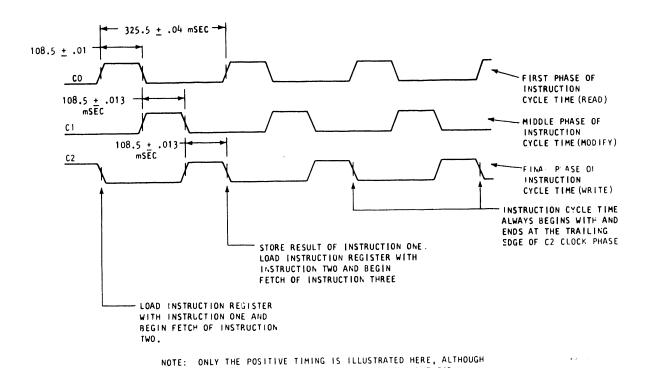

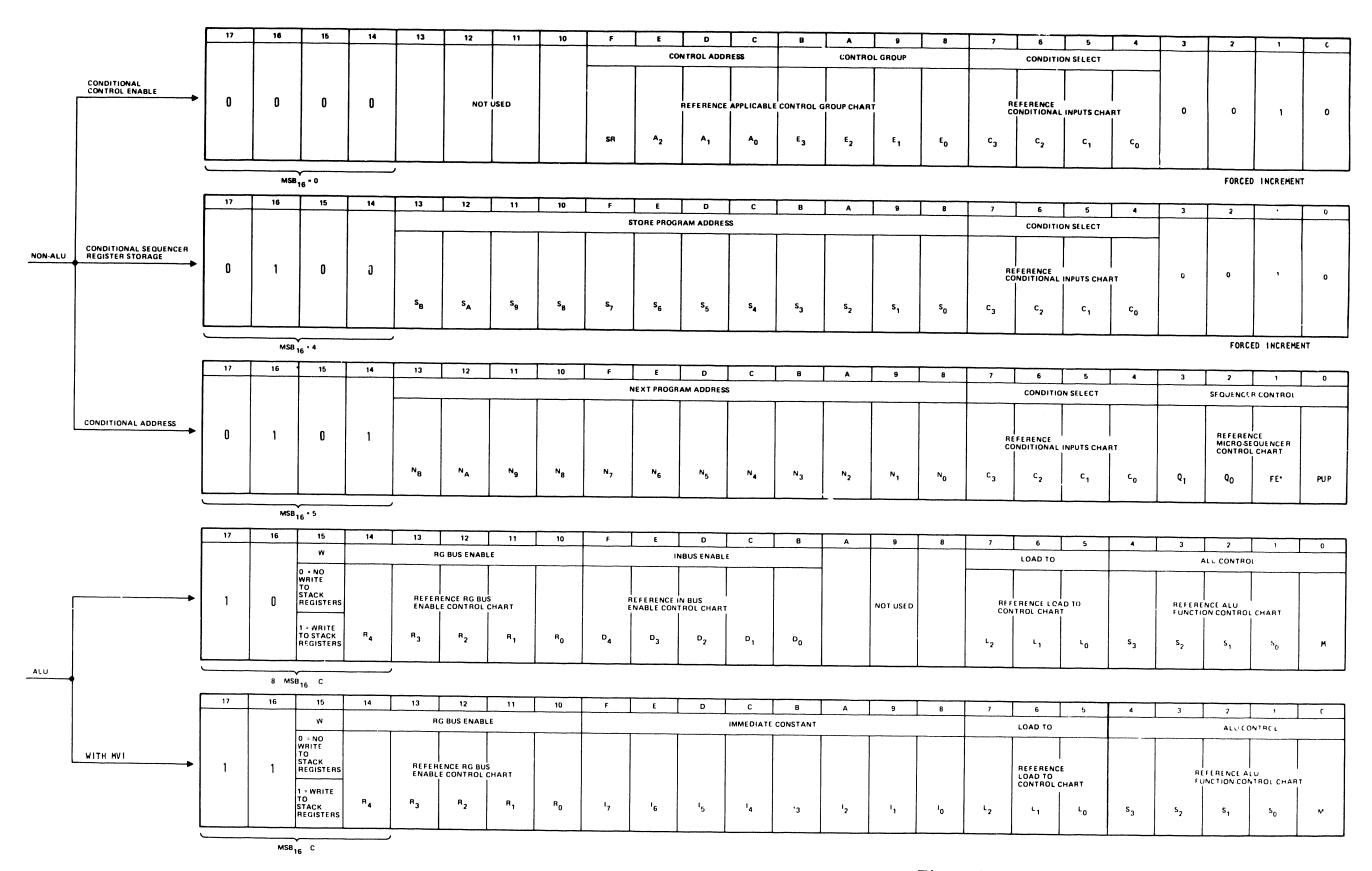

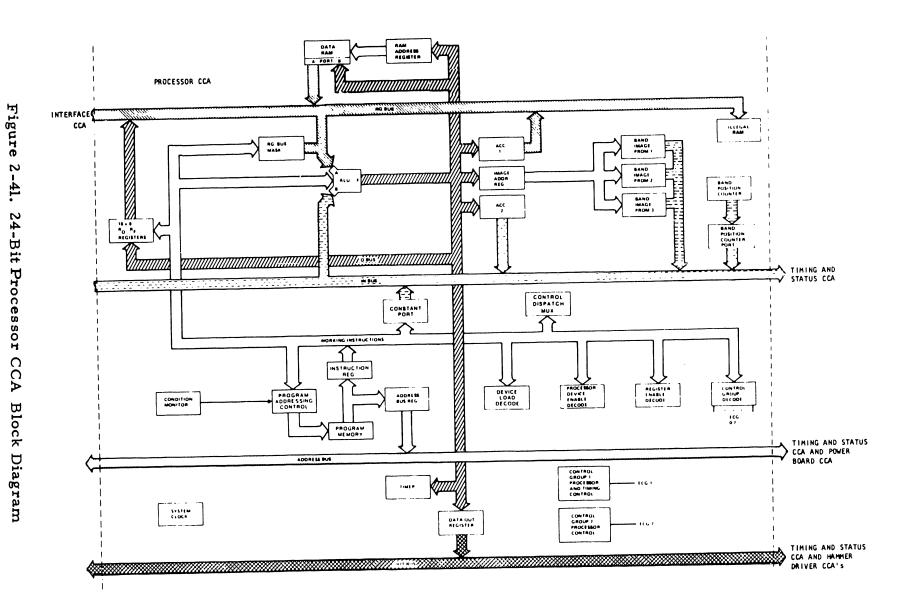

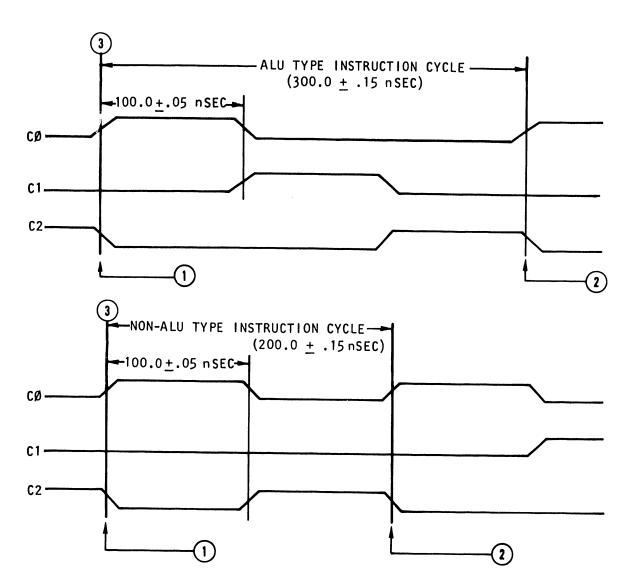

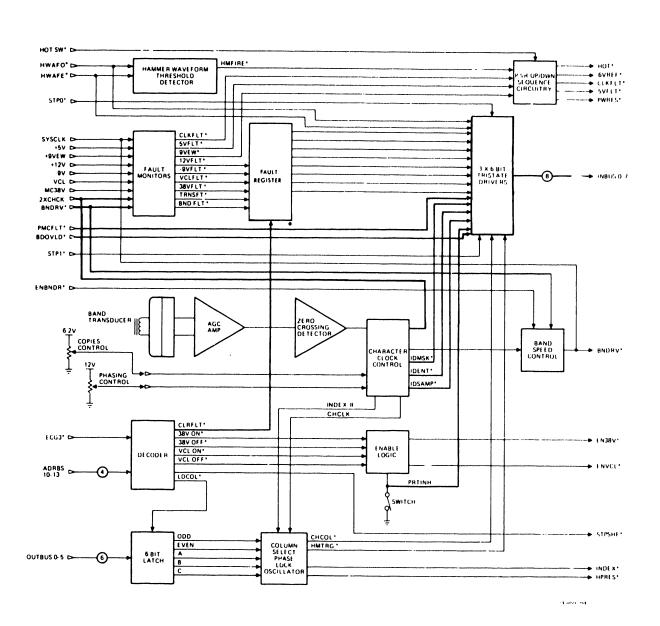

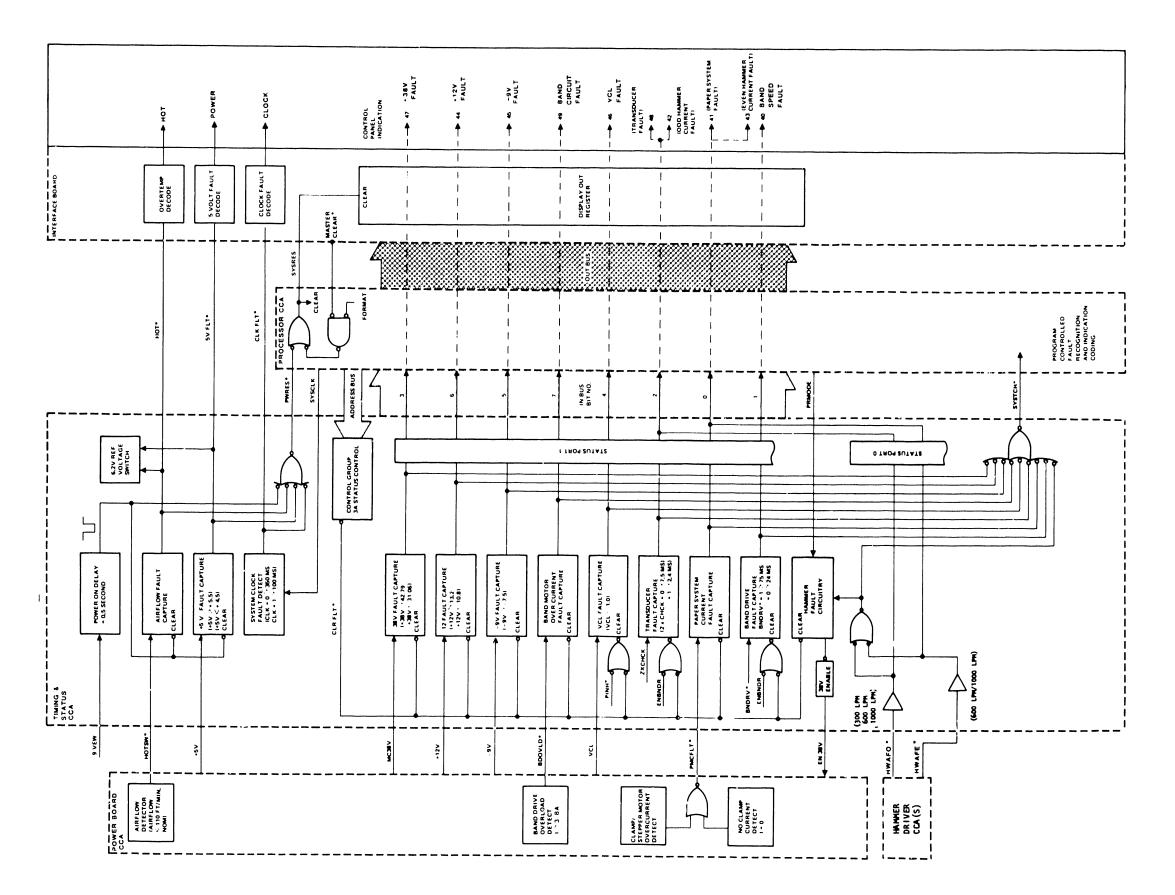

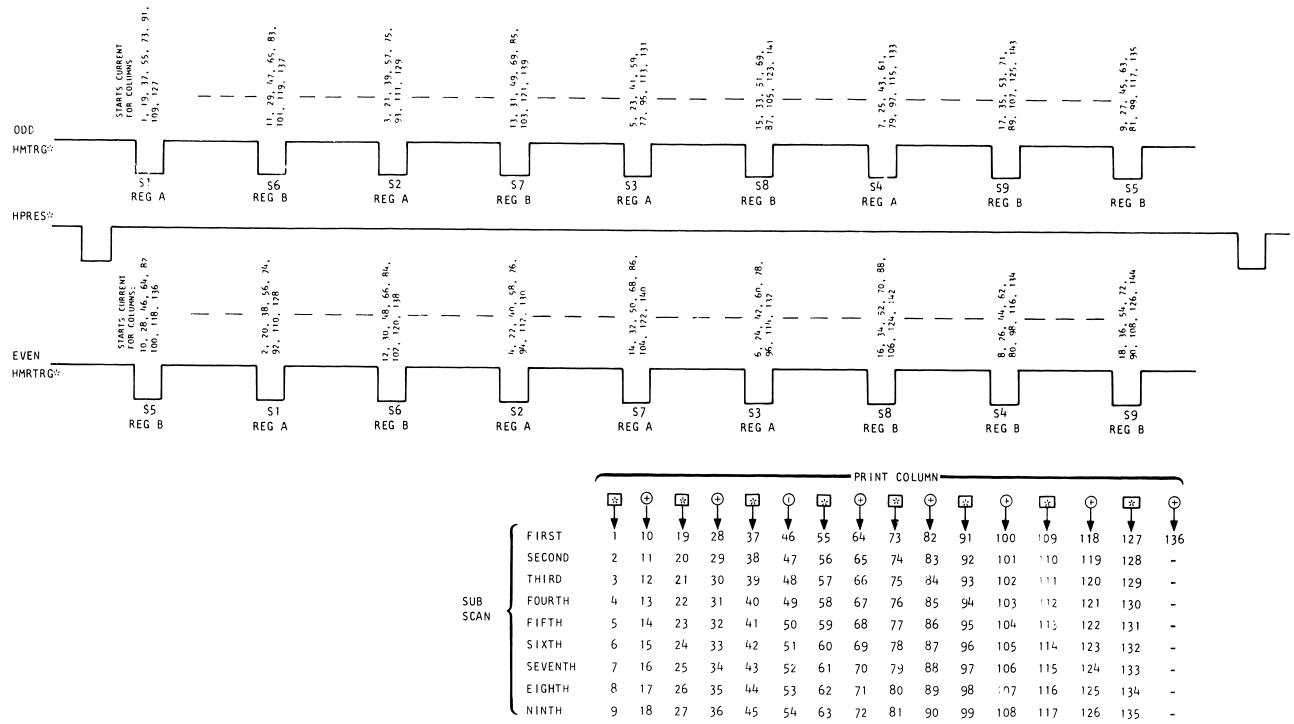

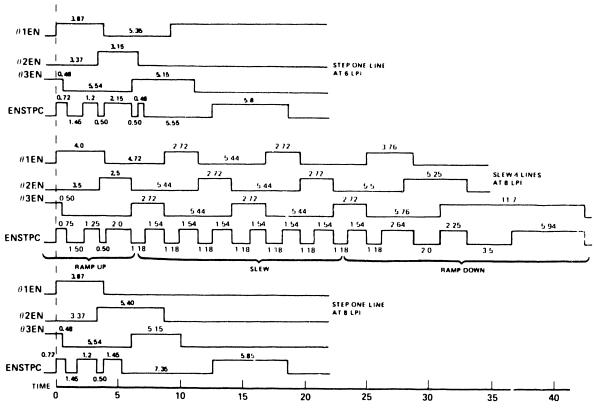

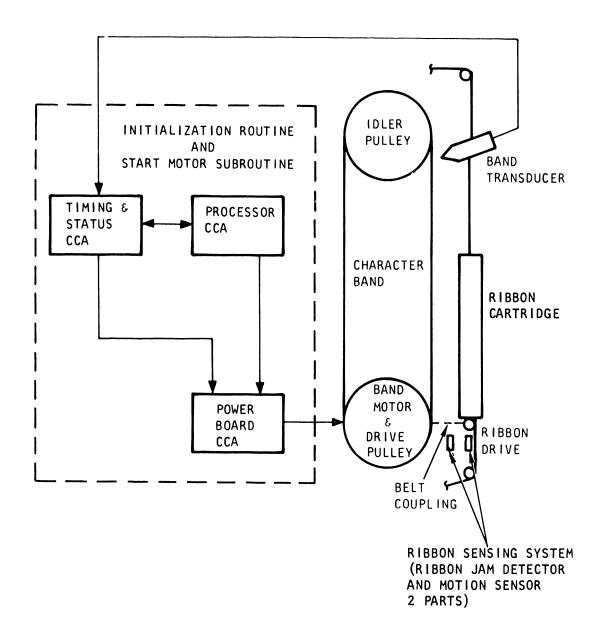

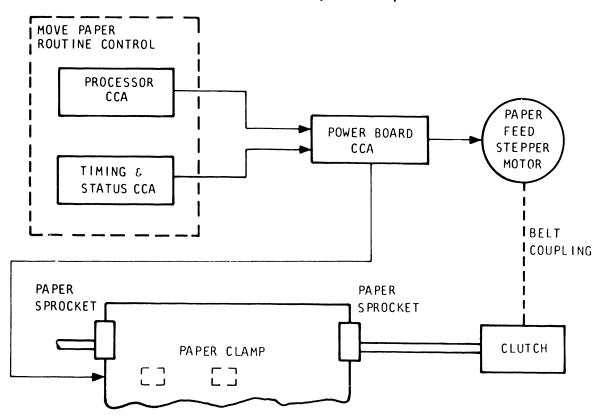

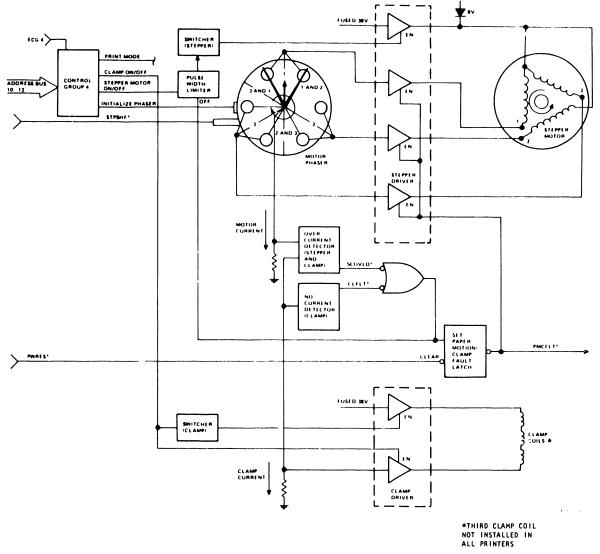

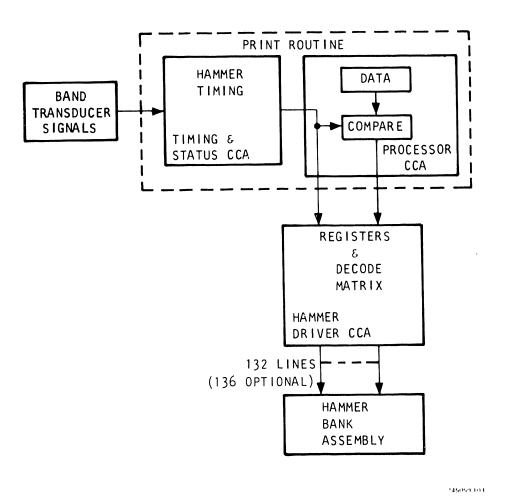

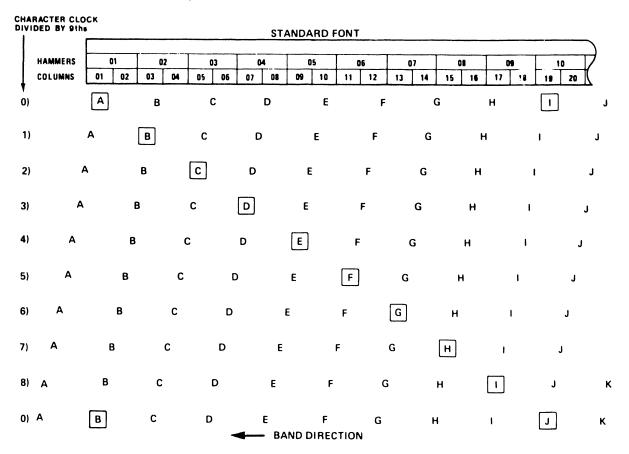

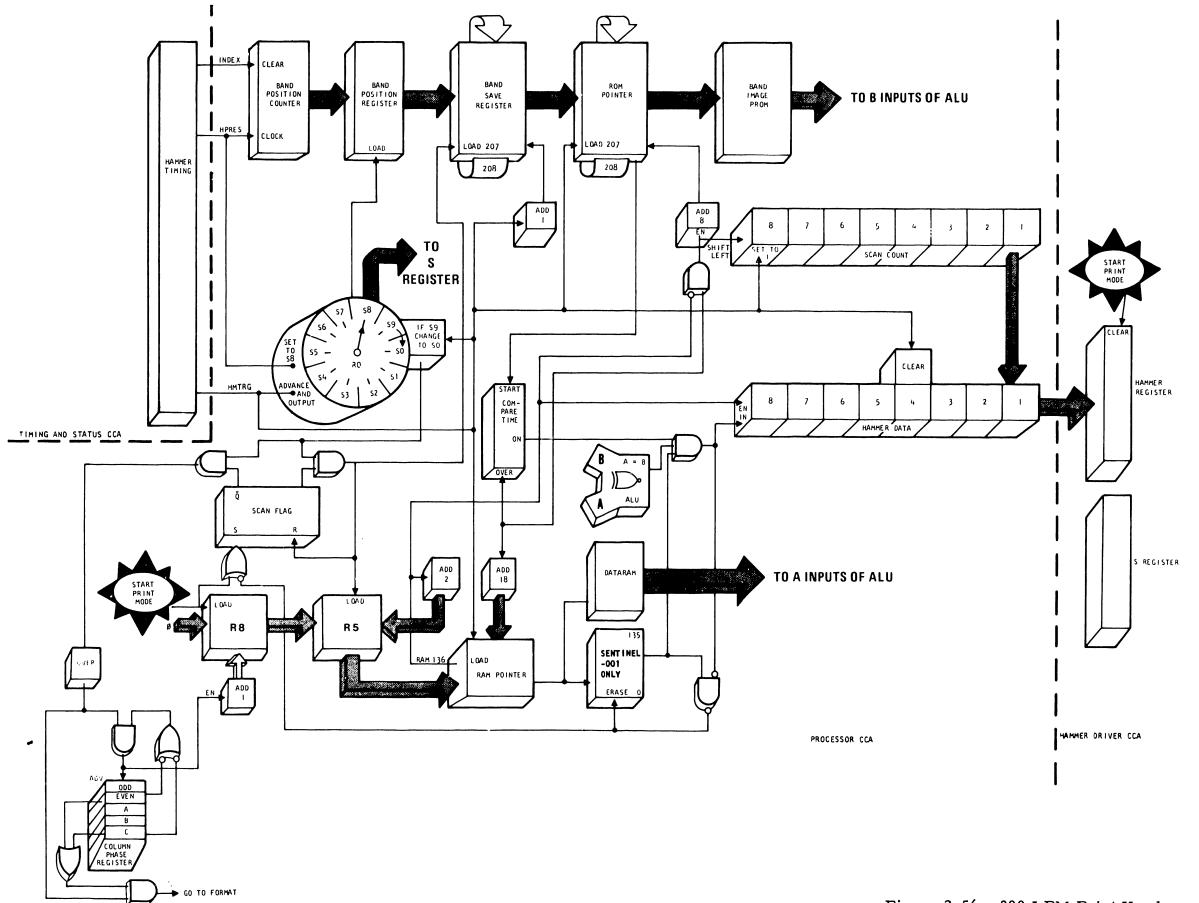

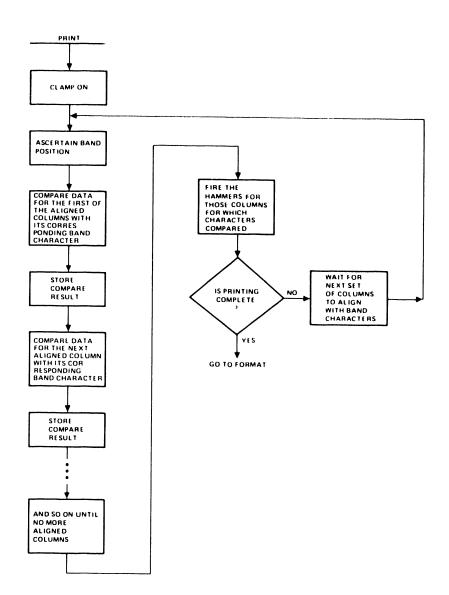

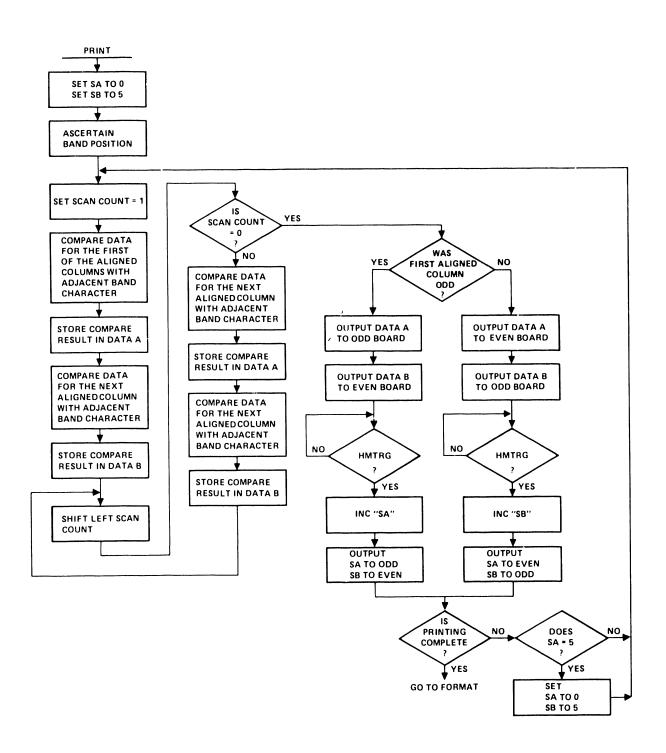

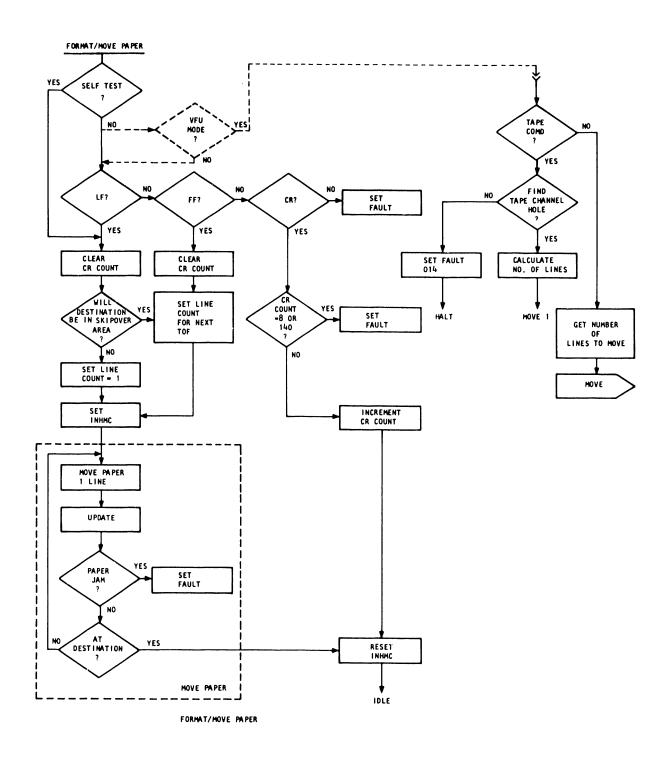

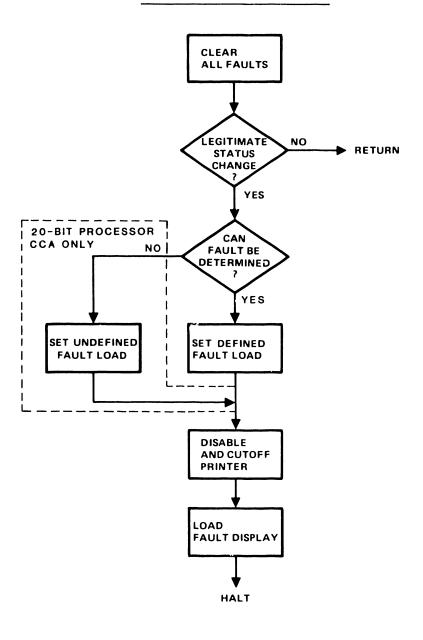

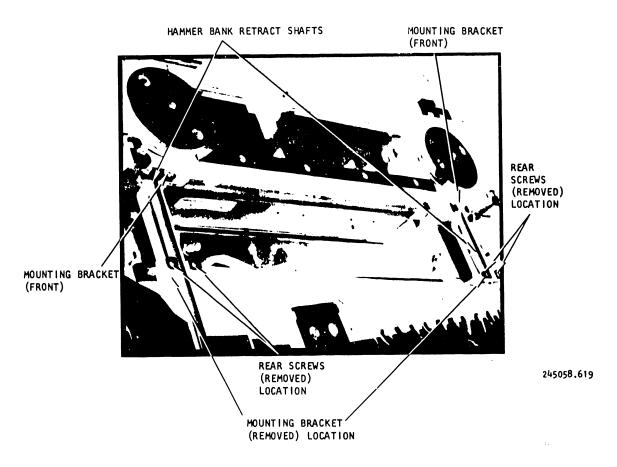

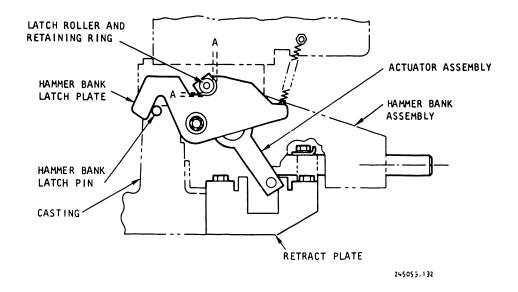

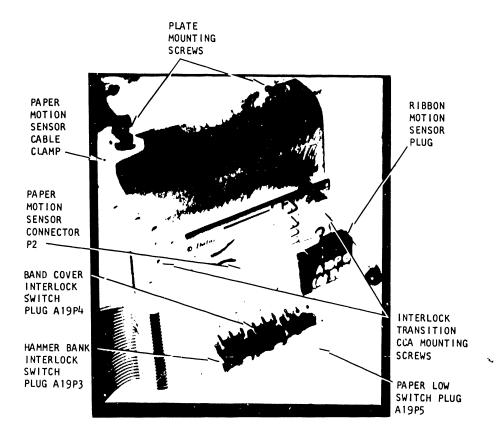

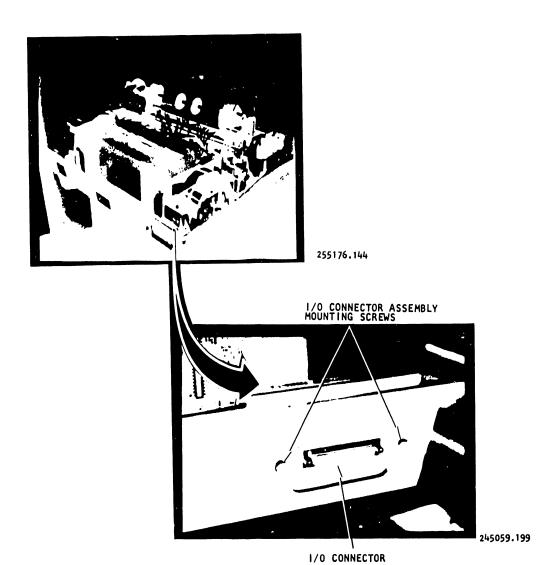

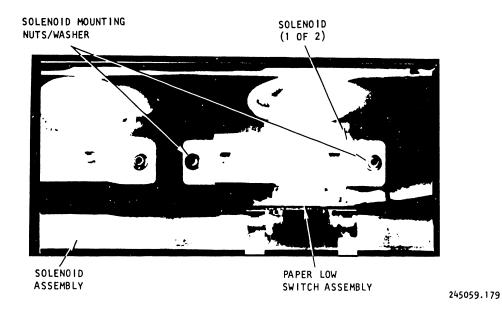

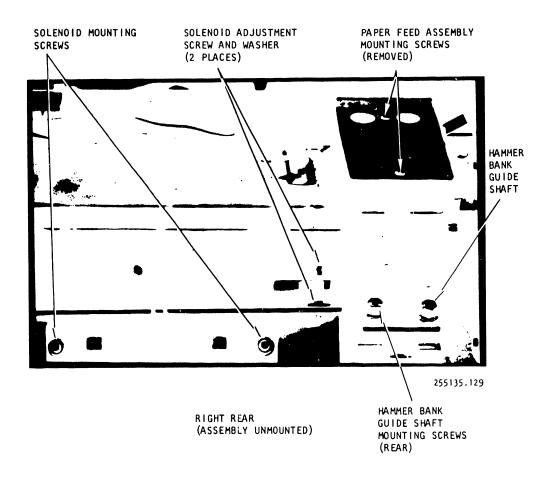

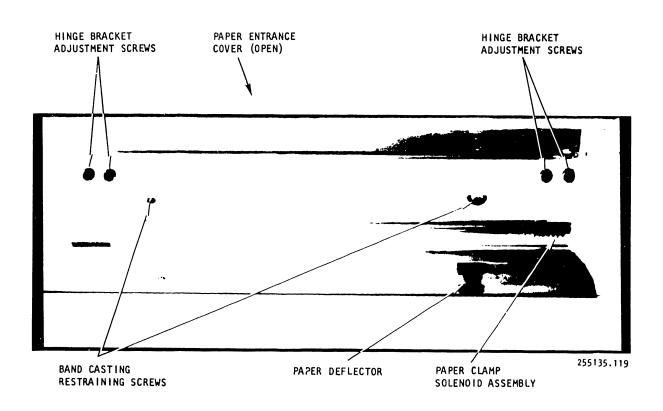

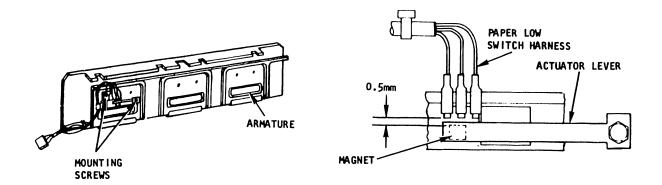

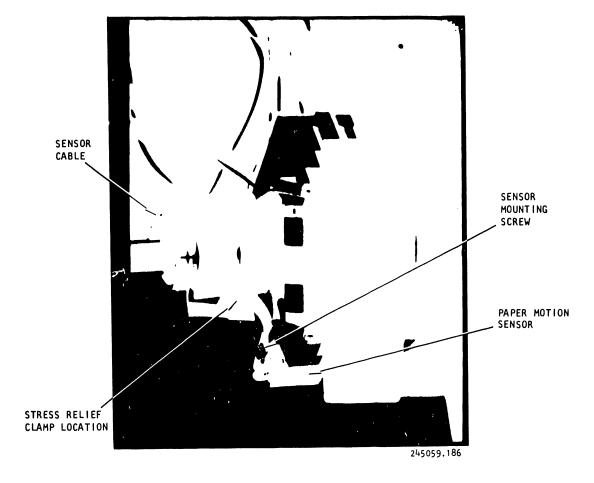

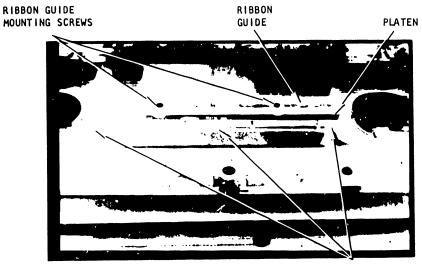

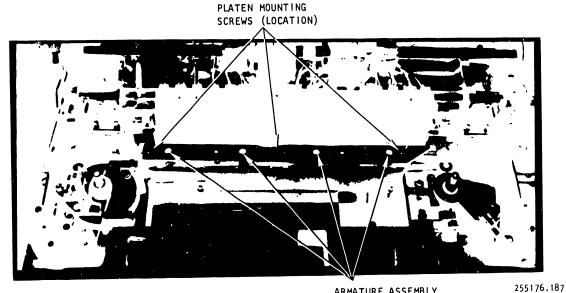

#### d. Low True and Buffer Clear Invert Interfaces