### 8-BIT-PARALLEL I/O INTERFACE CONTROLLER USER MANUAL

(MODEL 2250/OPTION 67)

# 343TEM 2200

# 8-BIT-PARALLEL I/O INTERFACE CONTROLLER USER MANUAL (Model 2250/Option 67)

© Wang Laboratories, Inc., 1978

ABORATORIES, INC.

## Disclaimer of Warranties and Limitation of Liabilities

The staff of Wang Laboratories, Inc., has taken due care in preparing this manual; however, nothing contained herein modifies or alters in any way the standard terms and conditions of the Wang purchase agreement, lease agreement, or rental agreement by which this equipment was acquired, nor increases in any way Wang's liability to the customer. In no event shall Wang Laboratories, Inc., or its subsidiaries be liable for incidental or consequential damages in connection with or arising from the use of this manual or any programs contained herein.

Wang Laboratories, Inc., assumes no responsibility for wiring the male connector, furnished with this interface controller board, to any non-Wang equipment. In no event shall Wang Laboratories, Inc., or its subsidiaries be liable for any damages in connection with or arising from the wiring or operation of non-Wang equipment interfaced to a Wang system.

#### HOW TO USE THIS MANUAL

Information regarding the installation and operation of Wang's 8-Bit-Parallel I/O Interface Controller is provided in this manual. Chapter 1 describes the features of the controller; strobes and signal levels for control of data input and output are described in detail with respect to the 36-pin Amphenol connector which facilitates direct connection of non-Wang devices to a Wang system. The information is essential for anyone planning to wire the male Amphenol connector to the cable from a device being interfaced to a Wang central processor via the controller described herein.

Chapter 2 and several appendices describe  ${\rm I/O}$  operations using BASIC language statements with built-in or customized signal sequences.

#### CONTENTS

|                                  |                                                             | Page                                                        |

|----------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| CHAPTER                          | 1                                                           | CONTROLLER FEATURES                                         |

| CHAPTER                          | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9 | General Information                                         |

|                                  | 2.1<br>2.2<br>2.3<br>2.4                                    | Introduction                                                |

| APPENDIX                         |                                                             | BUILT-IN SIGNAL SEQUENCES FOR DATALOAD BT, INPUT, AND KEYIN |

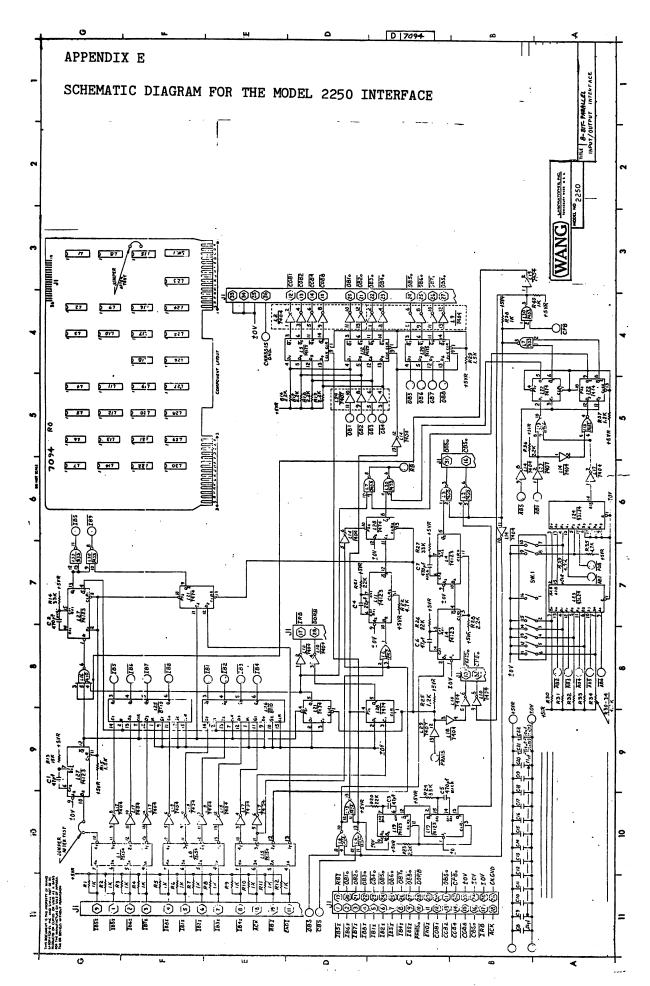

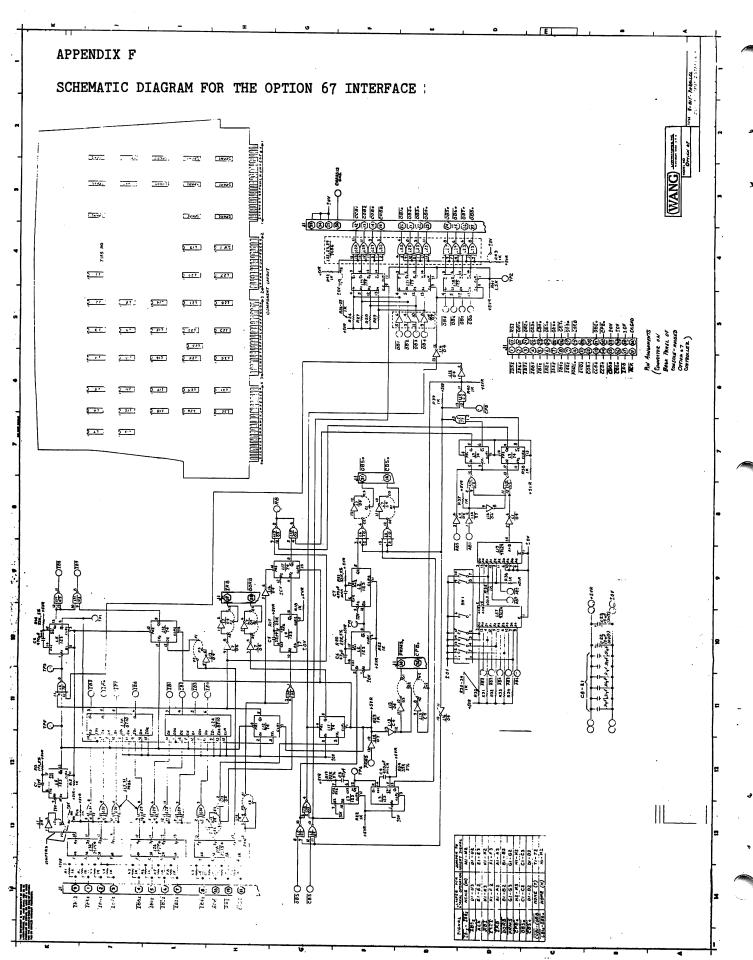

| APPENDIX<br>APPENDIX<br>APPENDIX | ( C<br>( D<br>( E<br>( F                                    | HEXPRINT, AND DATASAVE BT                                   |

| APPENDIX                         |                                                             | SIGNAL LEVEL INVERSION (OPTION 67 ONLY)                     |

| EQUIPMEN                         | NT MAIN                                                     | NTENANCE                                                    |

| INDEX .                          |                                                             | 40                                                          |

| CUSTOME                          | R COMMI                                                     | ENT FORM                                                    |

#### FIGURES

|                                              | Page                                   |

|----------------------------------------------|----------------------------------------|

| A Typical Line Receiver (Input) Circuit      | 3                                      |

| Schematic of Pin Assistments for Trank Date  | 4                                      |

| Schematic of Pin Assignments for Cutaut Data | 9                                      |

| Diamen of 9 Dele Address Costs               | 12                                     |

| Diagram of o-Pole Address Switch             | 33                                     |

| TABLES                                       |                                        |

| I/O Connector Pin Assignments                | 5                                      |

| Input Control Signals                        | 10                                     |

| Output Control Signals                       | 13                                     |

| I/O Interface Controller Addresses           | 15                                     |

| Input Operations                             | 17                                     |

| Output Operations                            | 18                                     |

| Effect of the Device Type Code on PRINT.     | 10                                     |

|                                              | 19                                     |

| Hexadecimal and Binary Equivalents           |                                        |

| for the Address Switch                       | 34                                     |

| ON-OFF Configuration for Address Switch      | 34                                     |

|                                              | A Typical Line Driver (Output) Circuit |

#### CHAPTER 1

#### CONTROLLER FEATURES

#### 1.1 GENERAL INFORMATION

Wang's 8-bit-parallel I/O Interface Controller facilitates direct connection of an 8-bit-parallel non-Wang device to a Wang central processor. The device may be one of the following types:

- a) input only

- b) output only, or

- c) input and output.

The I/O Interface Controller is available in physically different but operationally equivalent versions. One version, called the Model 2250, is attached to a mounting bar for plug-in compatibility with any one of the I/O slots in a 2200 Series CPU (Central Processing Unit) such as the 2200T or 2200VP. Another version, called Option 67, has no mounting bar and is configured to fit within the housing of compact units (such as the PCS-II and WCS/15) where the CRT, keyboard, and central processor are assembled in a single unit.

More than one Model 2250 controller can be installed in a Wang system if sufficient I/O slots are available in the 2200 Series CPU. On the other hand, only one Option 67 controller can be installed in a Wang system whose central processor resides inside the console unit.

Installation of an I/O Interface Controller is the responsibility of a Wang Customer Engineer. If a controller arrives as an addition to existing equipment, call the Wang Customer Engineer; do not attempt to install the controller -- any such attempt may void the warranty.

A 36-pin female Amphenol connector supports direct plug-in of a non-Wang device. The connector is located on the Model 2250 mounting bar or on the back panel of a unit containing an Option 67 controller. Although a 36-pin male Amphenol connector is supplied with each 8-bit-parallel I/O Interface Controller, responsibility for wiring the male connector to the cable from an external device is not assumed by Wang Laboratories.

The controller implements the sequential transfer of information one-byte-at-a-time under program control. Data transfer rates depend upon the BASIC language statement being used to control input or output operations. Although Wang systems use an 8-bit character set with 7-bit ASCII codes and the high-order bit set to zero, individual characters in any single or packed 8-bit codes (e.g., EIA, two 4-bit BCD digits, etc.) can be transmitted between a non-Wang device and a Wang system via an I/O Interface Controller. Furthermore, discrete binary information in an 8-bit format can be transmitted via the controller.

To ensure successful data transfer between a Wang system and an interfaced device, the person or persons responsible for interfacing a particular device to a Wang system must consider such factors as the following:

- . the I/O specifications of the device,

- . the requirements of the online application,

- . the characteristics of the I/O Interface Controller, and

- the signal sequences associated with the BASIC language statements by which input or output operations may be controlled.

Appropriate wiring of the 36-pin male Amphenol connector to the cable from a non-Wang device is a prerequisite to successful online operation of a device.

Detailed descriptions of the strobes and signal levels associated with the 36-pin connector are included in this chapter. Chapter 2 contains programming considerations and gives references to sources where BASIC language I/O signal sequences are described.

#### NOTE:

The terms input and output, as used in this manual, are chosen from the viewpoint of a Wang central processor and an 8-bit-parallel I/O Interface Controller. Thus, a description of an input strobe or signal level translates into a description of an output strobe or signal level when considered from the viewpoint of an interfaced device.

#### 1.2 INPUT/OUTPUT CIRCUITS

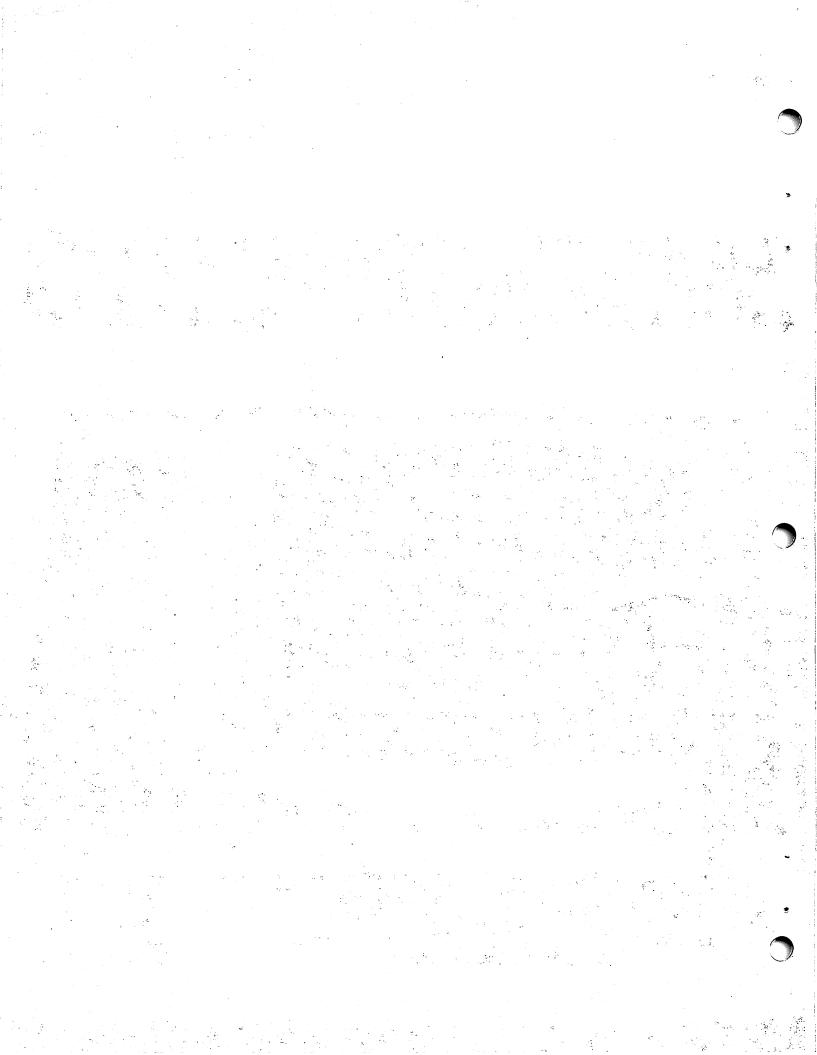

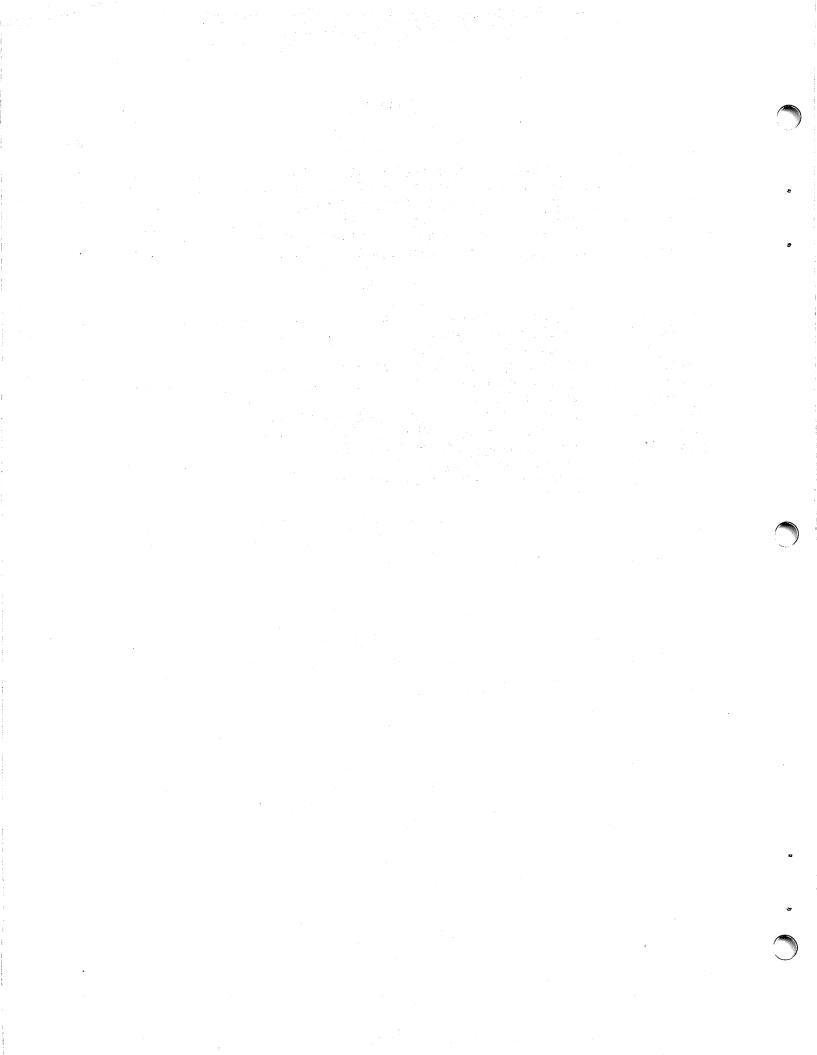

Input/output circuitry for the 8-bit-parallel I/O Interface Controller is TTL/DTL\* compatible. A typical line receiver (input) circuit is shown schematically in Figure 1-1. A typical line driver (output) circuit is shown schematically in Figure 1-2.

<sup>\*</sup>TTL - transistor-transistor-logic, DTL = diode-transistor-logic

Figure 1-1. A Typical Line Receiver (Input) Circuit

Figure 1-2. A Typical Line Driver (Output) Circuit

#### NOTES:

- 1. Use of the controller is adequate for short lines up to 100 feet in length, where environmental noise is not severe.

- 2. For minimum transmission error, Wang Laboratories recommends that the input/output circuitry of external devices include the same (or equivalent) line driver/receiver circuits as shown in Figures 1-1 and 1-2.

#### 1.3 SIGNAL SPECIFICATIONS

Voltage levels for the controller are as follows:

Logic "0" (False) is between +2.4 and 3.6 volts. Logic "1" (True) is between 0 and +0.4 volts.

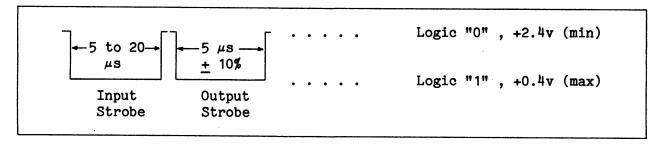

The pulse width of output strobes from the controller is 5 microseconds, plus or minus 10%. The pulse width of input strobes from an interfaced device must lie in the range from 5 to 20 microseconds. See Figure 1-3.

Figure 1-3. Schematic of Input and Output Strobes

#### NOTES:

1. In this manual, the signal levels are denoted by the abbreviations Hi and Lo, where:

Hi = high level = logic "0". Lo = low level = logic "1".

2. By special request, the level of some signals on the Option 67 version of the I/O Interface Controller can be inverted by a Wang Customer Engineer. However, if such action occurs, it becomes the customer's responsibility to indicate the effective changes in the copy of this manual supplied with the controller.

#### 1.4 I/O CONNECTOR PIN ASSIGNMENTS

The functional assignments for the 36-pin Amphenol connector are listed in Table 1-1. An open pin connection for an input circuit is equivalent to a high-level signal (logic "0").

Table 1-1. I/O Connector Pin Assignments

| Pin<br>No.                           | Signal<br>Mnemonic                                          | I/O*                       | Remarks                                                                                                                                  |                                              | Signal<br>Mnemonic                                          | I/O*    | Remarks                                                                                                                                   |

|--------------------------------------|-------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 185<br>1861<br>1871<br>1881<br>1811<br>1821<br>1831<br>1841 | I<br>I<br>I<br>I<br>I<br>I | 8-Bit-Parallel, Buffered Input 10 High-order 20 hexdigit 40 8-4-2-1 80 bit positions. 01 Low-order 02 hexdigit 04 8-4-2-1 bit positions. | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | OB1<br>OB2O<br>OB3O<br>OB4O<br>OB5O<br>OB6O<br>OB7O<br>OB8O | 0000000 | 8-Bit-Parallel, Buffered Output 01 Low-order 02 hexdigit 04 8-4-2-1 08 bit positions. 10 High-order 20 hexdigit 40 8-4-2-1 bit positions. |

| 9                                    | ĪBS <sub>I</sub>                                            | I                          | Input Strobe from External Device                                                                                                        | 28                                           | DORB                                                        | 0       | Data-Output-Buffer<br>Empty/Full Level                                                                                                    |

| 10                                   | PRMS                                                        | 0                          | Prime Output Strobe                                                                                                                      | 29                                           |                                                             |         | Spare                                                                                                                                     |

| 11                                   | ĒNDĪ <sub>I</sub>                                           | I                          | End-of-Input or Special<br>Control Level (Buffered)                                                                                      | 30                                           |                                                             |         | Spare                                                                                                                                     |

| 12<br>13                             | COB1<br>COB2                                                | 0                          | 1 4-bits, buffered<br>2 Control Information                                                                                              | 31                                           | ŌBS <sub>O</sub>                                            | 0       | Data Output Strobe                                                                                                                        |

| 14                                   | COB2<br>COB4<br>COB8<br>COB8                                | 0                          | 4 Output                                                                                                                                 | 32                                           | CPB <sub>O</sub>                                            | 0       | CPU/Controller<br>Ready/Busy Level                                                                                                        |

| 16                                   | CBS <sub>O</sub>                                            | 0                          | Control Output Strobe                                                                                                                    | 33                                           |                                                             |         | + 0 volts                                                                                                                                 |

| 17                                   | ĪRB                                                         | 0                          | Input-Buffer Empty/Full<br>Level                                                                                                         | 34<br>35                                     |                                                             |         | common .                                                                                                                                  |

| 18                                   | ACK                                                         | I                          | External Device Acknow-<br>ledge Strobe                                                                                                  | 36                                           |                                                             |         | Chassis Ground                                                                                                                            |

| 19                                   | RBI                                                         | I                          | External Device Ready/<br>Busy Level                                                                                                     |                                              |                                                             |         |                                                                                                                                           |

<sup>\*</sup>As seen by the Wang system and I/O Interface Controller

#### 1.5 SIGNAL MNEMONICS AND DESCRIPTIONS

For easy reference, this section describes the signal mnemonics in alphabetical order. In other sections, functionally related signals are grouped together.

ACK -- Pin 18

External Device Acknowledge -- an input strobe from an external device requiring "strobes" longer than  $5\,\mu\,s$ .  $\overline{\text{ACK}}$  resets  $\overline{\text{DORB}}$  to Hi (logic "0", Ready). Generally, if  $\overline{\text{ACK}}$  is used,  $\overline{\text{DORB}}$  should be connected to  $\overline{\text{RBI}}$  so the controller effectively provides its own ready/busy level for output operations. The leading edge of an  $\overline{\text{ACK}}$  strobe should not occur before the trailing edge of an  $\overline{\text{OBS}}_0$  or  $\overline{\text{CBS}}_0$  strobe.

$\overline{\text{CBS}}_{0}$  -- Pin 16

Control Output Strobe -- a  $5\mu$ s output strobe produced when a  $\overline{\text{CBS}}$  strobe from the CPU loads one byte of information into the controller's 8-bit Data Output Buffer and simultaneously loads the 4-bit Control Information Buffer with the four low-order bits of the byte.

COB1<sub>0</sub>,COB2<sub>0</sub>,COB4<sub>0</sub>,COB8<sub>0</sub>

-- Pins 12, 13, 14, 15

Control Information Output -- output levels corresponding to the 4-bit Control Information Buffer loaded by a  $\overline{\text{CBS}}$  strobe. The levels are latched until a subsequent  $\overline{\text{CBS}}$  strobe occurs.

$\overline{\text{CPB}}_{\text{O}}$  -- Pin 32

CPU Ready/Busy -- an output level indicating when the CPU and controller are ready to receive an input strobe from an external device. Hi (logic "O", Ready) indicates two conditions: (1) CPU awaiting input and (2) controller enabled. Lo (logic "1", Busy) is set by the controller when the TB1 through TB8 levels are strobed into the CPU, or at any time the controller is unable to accept data.

DORB -- Pin 28

Data Output Buffer Empty/Full -- an output level available for external devices requiring "strobes" longer than  $5\mu$ s. Lo (logic "1", Full) is set when the CPU strobes information via an  $\overline{\text{OBS}}$  or  $\overline{\text{CBS}}$  strobe into the controller's one-byte Data Output Buffer. Hi (logic "0", Empty) is reset by an  $\overline{\text{ACK}}$  strobe. Caution: Since  $\overline{\text{DORB}}$  is set Lo at the same time data is latched, devices using  $\overline{\text{DORB}}$  should delay after its leading edge.

ENDI -- Pin 11

End-of-Input or Special-Control Level — an optional ninth input level. If Pin 11 is not connected,  $\overline{\text{ENDI}}$  is always Hi (logic "0") to indicate standard data on Pins 1 through 8. Some BASIC statements test the buffered  $\overline{\text{ENDI}}$  level and execute alternative procedures if the level is Lo (logic "1") to indicate a special or termination condition when a byte of information is received. If used, the level must be available at the leading edge of the  $\overline{\text{IBS}}_{\text{T}}$  strobe.

IB1<sub>T</sub> through IB8<sub>T</sub>

-- Pins 1 through 8

Input Data (Buffered) -- input levels corresponding to one byte of information in 8-bit-parallel format. The levels must be available at the leading edge of the  $\overline{\text{IBS}}_{1}$  strobe. Upon receipt of an  $\overline{\text{IBS}}_{1}$  strobe, the levels on Pins 1 through 8 are strobed into the controller's 8-bit Input Buffer and held until  $\overline{\text{CPB}}_{0}$  is Hi; then the information is strobed into the CPU buffer.

$\overline{\text{IBS}}_{\text{T}}$  -- Pin 9

Input Strobe -- an input strobe indicating the availability of eight data levels,  $\overline{\text{IB1}}$  through  $\overline{\text{IB8}}_{\text{T}}$ , and an optional ninth level,  $\overline{\text{ENDI}}$ .

IRB -- Pin 17

Input Buffer Empty/Full -- an output level indicating when the controller's 8-bit Input Buffer contains information awaiting transfer to the CPU. Lo (logic "1", Full) is set by an  $\overline{\text{IBS}}_{\text{T}}$  strobe; Hi (logic "0", Empty) is reset when the  $\overline{\text{IBI}}_{\text{T}}$  through  $\overline{\text{IB8}}_{\text{T}}$  levels are strobed into the CPU by the controller.  $\overline{\text{IRB}}$  is also available to the CPU for testing if the controller is enabled with its even address (low-order bit "0"). See Section 2.2.

OB1 through OB8 o -- Pins 20 through 27

Output Data (Buffered) -- output levels corresponding to one byte of information in the controller's Data Output Buffer. Usually these levels are strobed into the buffer by an  $\overline{\text{OBS}}$  strobe from the CPU; however, during execution of some BASIC statements and particular \$GIO microcommands, the eight levels are strobed into the buffer by a  $\overline{\text{CBS}}$  strobe. The levels are latched until a subsequent  $\overline{\text{OBS}}$  or  $\overline{\text{CBS}}$  strobe occurs.

OBS -- Pin 31

Output Data Strobe -- a  $5\,\mu$  s output strobe produced when an  $\overline{\rm OBS}$  strobe from the CPU loads one byte of information into the controller's 8-bit Data Output Buffer.

PRMS<sub>O</sub> -- Pin 10

Prime Output Strobe -- a  $5\,\mu\,\mathrm{s}$  output strobe generated when the RESET button on the Wang system keyboard is depressed to interrupt an operation and return control to the operator. Generally, the signal is used by peripheral devices as a reset/initialization signal.

**RBI** -- Pin 19

External Device Ready/Busy -- an input level from an external device, where Hi (logic "0", Ready) indicates the device is ready to receive Wang system output, and Lo (logic "1", Busy) indicates the device is not ready.  $\overline{\text{RBI}}$  should be set to Lo within  $2\,\mu$ s of the leading edge of an  $\overline{\text{OBS}}$  or  $\overline{\text{CBS}}$  strobe; otherwise, a second output strobe may result from one ready level.  $\overline{\text{RBI}}$  should remain Lo until the trailing edge of an  $\overline{\text{OBS}}$  or  $\overline{\text{CBS}}$  occurs, regardless of the speed of the device.  $\overline{\text{RBI}}$  is also available to the CPU for testing if the controller is enabled with its odd address (low-order bit "1").

#### NOTES:

- 1. By using the \$GIO statement to custom-tailor the signal sequence for an I/O operation, data can be sent from the CPU via a CBS or an OBS strobe, as desired.

- 2. OBS strobes are sent from the CPU on the output bus circuit; CBS strobes are sent on the control bus circuit. If an I/O Interface Controller is enabled at the time an OBS strobe is sent, 8-bits are strobed into the controller's Data Output Buffer and an OBS strobe is produced on Pin 31 of the connector. Similarly, if an interface controller is enabled at the time a CBS strobe is sent, 8-bits are strobed into the Data Output Buffer, the 4 low-order bits are simultaneously strobed into the Control Information Buffer, and a CBS strobe is produced on Pin 16 of the connector.

- 3. If the ENDI level on Pin 11 is Lo (Logic "1") when a byte of information is received, a special condition is indicated; however, the significance of the condition depends upon the BASIC statement being executed. Statements such as INPUT and KEYIN utilize the ENDI level; also, \$GIO has the capability to check ENDI if microcommands with valid "Check T" codes are used.

#### 1.6 INPUT DATA SIGNALS

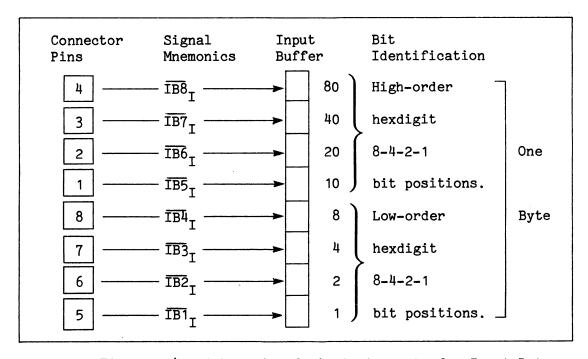

Pins 1 through 8 in the 36-pin connector are allocated for 8-bit-parallel input from an interfaced device. The eight levels represented by the mnemonics  $\overline{1B1}_{I}$  through  $\overline{1B8}_{I}$  correspond to one byte of information.

Figure 1-4 shows the correspondence between the connector pins, the signal mnemonics, and the bit positions in the controller's Input Buffer. Labels for the bit positions in the one-byte buffer are defined with respect to the 8-bit character set used by the Wang system (7-bit ASCII codes and the eighth bit set to zero). However, any single or packed 8-bit codes (or discrete binary data) are acceptable as input via the controller.

When an external device sends an  $\overline{\text{IBS}}_{\text{I}}$  strobe on Pin 9, the levels on Pins 1 through 8 are strobed into the controller's Input Buffer and held or immediately strobed into the CPU, depending upon the timing of the  $\overline{\text{IBS}}_{\text{I}}$  strobe relative to the  $\overline{\text{CPB}}_{\text{O}}$  level. The timing is dependent upon the signal sequence of the input operation being executed.

Figure 1-4. Schematic of Pin Assignments for Input Data

#### NOTE:

The levels  $\overline{IB1}$  through  $\overline{IB8}$  on Pins 1 through 8 must be available at the leading edge of an  $\overline{IBS}_I$  strobe on Pin 9.

#### 1.7 INPUT CONTROL SIGNALS

Strobes and signal levels available for control of input operations are summarized in Table 1-2. Also, for special applications, the levels  $\overline{\text{COB1}}_0$ ,  $\overline{\text{COB2}}_0$ ,  $\overline{\text{COB4}}_0$ , and  $\overline{\text{COB8}}_0$  on Pins 12 through 15 can be used to control input (and output) operations.

Table 1-2. Input Control Signals

| Mnemonic         | Pin<br>Number | Signal<br>Origin   | Signal<br>Type                                                              | Remarks                                                                                                                                                                                                                        |

|------------------|---------------|--------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĪBS <sub>I</sub> | 9             | external<br>device | Input strobe                                                                | Indicates one-byte of data is available on Pins 1 through 8.                                                                                                                                                                   |

| ĒNDĪ             | 11            | external<br>device | Input level: Hi (or Open)= standard data. Lo = special or termination data. | If used, this optional, buffered, termination or special condition level must be available at the leading edge of $\overline{\text{IBS}}_{\text{I}}$ .                                                                         |

| <sup>Ĉ₽B</sup> O | 32            | CPU/<br>controller | Output level: Hi=controller enabled & CPU awaiting input. Lo=CPU busy.      | Indicates when the CPU is ready for input via the controller. (See Note 1 on the following page.)                                                                                                                              |

| ĪRB              | 17            | CPU/<br>controller | Output level: Hi=Empty. Lo=Full.                                            | Indicates when the Input Buffer contains information awaiting transfer to the CPU; IRB is also available to the CPU for testing if the controller is enabled with its even address. (See Notes 2 and 3 on the following page.) |

| PRMSO            | 10            | CPU/<br>controller | Output strobe                                                               | Produced when the Wang system RESET key is depressed to interrupt an operation and return control to the operator.                                                                                                             |

#### NOTES:

- 1. Devices using  $\overline{\text{CPB}}_0$  to govern input to the controller should ignore a Hi (CPU ready) level until an  $\overline{\text{IBS}}_1$  strobe is completed. Although overlapping strobes will not occur if programming techniques ensure that the CPU time interval between accepting a strobe and becoming ready for another strobe is much longer than an  $\overline{\text{IBS}}_1$  strobe, the preferred technique is to have the external device hardware design protect against overlapping strobes.

- 2. Devices using  $\overline{\text{IRB}}$  to govern input to the controller should ignore a Hi (buffer empty) level until an  $\overline{\text{IBS}}_{\text{I}}$  strobe is completed; otherwise, overlapping strobes can cause problems which programming techniques cannot solve.

- 3. If the controller is enabled with its odd address (low-order bit "1") for an input operation, the RBI level on Pin 19 (not the IRB level on Pin 17) is available to the CPU for testing.

#### 1.8 OUTPUT DATA SIGNALS

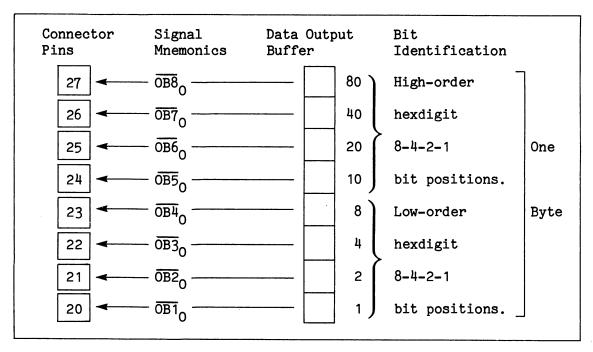

Pins 20 through 27 in the connector are allocated for 8-bit-parallel output from the Wang system to an interfaced device. The eight levels  $\overline{\text{OB1}}_{0}$  through  $\overline{\text{OB8}}_{0}$  correspond to one byte of information (8-bits) in the controller's Data Output Buffer.

Figure 1-5 shows the correspondence between the connector pins, the signal mnemonics, and the bit positions in the controller's Data Output Buffer.

During an output operation, the Data Output Buffer is loaded by either an  $\overline{\text{OBS}}$  or a  $\overline{\text{CBS}}$  strobe from the CPU, depending upon the BASIC language statement or \$GIO microcommand being executed. Therefore, either an  $\overline{\text{OBS}}_0$  strobe on Pin 31 or a  $\overline{\text{CBS}}_0$  strobe on Pin 16 is produced by the controller when the Data Output Buffer contains a byte of information.

Figure 1-5. Schematic of Pin Assignments for Output Data

#### NOTES:

- 1. The eight Data Output Buffer signal levels are latched until a subsequent OBS or CBS strobe occurs.

- 2. When a  $\overline{\text{CBS}}$  strobe from the CPU loads the Data Output Buffer, the strobe also loads the 4-bit Control Information Buffer with signal levels corresponding to the low-order hexdigit. The Control Information Buffer levels are latched until a subsequent  $\overline{\text{CBS}}$  strobe occurs -- they are not altered by  $\overline{\text{OBS}}$  strobes. See Section 1.5 and Table 1-3.

#### 1.9 OUTPUT CONTROL SIGNALS

Strobes and signal levels available for control of output operations are summarized in Table 1-3.

Table 1-3. Output Control Signals

|                                                         | Pin             | Signal             | Signal                                     |                                                                                                                                                                                                            |

|---------------------------------------------------------|-----------------|--------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic                                                | Number          | Origin             | Туре                                       | Remarks                                                                                                                                                                                                    |

| ĀCK                                                     | 18              | external<br>device | Input strobe                               | ACK resets DORB to Hi.  ACK should be used by devices designed to acknowledge each received strobe with a "handshake" or acknowledgment strobe, or by devices requiring output "strobes" longer than 5 μs. |

| RBI                                                     | 19              | external<br>device | Input level: Hi = Ready. Lo = Busy.        | RBI is available to the CPU for testing if the controller is enabled with its odd address.                                                                                                                 |

| PRMSO                                                   | 10              | CPU/<br>controller | Output<br>strobe                           | Produced when the Wang system RESET key is depressed to interrupt an operation and return control to the operator.                                                                                         |

| ŌBS <sub>O</sub>                                        | 31              | CPU/<br>controller | Output<br>strobe                           | Produced when an OBS strobe from the CPU loads the 8-bit Data Output Buffer.                                                                                                                               |

| DORB                                                    | 28              | CPU/<br>controller | Output level:<br>Hi = Empty.<br>Lo = Full. | Set to Lo when either an OBS or CBS strobe from the CPU loads the Data Output Buffer; reset to Hi by an ACK strobe.                                                                                        |

| CBS <sub>O</sub>                                        | 16              | CPU/<br>controller | Output<br>strobe                           | Produced when a CBS strobe from the CPU simultaneously loads the 8-bit Data Output Buffer and the 4-bit Control Information Buffer.                                                                        |

| COB1 <sub>0</sub> ,COB2 <sub>0</sub> ,COB8 <sub>0</sub> | 12,13,<br>14,15 | CPU/<br>controller |                                            | Levels strobed into the Control Information Buffer by a $\overline{\text{CBS}}$ strobe, and latched until another $\overline{\text{CBS}}$ strobe occurs.                                                   |

#### CHAPTER 2

#### PROGRAMMING CONSIDERATIONS

#### 2.1 INTRODUCTION

The customized nature of applications involving interfaced non-Wang devices precludes presentation of detailed programming examples; therefore, the information in this chapter is limited to fundamental considerations such as choosing a BASIC language statement for program control of an interfaced device, and using an appropriate address code for a particular statement. For the information to be completely meaningful, readers should be familiar with the Wang system being used in conjunction with an 8-bit-parallel I/O Interface Controller.

#### 2.2 DEVICE ADDRESS CODES

Since Wang systems, especially the larger ones, can be configured with several input and output devices, it is usually necessary to identify the particular device to which or from which data is to be transferred. When specifying a device for an I/O operation, the BASIC syntax requires a three-hexdigit (12-bit) code of the form xyy, where

- x, the "device type" digit, usually determines which microcode routines are accessed by the system during execution of the BASIC statement, and

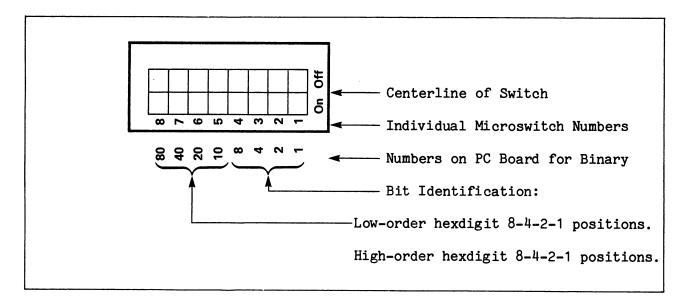

- . yy, the "preset address" digits, represent the hexadecimal equivalent of a binary value corresponding to the setting on a device controller's 8-pole address switch.

To ensure address uniqueness for the devices in a particular system, a Wang Customer Engineer sets the address switches in conformity with a standard list when installing a system initially or adding equipment to an existing system. As indicated in Table 2-1, an Option 67 or a Model 2250 I/O Interface Controller is installed with its address switch set to correspond to the hexadecimal value 3A, i.e., the binary value 00111010. A second Model 2250 controller is installed with its address switch set to hex 3C, i.e., 00111100; a third such controller is installed with its switch set to hex 3E, i.e., 00111110.

Although an I/O Interface Controller's address switch is set to an even address (low-order bit "0"), only the seven high-order bits in an address code must match the switch setting in order to enable the controller. Thus, an odd address which differs only in the low-order bit position also enables the controller. (See Table 2-1.)

The choice of an even or odd address affects which signal is made available to the CPU on the controller's  $\overline{\text{RB}}$  (Ready/Busy) line. The even address makes the  $\overline{\text{IRB}}$  (Input Buffer Ready/Busy) level available to the CPU; the odd address makes the  $\overline{\text{RBI}}$  (External Device Ready/Busy) level available to the CPU. For some BASIC statements, only an even or an odd address can be used; for other statements, the choice is optional and should be based upon the characteristics of the interfaced device. Furthermore, for any statement which does not check the  $\overline{\text{RB}}$ -line during execution, the choice is immaterial. Therefore, Section 2.4 provides brief descriptions of several BASIC language statements which may prove useful for control of non-Wang devices, and includes information about the appropriate address codes for input and output operations via an 8-bit-parallel I/O Interface Controller.

| Switch<br>Setting | Corresponding<br>Addresses* | Remarks                                                                                                                                   |

|-------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 3 <b>A</b>        | Even: x3A<br>Odd: x3B       | Standard for the Option 67 controller and for one Model 2250 controller (whether one or more such controllers are installed in a system). |

| 3C                | Even: x3C<br>Odd: x3D       | For a second Model 2250 controller in one system.                                                                                         |

| 3E                | Even: x3E<br>Odd: x3F       | For a third Model 2250 controller in one system.                                                                                          |

Table 2-1. I/O Interface Controller Addresses

#### 2.3 DEVICE SELECTION

When a Wang system is Master Initialized (power turned off and then on), "primary devices" are automatically selected for the eight classes (groups) of I/O operations identified by the SELECT statement I/O-class parameters CI (console input), CO (console output), INPUT, PRINT, LIST, TAPE, DISK, and PLOT. To be a primary device, a device must be plugged into a controller whose address code is one of the five default addresses for the system. For example, the keyboard whose controller is preset with the address O1 is a primary device since the address code O01 is selected automatically during master initialization for all subsequent operations governed by the parameters

<sup>\*</sup> Recommended or required values for the x-digit are included in the descriptions of BASIC statements in Section 2.4.

CI and INPUT. Similarly, the CRT display unit whose controller is preset with the address 05 is a primary device since the address code 005 is selected automatically for all subsequent operations governed by the parameters CO, PRINT, and LIST. The disk or diskette drive corresponding to address code 310 is a primary device. The other default addresses are 10A (for the operations in the I/O-class TAPE) and 413 (for the I/O-class PLOT).

Anyone writing an application program for an interfaced device plugged into an 8-bit-parallel I/O Interface Controller must remember that the device is not a primary device. Hence, to access an interfaced device for an input or output operation, the appropriate even or odd address code of the controller must be specified in at least one of the following ways:

- a) directly (using a three-hexdigit address) or indirectly (using a file number) in any BASIC statement whose syntax permits address specification, or

- b) in a SELECT statement containing the I/O-class parameter governing the operation, e.g., SELECT INPUT 23A assigns the code 23A to the I/O-class parameter INPUT which governs all subsequent INPUT and KEYIN operations.

#### NOTE:

When an optional address is omitted in a BASIC statement, the default address is the address last selected for the I/O-class parameter associated with the operation (or the "primary" address if no selection is made after master initializing the system).

#### 2.4 CHOOSING BASIC STATEMENTS

Generally speaking, several BASIC language I/O statements are feasible for program control of non-Wang devices interfaced to Wang systems via 8-bit-parallel I/O Interface Controllers. Brief descriptions of the statements, appropriate address codes, and any special wiring considerations are summarized for input operations in Table 2-2 and for output operations in Table 2-3. More detailed descriptions for the statements are given in Appendices A and B.

Table 2-2. Input Operations

| Statement   | Description, Address Code, and Wiring Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT       | Suitable for devices not requiring initialization signals. Receives ASCII data for storage in one or more numeric and/or alphanumeric variables if the incoming data stream is properly interspersed with commas and carriage return characters serving as data separators. Since the statement does not check the controller's RB-line, either the even or odd address with device type code 0 or 2 (23A, 23B, 03A, or 03B) is appropriate. (See Appendix A.)                                                                                                                                                                                           |

| MAT INPUT   | Similar to INPUT, except receives ASCII data for storage in one or more numeric or alphanumeric arrays.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DATALOAD BT | Provides one initialization strobe with a special 8-bit code which can be used or ignored by the device. Receives any 8-bit formatted character codes (or discrete binary data) by providing one request strobe per input character when the CPU via the controller senses RBI on Pin 19 is Hi; however, for devices not requiring request strobes, Pin 19 can be left open so RBI remains continuously Hi (Ready). Since the statement is designed to check the RBI level, the controller's odd address must be used; furthermore, Wang Laboratories supports only device type code 6 (e.g., 63B) in conjunction with the controller. (See Appendix A.) |

| KEYIN       | Suitable for reception of a single-character "handshaking" message, e.g., ACK, ENQ, NAK. Also, if programmed in a loop, suitable for character-by-character reception from relatively slow or intermittent devices. Usually, the even address with device type 0 or 2 is preferred (23A or 03A); however, the odd address (23B or 03B) may be used for a device designed to supply its own ready/busy signal. (See Appendix A.)                                                                                                                                                                                                                          |

| \$GIO       | Suitable for customizing an input (or output) operation. Particularly useful for devices not easily controlled by BASIC statements having built-in signal sequences. Device type 0 is preferred for all \$GIO operations. The controller's odd address should be used for operations whose microcommands include "WR", i.e., CPU awaits enabled device ready signal. (See Appendix C.)                                                                                                                                                                                                                                                                   |

Table 2-3. Output Operations

| 1           | Table 2-3. Output Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Statement   | Description and Appropriate Address Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PRINT       | Outputs the data currently stored in the specified numeric or alphanumeric variables, data specified via HEX functions, and also space characters if necessary to achieve any column positioning specified via TAB functions. Automatically inserts any space characters necessary to achieve zoned, packed, or mixed formats, as specified by the commas and semicolons appearing between arguments in the argument list. Also inserts any carriage return characters necessary to satisfy the currently effective line length, and supplies either a line feed or null character after each carriage return, depending upon the device type code currently in effect for the operation (see Table 2-4). The controller's odd address with device type 0, 2 or 4 should be used. (See Appendix B.) |

| PRINTUSING  | Outputs data and interspersed text, as specified in the referenced image (%) statement. The controller's odd address with device type 0, 2 or 4 should be used (see Table 2-4). (Also, see Appendix B.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MAT PRINT   | Similar to PRINT, except the argument list can specify numeric and alphanumeric arrays as the source of data to be output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HEXPRINT    | Outputs the hexadecimal notation for each byte of data (including any trailing space characters) currently stored in the specified alphanumeric variables and arrays. Data representing individual elements of an array is not separated at element boundaries; however, carriage return characters are inserted, as necessary, to satisfy the currently effective line length. Furthermore, data representing successive arguments in the argument list is not separated if semicolons are used in the list. On the other hand, if a comma separates a pair of arguments, a carriage return is inserted to indicate where one argument ends and the next one begins. The controller's odd address with device type 0, 2 or 4 should be used (see Table 2-4). (Also, see Appendix B.)               |

| DATASAVE BT | Outputs data without inserting any special characters to separate the values currently stored in the elements of the specified alphanumeric array. Suitable for transmitting a long data stream with no limit on the number of characters, other than the limit imposed on the specified array by the storage capacity of the CPU. Any 8-bit codes, EIA codes, or packed BCD codes stored in the alphanumeric array can be transmitted from the CPU to the controller. The controller's odd address with device type 4 must be used. (See Appendix B.)                                                                                                                                                                                                                                              |

| \$GIO       | Suitable for customizing an output (or input) operation. Particularly useful for devices not easily controlled by BASIC statements having built-in signal sequences. Device type 0 is preferred for all \$GIO operations. The controller's odd address should be used for operations whose microcommands include "WR", i.e., CPU awaits enabled device ready signal. (See Appendix C.)                                                                                                                                                                                                                                                                                                                                                                                                              |

Table 2-4. Effect of the Device Type Code on PRINT, PRINTUSING, and HEXPRINT Statements

| Code | CPU Action                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Supplies a line feed (LF) character automatically after each system-generated carriage return (CR) character. Therefore, device type "O" is appropriate for an output operation to a device which does not supply its own LF character after receiving a CR character.                                                                                                                                               |

| 2    | Supplies a null character, (00) <sub>16</sub> , automatically after each system-generated CR. Therefore, device type "2" is appropriate for an output operation to a device which supplies its own LF after receiving a CR.                                                                                                                                                                                          |

| 14   | Suppresses the character count during an output operation and thereby suppresses any CR normally generated when the character count equals the currently selected line length for the output operation. Supplies a LF after any other system-generated CR. Therefore, device type "4" is appropriate for an output operation to a printer which supplies its own CR/LF when the physical carriage width is exceeded. |

#### APPENDIX A

BUILT-IN SIGNAL SEQUENCES FOR DATALOAD BT, INPUT, AND KEYIN

#### DATALOAD BT Sequence

If the controller's odd address with device type code 6 is specified, the DATALOAD BT sequence includes the following actions:

1. Enable

The CPU strobes an 8-bit address to the I/O bus to enable the controller. (Address specification is optional in a DATALOAD BT statement. Priority is given to the specified address, if any; otherwise, the address currently selected for the I/O-class parameter TAPE is used.)

2. Test device ready

The CPU tests the  $\overline{RB}$ -line and waits until  $\overline{RBI}$  is Hi. (Therefore, the odd address is necessary to make the  $\overline{RBI}$  level available to the CPU on the controller's  $\overline{RB}$ -line.)

3. Output initialization strobe

The CPU sends an initialization character to the controller's Data Output Buffer via an  $\overline{OBS}$  strobe. Then, the controller generates an  $\overline{OBS}_0$  strobe on Pin 31 and provides eight data levels on Pins 20 through 27. Specifically, a character (x1)<sub>16</sub> is provided if the parameter R is specified; otherwise, (x0)<sub>16</sub> is sent. However, in either case, the value of x is indeterminate. (If the interfaced device does not require an initialization character, the strobe can be ignored.)

4. Test device ready

Again, the CPU tests the  $\overline{RB}$ -line and waits until  $\overline{RBI}$  is Hi.

5. Set CPU ready

The CPU sets  $\overline{\text{CPB}}$  Hi, which also sets  $\overline{\text{CPB}}_0$  Hi, thereby ensuring that a received character is strobed into the CPU and not held in the controller's Input Buffer.

6. Output request strobe

The CPU/controller generates a character request strobe  $\overline{\text{CBS}}_0$  on Pin 16 which may be used to initiate an  $\overline{\text{IBS}}_1$  strobe and eight data levels from the device; however, the  $\overline{\text{CBS}}_0$  strobe can be ignored by a device not requiring a request strobe, and the  $\overline{\text{CPB}}_0$  level on Pin 32 can be used to initiate/inhibit  $\overline{\text{IBS}}_1$ .

7. Receive a character

Within 4  $\mu$ s of the leading edge of an  $\overline{\text{IBS}}_{\text{I}}$  strobe, the controller strobes the eight levels on Pins 1 through 8 into the CPU and sets  $\overline{\text{CPB}}_{\text{O}}$  Lo. Alternatively, if appropriate for a device, the  $\overline{\text{CBS}}_{\text{O}}$  strobe on Pin 16 can be used in lieu of  $\overline{\text{IBS}}_{\text{I}}$  by wiring Pin 16 to Pin 9.

8. Receive remaining characters

Steps 4 through 7 are repeated until any one of the following conditions occurs:

- the N parameter (denoting the number of characters to be received) is satisfied, if specified, or

- . the S parameter (denoting a stop/termination code) is satisfied, if specified, or

- . the specified receiving variable or array becomes full.

- 9. Disable

The CPU disables the controller and advances program execution to the next statement.

#### INPUT Sequence

The INPUT sequence includes the following actions:

- 1. Prompt The CPU enables the currently selected CO (console output) device to send the literal string message, if any, and a question mark (plus a space character) to indicate the system is awaiting input.

- 2. Enable The CPU strobes an 8-bit address to the I/O bus to enable the controller. (Since the INPUT syntax does not permit address specification, the address currently selected for the I/O-class parameter INPUT is used.)

- 3. Set ready The CPU sets  $\overline{\text{CPB}}$  Hi, which also sets  $\overline{\text{CPB}}_{0}$  Hi, thereby indicating the system is ready to receive an  $\overline{\text{IBS}}_{1}$  strobe from the interfaced device.

- 4. Receive input strobe The controller awaits an  $\overline{\text{IBS}}_{T}$  strobe on Pin 9 and eight levels on Pins 1 through 8, representing one character in 8-bit parallel format. (The system waits indefinitely if no strobe is received.)

- 5. Receive one character Within  $4\,\mu$ s of the leading edge of an  $\overline{\text{IBS}}_{T}$  strobe, the character controller strobes the 8-bit character directly into the CPU, and also sets  $\overline{\text{CPB}}_{O}$  Lo. (The  $\overline{\text{ENDI}}$  level is also strobed into the CPU since provision is made in the INPUT statement to handle input via a special function key which automatically sets  $\overline{\text{ENDI}}$  Lo.)

6. Temporarily disable

The CPU temporarily disables the controller for echo and character processing as follows (assuming ENDI is Hi):

- . The received character is compared with a special character list, where (08) or (5F) for represents a backspace instruction which effectively removes the previously received character, and (5C) for represents a line erase instruction which effectively removes all currently buffered received characters; none of these codes is stored in the buffer.

- . A received  $(00)_{16}$  or  $(7F)_{16}$  code is not stored.

- . Any code above  $(7F)_{16}$  may cause unpredictable action.

- . An (OD)<sub>16</sub> carriage-return code is stored, but interrupts reception, as described in Step 9.

- . Otherwise, the received character is stored in the CPU buffer, and the character count is incremented by one.

- 7. Echo the character

The CPU enables the currently selected CO (console output) device and sends a duplicate (an echo) of the buffered character, or any backspace or line erase action which occurs.

8. Receive subsequent characters

Steps 2 through 7 are repeated until an  $(0D)_{16}$  is stored in the CPU buffer, or the character count reaches a system-related value (e.g., 191 for a 2200T central processor), whichever occurs first. If the count reaches the maximum value without an  $(0D)_{16}$ , the CPU disables the controller, enables the CO device to send an ERR 45 code, ignores the currently buffered data, resets the character count to zero, and returns to Step 2.

9. Process buffered characters

Upon receipt of an (OD) character, the CPU processes any currently buffered characters for storage in the receiving variables specified in the INPUT statement argument list; the procedure includes the following actions:

- . If no data precedes the (OD) 16, statement execution ends.

- . Otherwise, the buffer is searched for a data separator comma, (2C)<sub>16</sub>, i.e., a comma not embedded in data delimited by double or single quotation mark codes, (22)<sub>16</sub> or (27)<sub>16</sub>.

(continued on next page)

- . If a data separator comma is located, the current position of the argument list pointer is checked to determine which variable is to receive the data preceding the comma (or preceding the carriage return character if no other data separator is found).

- . If the currently flagged receiving variable is numeric, a data validity check is made. If any illegal character is found, an ERR 29 code is sent to the CO device, the data currently being processed (and all remaining buffered data) is ignored, the argument list pointer does not move, and execution returns to Step 2. Otherwise, the data is converted to Wang's internal numeric format and stored in the receiving variable; then, the argument list pointer moves to the next receiving variable.

- If the currently flagged receiving variable is alphanumeric, data is transferred to character-by-character until the allocated storage area is filled, or the data separator is reached. Any excess characters are ignored; trailing space characters, (20)<sub>16</sub>, are automatically supplied if the storage area is not filled by the received Similarly, if a string function (STR) is in the currently flagged argument list position, data is transferred only to the designated byte positions (excess characters are ignored or trailing space characters added). If the buffered data being transferred is delimited by single quotation marks, any uppercase codes are converted to lowercase before storage. When data transfer to the flagged variable is completed, the argument list pointer moves to the next receiving variable.

- The buffer is searched for the next data separator comma if the previously transferred data was delimited by a comma. If a comma is found, the data transfer cycle is repeated, as described, depending upon the nature of the next receiving variable. The process continues until no receiving variables remain, or the (OD) character is reached.

- 10. Receive other characters

- If the  $(0D)_{16}$  code has been reached, but another receiving variable remains, Steps 2 through 9 are repeated until the last variable is reached, or an  $(0D)_{16}$  is received with no other data.

- 11. Disable

- After data is transferred to the last receiving variable, or a carriage-return without data is encountered, the CPU disables the controller and moves to the next statement in the program.

#### Echo Suppression

If desired, the INPUT-data-echo normally displayed on the CRT screen can be suppressed by programming techniques. For example, <u>assume</u> the following:

- a) The CRT echo of INPUT-data is undesirable for an application requiring a particular CRT display to remain undisturbed while data is being read from an external device.

- b) The external device is an input-only device not wired to receive output from the CPU via the controller; Pin 19, RBI, is open (Hi = logic "0" = Ready).

- c) The external device is plugged into an 8-bit-parallel I/O Interface Controller whose address switch is set to 3A. (See Table 2-1.)

Now, consider the following programming technique. Whenever the input address of the controller is selected for execution of one or more INPUT statements, select the output address of the controller for CO-class operations. By this technique, the INPUT-data-echo is sent to the output buffer on the controller rather than to the CRT screen. However, since the external device is an input-only device with respect to the CPU and controller (by our assumption), the echo characters are ignored. The following program demonstrates the technique of echo suppression:

| Statements                  | Comments                                                                                                               |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| 10 DIM A\$(100)35           | Dimension the A\$-array: 100 elements with a maximum of 35 characters per element.                                     |

| 20 SELECT INPUT 23A, CO 23B | Select the controller for subsequent INPUT-class and CO-class operations (23B can be assigned to the INPUT parameter). |

| 30 FOR J=1 TO 100           | Set up a FOR-NEXT loop to execute Line 40 repeatedly.                                                                  |

| 40 INPUT A\$(J)             | Receive data and store in the Jth element of the A\$-array.                                                            |

| 50 NEXT J                   | Increment J and loop.                                                                                                  |

| 60 SELECT INPUT 001, CO 005 | Reselect the keyboard for INPUT-class operations and the CRT for CO-class operations.                                  |

#### NOTES:

- 1. The programming technique illustrated by Line 20 is not suitable for echo suppression if the external device receives and responds to data sent from the CPU via the controller.

- 2. When assigning an address, other than the CRT address, to the CO-parameter in a SELECT statement to suppress the CRT INPUT-data-echo, do not assign a nonexistent device address to the CO-parameter. If such an address is used, the system locks out when the program is run with no controller matching the address. To regain control, the operator must Master Initialize the system which clears all memory.

- 3. If desired, assign the address of the Line Printer (usually 215) or the Output Writer (usually 211) to the CO-parameter in the SELECT statement, and thereby obtain a hardcopy of the INPUT-data-echo.

- 4. Always include a program statement reselecting the CRT (usually code 005) for CO-class operations, as illustrated in Line 60. Then, when program execution is complete, the CRT displays the system-generated colon which is sent automatically to the CO-device to indicate return of system control to the CI (console input) device.

#### KEYIN Sequence

The KEYIN sequence includes the following actions:

- 1. IBS received/not received

- The interfaced device can send an  $\overline{\text{IBS}}_{1}$  strobe on Pin 9, eight levels on Pins 1 through 8, and an optional  $\overline{\text{ENDI}}_{1}$  level on Pin 11 at any time, without checking  $\overline{\text{CPB}}_{0}$  on Pin 32. However, unless the device checks  $\overline{\text{IRB}}$  on Pin 17, a character may be overwritten and thereby lost before its transfer to the CPU occurs.

- 2. Enable

- The CPU strobes an 8-bit address to the I/O bus to enable the controller. (Since the KEYIN syntax does not permit address specification, the address currently selected for the I/O-class parameter INPUT is used.)

- 3. Test for character

- The CPU tests the controller's  $\overline{RB}$ -level, which is either the  $\overline{IRB}$  level on Pin 17 (if the address is even) or the  $\overline{RBI}$  level on Pin 19 (if the address is odd).

4. If  $\overline{RB} = Hi^*$

The CPU disables the controller, terminates the KEYIN operation, and advances program execution to the next statement.

5. If  $\overline{RB} = Lo^{*}$

The procedure is as follows:

- . The CPU sets  $\overline{\text{CPB}}$  Hi, which also sets  $\overline{\text{CPB}}_{\text{O}}$  Hi.

- . The controller then strobes the eight Input Buffer levels and the  $\overline{\text{ENDI}}$  level into the CPU.

- . The CPU disables the controller, stores the 8-bits of data (one byte) in the specified alpha variable, and then executes a program branch as follows:

- . to the first specified line number if  $\overline{\text{ENDI}}$  is Hi, or

- . to the second specified line number if  $\overline{\mathtt{ENDI}}$  is Lo.

- \* With an even address in Step 3,

RB is { Hi, logic "0" } when IRB on Pin 17 is { Hi, logic "0", buffer empty }; Lo, logic "1" } Lo, logic "1", buffer full }

alternatively, with an odd address in Step 3,

$\overline{\text{RB}}$  is  $\{\text{Hi, logic "0"}\}\$  when  $\overline{\text{RBI}}$  on Pin 19 is  $\{\text{Lo, logic "1"}, \text{ device busy }\}$ .

Note that the Pin 19 logic, as seen by the CPU on the  $\overline{\text{RB}}$ -line, is inverted if an odd address is used for a KEYIN operation. For many applications suited to the KEYIN statement, the even address is preferred; however, the odd address may be used to control input from a device designed to supply its own ready/busy signal.

The following program can be used to demonstrate the conditional branches of the KEYIN statement. In the program, line 20 is executed repeatedly by an endless loop. Each time no character is found in the keyboard controller buffer, the line 30 message is displayed. However, touching alpha or numeric keys on the keyboard produces the line 50 message, while touching special function keys produces the line 70 message.

#### Statements

#### Remarks

Dimension A\$ for one character.

Scan the keyboard for input.

- 10 DIM A\$1

- 20 KEYIN A\$, 50, 70

- 30 PRINT "\*\*\*\*\*

- 40 GOTO 20

- 50 PRINT "---50---"

- 60 GOTO 20

- 70 PRINT "S.F. KEY"

- 80 GOTO 20

- By including the following line:

- 15 SELECT INPUT xyz

where xyz is replaced by the input address of an I/O Interface Controller, the program above can be used to demonstrate KEYIN operations for an external device plugged into the controller.

#### APPENDIX B

BUILT-IN SIGNAL SEQUENCES FOR PRINT, PRINTUSING, HEXPRINT, AND DATASAVE BT

The built-in signal sequences for PRINT, HEXPRINT, and DATASAVE BT statements are essentially the same. The sequences described here assume that the device controller currently selected for any one of these operations is an I/O Interface Controller whose odd address is assigned to the I/O-class parameter governing the particular operation (or specified in a DATASAVE BT statement).

Two sequences are described here:

- 1) a "normal" output sequence and

- 2) an "acknowledge" output sequence.

The normal output sequence occurs if a Ready/Busy level  $\overline{\text{RBI}}$  is supplied by the external device on Pin 19 of the connector. The acknowledge output sequence occurs if the  $\overline{\text{DORB}}$  level on Pin 28 is connected to Pin 19 for applications where an external device requires output "strobes" longer than the  $5\mu s$  strobe normally supplied by the CPU/controller; in such cases, the external device supplies an  $\overline{\text{ACK}}$  strobe via Pin 18 rather than an  $\overline{\text{RBI}}$  level on Pin 19.

The normal output sequence is as follows:

- 1. Enable The CPU strobes the 8-bit address code to the I/O bus to enable the controller. When enabled with its odd address, the controller makes the  $\overline{\text{RBI}}$  level on Pin 19 available to the CPU on the  $\overline{\text{RB}}$ -line to test the external device Ready/Busy level.

- 2. Test ready If the RBI level on Pin 19 is Lo (logic "1", Busy), the CPU continues a test loop until a Hi level is sensed.

- 3. Output one character When  $\overline{\text{RBI}}$  on Pin 19 becomes Hi (logic "O", Ready), the CPU strobes an 8-bit character into the Data Output Buffer on the controller. The controller then makes eight parallel data levels (corresponding to the character) available on Pins 20 through 27 and makes a  $5\mu$ s  $\overline{\text{OBS}}_0$  strobe available on Pin 31. Although the controller also sets the  $\overline{\text{DORB}}$  level on Pin 28 to Lo (logic "1", Full),  $\overline{\text{DORB}}$  is not utilized in the normal sequence.

- 4. Hold Upon receipt of the  $\overline{\text{OBS}}_0$  strobe, the external device sets the  $\overline{\text{RBI}}$  level on Pin 19 to Lo (logic "1", Busy). The  $\overline{\text{RBI}}$  level remains Lo while the external device is processing the character. When processing is complete, the external device resets  $\overline{\text{RBI}}$  to Hi.

- 5. Output Steps 2, 3, and 4 are repeated if the previous character is successive not the final character of the output operation. (A ready characters test is not made after the final character is output.)

- 6. Disable The CPU disables the controller and program execution advances to the next statement.

The acknowledge output sequence is as follows:

- 1. Enable The CPU strobes the 8-bit address code to the I/O bus to enable the controller. When enabled with its odd address, the controller makes the RBI level on Pin 19 available to the CPU on the RB-line to test the external device Ready/Busy level. However, since Pin 28 is tied to Pin 19 (rather than using an external device ready/busy level), the

- CPU effectively tests the  $\overline{DORB}$  level. Initially,  $\overline{DORB}$  = Hi (logic "0", Empty); therefore,  $\overline{RBI}$  = Hi (logic "0", Ready).

- 2. Test ready Whenever the level on Pin 19 is Lo (logic "1", Busy), the CPU continues a test loop until a Hi level is sensed.

- 3. Output one character When the level on Pin 19 becomes Hi (logic "0", Ready), the CPU strobes an 8-bit character into the Data Output Buffer on the controller. The controller makes the eight data levels available on Pins 20 through 27 and sets the  $\overline{\text{DORB}}$  level on Pin 28 to Lo (logic "1", Full). (The controller also provides a  $5\mu$ s  $\overline{\text{OBS}}_0$  strobe on Pin 31; however, the strobe need not be utilized by the external device.)

- 4. Hold The  $\overline{DORB}$  level on Pin 28 remains Lo while the external device is receiving and processing the data levels. Since Pin 28 is tied to Pin 19, the  $\overline{RBI}$  level is also Lo. When processing is complete, the external device sends an acknowledge strobe.

- 5. Receive When the external device sends an  $\overline{ACK}$  strobe on Pin 18, the acknowledge controller resets the  $\overline{DORB}$  level on Pin 28 to Hi (logic "O", strobe Empty). Thus, the  $\overline{RBI}$  level on Pin 19 is reset to Hi.

- 6. Output Steps 2 through 5 are repeated if the previous character is successive not the final character of the output operation. (A ready characters test is not made after the final character is output.)

- 7. Disable The CPU disables the controller and program execution advances to the next statement.

## NOTE:

In Step 5 of the normal output sequence and Step 6 of the acknowledge output sequence, several system-generated characters may occur in addition to the data corresponding to the argument list of the particular BASIC statement being executed. See Tables 2-3 and 2-4.

#### APPENDIX C

## CUSTOMIZED SIGNAL SEQUENCES FOR I/O OPERATIONS

In contrast to the statements with built-in signal sequences, the \$GIO (i.e., the General Input/Output) statement fits into the framework of the high-level BASIC language, yet provides the capability to customize input and output operations by a technique similar to machine-language programming. Effectively, the user tailors a signal sequence to the specifications of a particular input or output device by choosing one or more microcommands to define the desired input or output operation.