# PERFORMACE SPECIFICATIONS AND DESIGN NOTES ON THE

2200 MVP 5 1/4" DISK POWER SUPPLY

HM- 75

Donald Paradis

Original release: June 20, 1983 Last update: June 20, 1983

# TABLE OF CONTENTS

|         |    |                           | 1 | Page |

|---------|----|---------------------------|---|------|

| Section | 1. | Performace Specifications |   | 3    |

| Section | 2. | Specification Definitions |   | 4    |

| Section | 3. | Design Notes              | • | 9    |

| Section | 4. | Temperature Measurements  |   | 12   |

# (1). PERFORMACE SPECIFICATIONS

# +5V SUPPLY

Load regulation .8% or less (measured at logic bd.) .015% or less (measured at power supply bd.) Load regulation Line regulation less than .002% Ripple and noise less than 4 mV peak to peak. Load transient response less than 40 usec. Minimum adjustment range .65 V. Worst case adj. ranges refer to pg. 6 Max. cont. output current\* 8.5 amps. Current liminting 10A to 12.25A Typical A.C. dropout 93 Vac +12V crosstalk 20 mV peak to peak Over-voltage protection none

### +12V SUPPLY

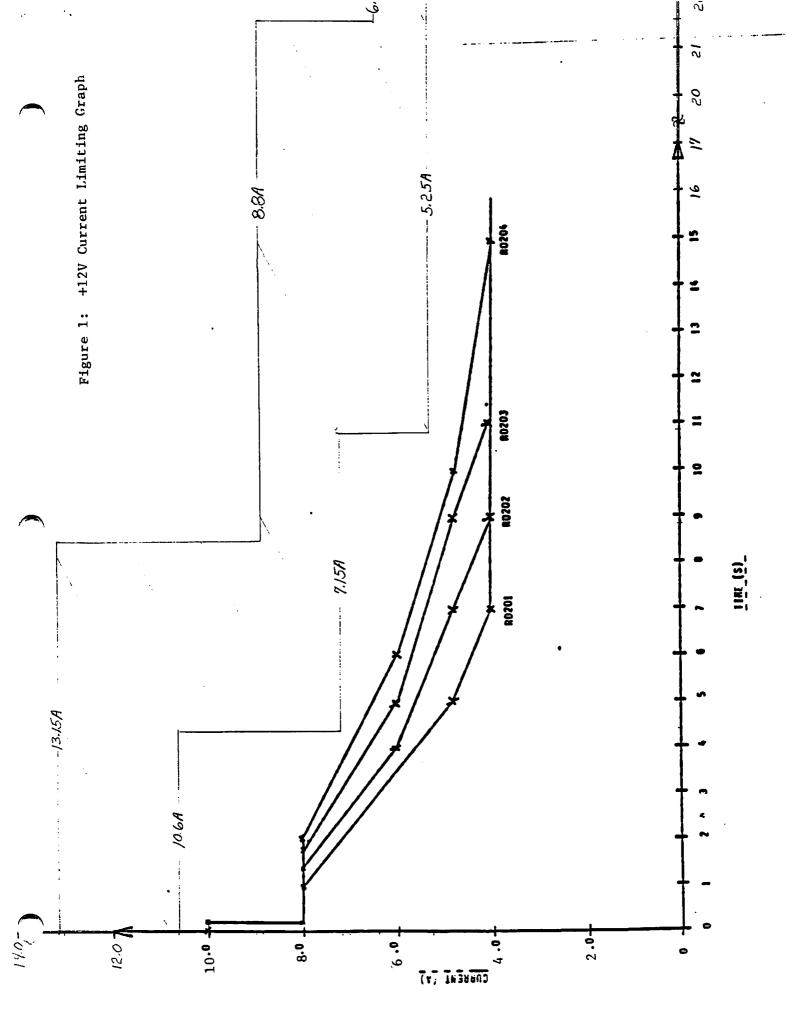

.5% or less (measured at furthest drive) Load regulation Load regulation .015% (measured at power supply bd.) Line regulation less than .002% less than 6 mV peak to peak. Ripple and noise less than 40 usec. Load transient response Minimum adjustment range 1.5V refer to pg. 6 Worst case adj. ranges Max cont. output current\* 4.25A Current lim. 0 to 6 secs. 10.6 to 13.15A refer to pg. 7 Current lim. 6 to 15 secs. 7.15 to 8.8A ti Current lim. after 15 secs. 5.25 to 6.4A Typical A.C. dropout 93 Vac +5V crosstalk 20 mV peak to peak V Over voltage protection none

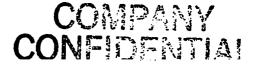

# +16V UNREGULATED SUPPLY

Max. cont. current (average) .65A

Nominal output voltage at 115 Vac; with both supplies fully loaded: 20 Vdc

# -16V UNREGULATED SUPPLY

Max. cont. current (average) .65A

Nominal output voltage at 115 Vac; with both supplies fully loaded: 18 Vdc

# A.C. INPUT

115V Operation 98Vac to 128Vac 2.0A max @ 128 Vac 230V operation 196Vac to 256Vac 1.0A max @ 256 Vac

OPERATING AMBIENT TEMPERATURE RANGE 50' F to 120' F ( supply is equipped with a thermal protection switch )

\* Requires forced air cooling.

# (2). SPECIFICATION DEFINITIONS

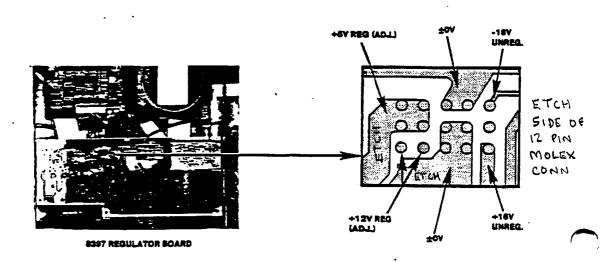

This section outlines the proper test procedures to be taken to determine the performace characteristics of the 8397. To meet the specifications as stated in section 1 these measurement procedures must be adhered to. Additionally, the specifications presented are based on the actual system configuration. Any alteration of component placement or wiring may affect certain parameters.

Only the maximum current drain is defined for the +16V and -16V supplies, because these supplies are unregulated.

LOAD REGULATION: The following formula shall be used to determine load regulation.

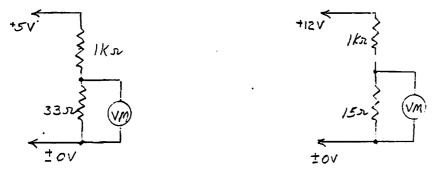

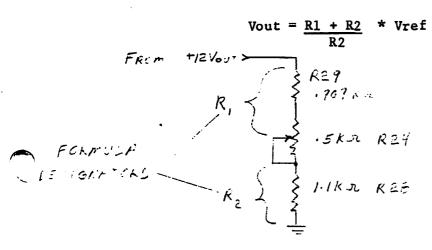

Due to the small differences between no load and full load voltages, a resistor voltage divider network had to be utilized in order to obtain more accurate measurements. The measuring instrument used was a 4 1/2 digit digital voltmeter set on the 200 mv. range. The voltage dividers required are illustrated below.

Note that all voltage readings should be taken quickly to minimize thermal effects.

Additionally, all specifications listed in section 1 are based on using new connectors which have not had more than 10 insertion cycles.

Load regulation was tested at two different locations for both the +5V supply and the +12V supply. The measurement points for the +5V supply were at the back side of the connector on the main logic board and at the back side of the output connector on the 8397 regulator board. Typical regulation figures as measured at the logic board are approximately .65%; the supply is specified at .8% or less. The load change used was from 0 amp to 4.25 amps. Typical regulation figures as measured at the regulator board are approximately .01%; the supply is specified at .015% or less. The load change used was from 0 amp to 8.5 amps.

The measurement points for the +12V supply were at the back side of the power connector on the disc drive located furthest from the regulator board, and at the back side of the output connector on the 8397 regulator board. Typical regulation figures as measured at the disc drive are approximately .4%; the supply is specified at .5% or less. The load change used was from 0 amp to 2.25 amps. Typical regulation figures as measured at the regulator board are approximately .01%; the supply is specified at .015% or less. The load change used was from 0 amp to 4.0 amps.

# (2). SPECIFICATIONS DEFINITIONS

LINE REGULATION: Line regulation is to be calculated based on the following formula:

Line Reg. = change in D.C. output voltage \* 100% change in A.C. input voltage

The A.C. voltage is to be changed from 98 Vac to 128 Vac as measured at the A.C. plug that inserts into the VARIAC. Both of the supplies are to be continously loaded, the +12V supply should have a load of 4 amps and the +5V supply should have a load of 8.5 amps.

Again, due to the small voltage variations, the voltage dividers as outlined in the load regulation section must be used.

Typical line regulation figures for both the +12V and +5V supplies are approximately .0002%; the supply is specified at .002% or less.

RIPPLE AND NOISE: Ripple and noise is to be measured following the conditions listed below:

- 1. Both the +12V and +5V supplies are to be continously loaded using the following loads; +12V with a 4.0 amp load, +5V with a 8.5 amp load.

- 2. A 75 MHZ. or faster scope with a 'times' 1 probe is to be used to take measurements.

- 3. Measurement locations are the back side of the output connector on the regulator board.

- 4. A nominal line voltage of 115Vac is to used.

- 5. The scope's ground connection is to disconnected from the wall outlet and the ground connection shall be made via the ground connection at the probe end using a ground wire which is not more than 4 inches in length. To maintain adequate safety precautions the scope case should be grounded to the supplies ground via a separate wire incorporating a series resistor of 10 ohms.

LOAD TRANSIENT RESPONSE AND CROSSTALK: The typical response time for both supplies is approximately 20 micro-seconds; the supply is specified at 40 micro-seconds or less. The load step change for the +5V supply is from 5 amps to 8.5 amps while the step change for the +12V supply is from 2 amps to 4 amps.

Only one supply at a time is to be tested while the other supply has a continous maximum load as specified in section 1.

The response time is to measured from the moment the supplies output voltage changes to the time the output voltage reaches 5% of it's new steady state voltage. All measurement points are to be taken at the back side of the output connector on the 8397 board.

While one supply is being tested for transient response, the other supply can be monitored for the amount of induced crosstalk. The crosstalk figures indicated in section 1 do not include the normal ripple and noise voltage associated with the particular supply. Therefore, the total noise is the summation of the crootalk and the ripple & noise voltage.

# (2). SPECIFICATION DEFINITIONS

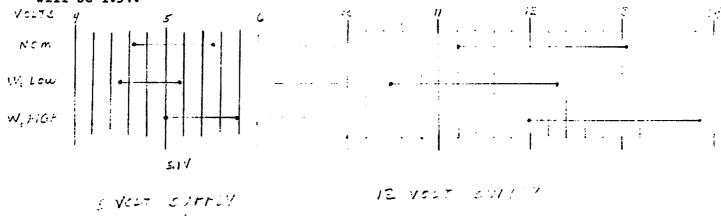

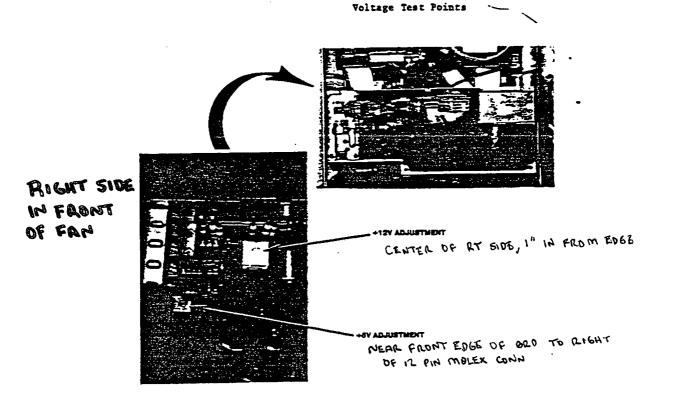

WORST CASE ADJUSTMENT RANGES: The following graphs best describe all possible worst case adjustment conditions which could exist regarding the supplies adjustment. From the graphs it can be deduced that the worst case range for the +5V supply will be at least .65V, while for the +12V supply it will be 1.5V.

MAXIMUM CONTINOUS OUTPUT CURRENT: The maximum load specifications as stated in section 1 are based on forced air cooling conditions. The supply can be operated continously at these loads with an input voltage of 128Vac, and at an ambient temperature of 120' F as long as the fan is functioning properly. In the event the fan becomes defective, the supply will shut down automatically once the internally equipped thermal switch reaches a temperature of 95 C +4 C.

After the thermal switch cools down to approximately 65 C the unit will power back up, assuming of course that the power switch is still in the on position.

If the fan is defective the unit will stay powered on for approximately 5 to 15 minutes before shuting down. The input line voltage, the ambient temperature, the system configuration (which manufacturer drives are installed), and the placement and orientation of the system all effect how long the unit will remain powered on should the fan die.

CURRENT LIMITING: The current limit specifications as outlined in section 1 desribe the load where the output voltage just begins to decrease, this point is more commonly referred to as the foldback knee. The +5V supply has a knee point of somewhere between 10 amps to 12.25 amps.

The +12V supply however is not so easily desribed, instead, a graph will be provided (on next page ) which will yield a clearer picture of the foldback characteristics. Actually, the supply cannot provide good regulation at the stated current level for the first initial six seconds, the current limiting is only set this high to allow for the high initial surge during start-up caused by the drives. The worst case condition occurs when two Rodime fixed drives (model R0204) are used.

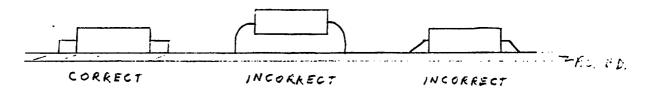

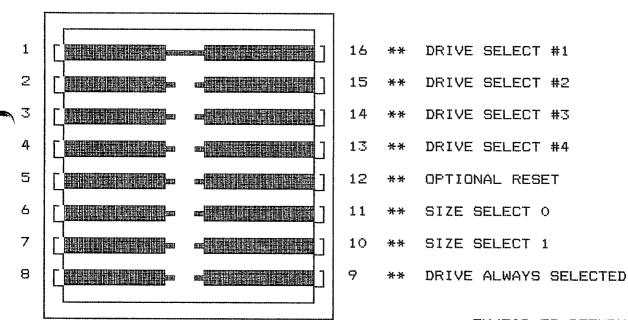

It's very important to realize that to meet these specifications as outlined in section 1; R2, and R3 must be properly mounted as illustrated in figure 2 (pg. 8). Don't be deceived, these resistors have very low resistance, and consequently the leads themselves contribute to the overall resistance.

# (2). SPECIFICATION DEFINITIONS

TYPICAL A.C. DROPOUT VOLTAGE: This is the input voltage at which the supplies output voltage has a total of 10 mv. (peak to peak) of ripple and noise. Both supplies are to be loaded at the respective maximum currents as defined in section 1. The typical dropout point for a new supply is approximately 93Vac. Even after 5 years the dropout voltage should not exceed 98Vac.

All A.C. voltage measurements are taken at the wall outlet.

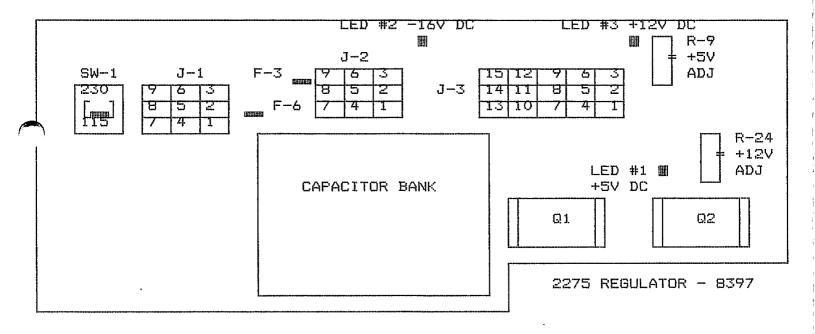

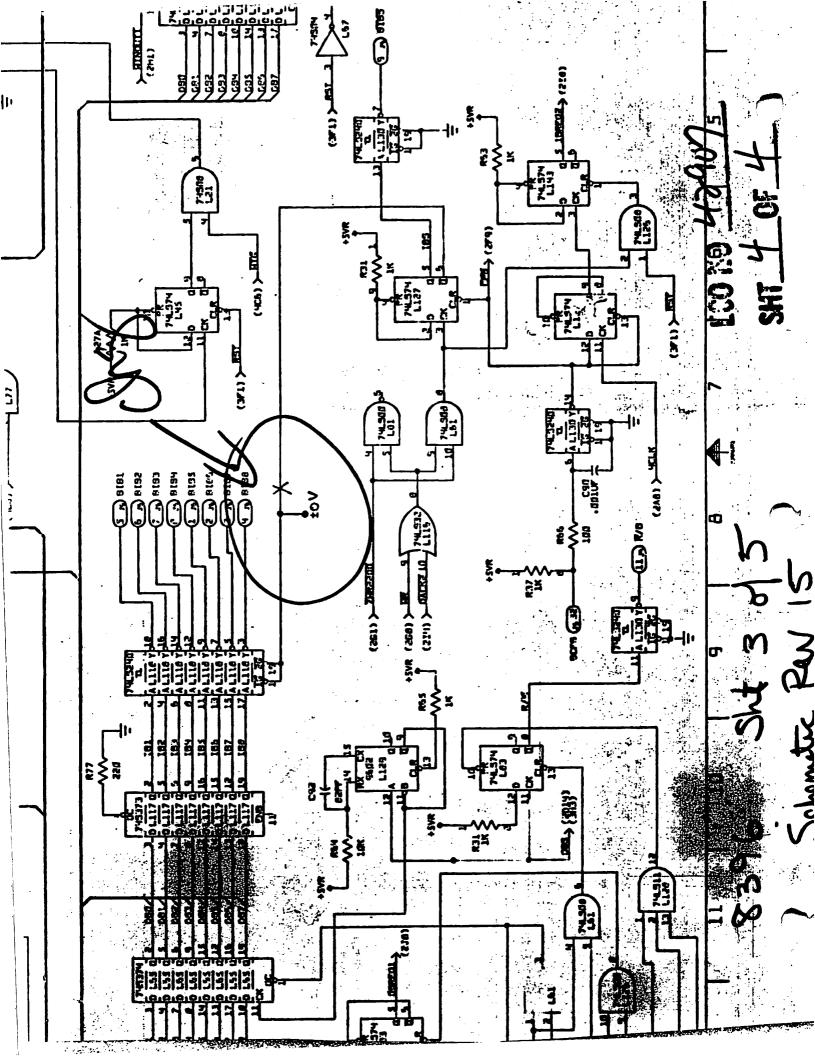

Figure 1: Proper and improper mounting arrangements for resistors R2 and R3.

# (3). DESIGN NOTES

The 8397 regulator board has many similarities to the 7770 regulator board. Therefore, to eliminate a duplication of effort reference should be made to hardware manual #56 ( H.M. 56 ). This manual provides ample information concerning component selection and alternative circuits.

Topics to be discussed in this particular manual will be restricted to significant differences between the 7770 and 8397 regulator boards or items which are unique only to the 8397 board.

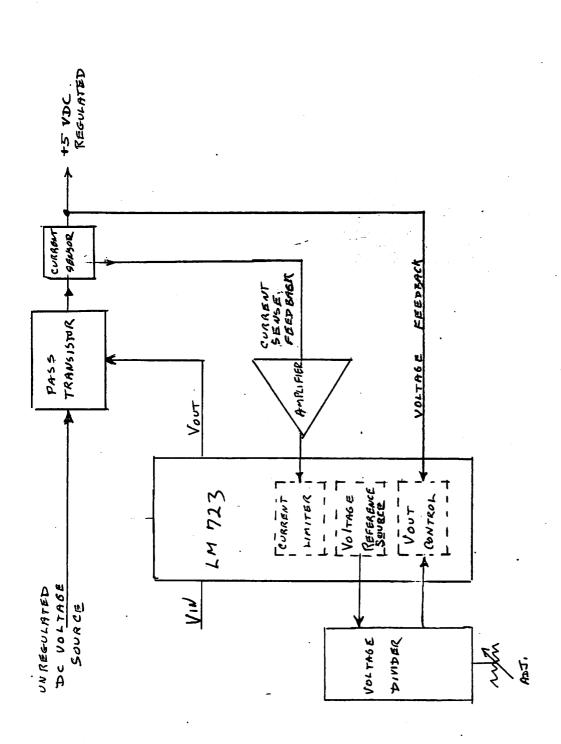

# +5V SUPPLY DESIGN NOTES

The +5V circuit incorporated on the 8397 board is virtually an exact duplicate of the one used on the 7770 board.

Significant differences include:

- 1. The addition of a 16K ohm resistor (R16) across R13. The purpose is to increase the output voltage by approximately .05V to compensate for the loses due to the power distribution cable. Recall that the 7770 board sensed the voltage at the load, in contrast to the 8397 board sensing the voltage at the power output connector.

- 2. The addition of a 470 ohm resistor (R10A) from L1 pin 3 to ground. This helps prevent hysteresis during current limiting foldback.

A hysteresis loop is when the external load must be significantly reduced beyond the point where foldback began in order for the supply to resume normal operation.

3. Instead of using a single 2210 ohm resistor from L1 pin 5 to ground; two resistors were utilized to form a voltage divider network to be used by the +12V foldback circuitry. The two resistors are 1.1K ohm ( R14 ) and 1.21K ohm ( R15 ). The +12V foldback circuitry will be more fully discussed at a later time.

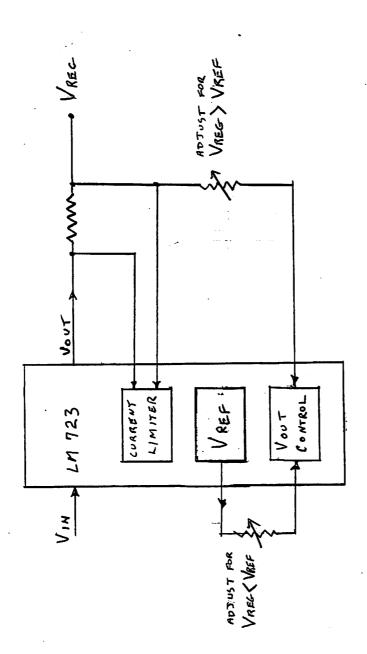

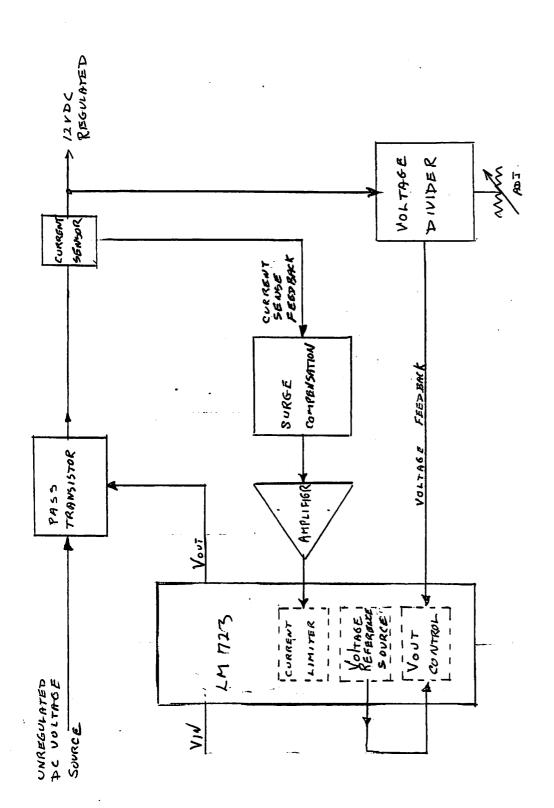

# +12V SUPPLY DESIGN NOTES

The configuration of the +12V supply is basically similar to the +5V supply. One major difference is the voltage divider network compromising R24, R28, and R29; instead of being connected to the non-inverting input of the 723 regulator the network is connected to the inverting input of the 723. This is necessary because the desired output voltage of +12V exceeds the 723's internal reference voltage (approx. 7.15V).

The formula for determining Vout and the actual resistor values used are indicated below:

## (3). DESIGN NOTES

A second major difference between the +12V circuit arrangement and the +5V circuit is the fashion in which Q4 and L3 obtain their power. Since the required current is relatively low; typically about 45 ma, it was derived from a half-wave rectifier circuit operating at a higher voltage than that required for Q1. Consequently, the supply's efficiency was increased.

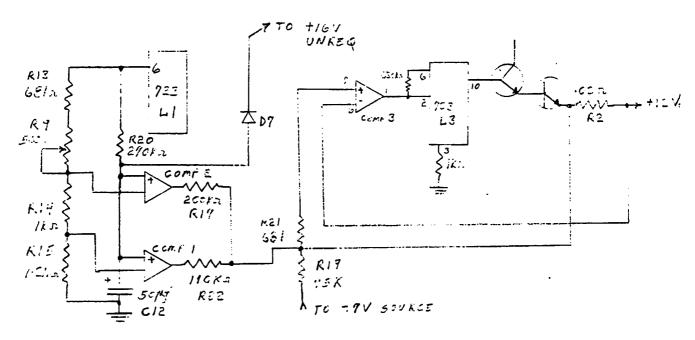

A third major difference is the unusual aspect of the +12V supply current limiting foldback circuitry. The circuitry involved is indicated below.

At initial power-on, the voltage across Cl2 will be approximately zero volts and consequently both Compl and Comp2 outputs will be low (approx. -.3V). This effectively places Rl7, Rl9, and R22 in parallel and permits a higher current limiting value. The graph on page 7 best describes the foldback characteristics. The shaded portion indicates the area that the foldback knee may exist at any particular time.

It should be noted that the supply does not have the capability of providing a clean, regulated output voltage in excess of 10 amps. Should the current drain exceed this value during the first 6 seconds after power-on the output voltage will contain increased amounts of ripple. This is due to Q1's collector voltage being too low.

R20 and C12 comprise a timer circuit and after roughly 6 seconds, the voltage at L2 pin 9 will be approximately 2.75 volts. The other input to the comparator is obtain from the +5V regulator voltage divider network, which incorporates R14 and R15. When the +5V supply is adjusted for an output voltage of 5.05 volts, the voltage at pin 8 of L2 will be 2.75 volts.

At any rate, when the voltage at pin 9 exceeds that at pin 8 the comparator's output will switch to a high impedance state.

After about 6 seconds only R17 and R19 will be in parallel and thus yields the intermediate current limiting value between 7.15A to 8.8A.

After about 15 seconds the voltage at L2 pin 11 will exceed the 5.05 volts present at pin 10. As a result, the comparator's output (pin 13) will go to the high impedance state and thus only R19 now controls the final current limiting value between 5.25A to 6.4A.

# (3). DESIGN NOTES

Diode D7 is used to discharge C12 during power down so that the same current limiting curve can be obtain within a few seconds after powering down. The reason for stepping down the current limiting in this fashion was to reduce the cost, and weight of the supply while maintaining adequate protection for the supply should the output be shorted to ground. This was an alternative to designing a supply capable of providing a continous 10 amps, which would require a much larger transformer and a corresponding heaftier rectifier.

During initial power-on the fixed disk drive(s) exhibit high current surges, this can be seen on the graph on page 7, which illustrates the current versus time characteristics of two Rodime drives. This should fully explain the necessity of altering the current limiting value with respect to time.

### AN ALTERNATIVE TO FUTURE DESIGNS

There are basically two major disadvantages of linear supplies as compared to switching supplies. The first disadvantage is the greater weight and the second disadvantage is the lower efficiency. Unfortunately, at the present time there is little that can be done to reduce the size of the linear transformer; which is the component contributing the most to the overall weight of the supply.

The efficiency can be improved by utilizing pass transistors which have very low saturation voltage, which was exactly what was done on the 7770 and 8397 boards. However, a future alternative might be to use a monolithic regulator being offered by National; part number LM-196-5. Besides being a single package device, this regulator requires only a 1 volt differential voltage. A definite plus in order to obtain the maximum efficiency possible.

Supposedly this part was to be released over a year ago, but as of 2/83 the part was still not available. Apparently, National encountered design problems, but nevertheless, it may prove valuable in future designs.

# (4). TEMPERATURE MEASUREMENTS

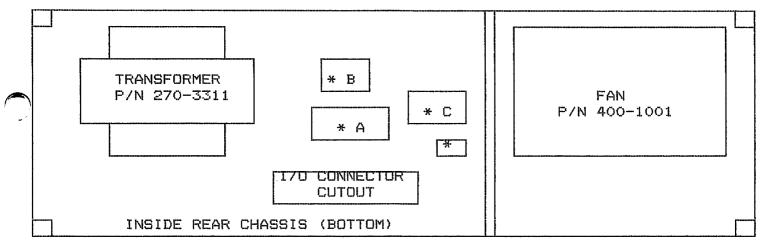

The following indicated temperatures are based on the conditions outlined below.

- 1. The +5V supply is connected to an 8.5 amp load, and the +12V supply is connected to a 4.25 amp load. Both of these loads are to be located externally from the system cabinet.

- 2. All A.C. voltages are to measured at the output of the Variac.

- 3. The thermal sensors are to be applied to the 2N5301 transistors using Eastman's 910 glue or equivalent. While the glue is drying, pressure is to be applied to the sensor to insure a good thermal connection with the transistor case; a small bladed screwdriver is a suitable tool for applying pressure. An accelerator can be used to reduce the drying time.

The sensors are to be located on the top side of the transistor base just in front of the mounting screw that is furthest from the fan.

- 4. The PAC10 thermal sensor is to be secured between the washer and the rectifier module with the retaining nut tightened to 10 in. lbs.

- 5. The FE16C thermal sensor is to be located between the rectifier's case and the flat rectangular washer.

- 6. The thermal switch sensor is to located between the heatsink and the switch housing.

- 7. All temperatures are based on an enclosed unit standing vertically with the fan at the highest elevation. The back of the unit is to be located 6 inches from a vertical wall.

| Ambient temp.= 75 F    | (A) | (B) All temperatures in Fahrenheit |

|------------------------|-----|------------------------------------|

| +12V 2N5301 transistor | tba | 187                                |

| +5V 2n5301 transistor  | tba | 179                                |

| PAC10 rectifier module | tba | 140                                |

| Thermal switch         | tba | 141                                |

| FE16C rectifier module | tba | 175                                |

| P.C. bd. under Q1      | tba | 145                                |

| P.C. bd. under Q2      | tba | 147                                |

(A) 115 Vac input (B) 128 Vac input

Harvey,

TO:

Dan Messuri

Ken Samel

Whom it May Concern

FROM:

Don Logan

Hardware Technical Writing

DATE: November 29, 1983

SUBJ:

Review draft of theory of operation manual for the 2200 MVP

2275 5-1/4" Winchester Floppy Disks Controller

Since it appears that this document is going to be much longer than I had originally expected, I am giving you 50 pages of text to review now, rather than waiting until the entire document is written. should reduce the likelihood of you falling asleep while trying to review the manual. Those of you who are using this document for technical information should bear in mind that this is a review draft, and, as always, is subject to changes and corrections at the whim of the engineer.

# Table of Contents

| 2 | DPU | Bus                     | Arch       | itecture, Memory, and I/O2-1                                                             |

|---|-----|-------------------------|------------|------------------------------------------------------------------------------------------|

|   | 2.1 | Bus                     | Over       | view2-1                                                                                  |

|   | 2.2 | Memo                    | ory        | 2-5                                                                                      |

|   | 2.2 | 2.1                     | ROM        | and Memory Mapped Status Port2-5                                                         |

|   | 2.2 | 2.2                     | Dyna       | mic RAM2-6                                                                               |

|   |     | 2.2.2<br>2.2.2<br>2.2.2 | 2.2<br>2.3 | Generating /RAS                                                                          |

|   | 2.3 | Inp                     | ut/Ou      | tput Ports2-21                                                                           |

|   | 2.3 | 3.1                     | DPU        | Status Ports and Z80A Command Ports2-23                                                  |

|   | :   | 2.3.                    | 1.1        | Winchester Interface Status Port (Input Port 00)2-2                                      |

|   | :   | 2.3.                    | 1.2        | Winchester Interface Command Register 1 (Output Port 10)2-23                             |

|   | :   | 2.3.                    | 1.3        | Winchester Interface Command Register 2 (Output Port 20)2-25                             |

|   | :   | 2.3.                    | 1.4        | Set Controller Ready Port (Output Port 40) Set Controller Busy Port (Output Port 50)2-26 |

|   |     | 2.3.                    | 1.5        | 2200 Data Input Register (Input Port 60)2-28                                             |

|   |     | 2.3.                    | 1.6        | 2200 Data Output Register (Output Port 70)2-29                                           |

|   | :   | 2.3.                    | 1.7        | Floppy Interface Command Register (Output Port CO)2-3                                    |

|   | :   | 2.3.                    | 1.8        | Floppy Controller Reset Port (Output Port DO)2-32                                        |

|   | :   | 2.3.                    | 1.9        | DPU System Status and Options Port (Input Port E0)2-33                                   |

|   | :   | 2.3.                    | 1.10       |                                                                                          |

|   | 2.  | 3.2                     | Pro        | ogrammable I/O Devices2-35                                                               |

|   |     | 2.3.                    | 2.1        | 9517-4 DMA Controller2-35                                                                |

|   |     |                         | 2.2        |                                                                                          |

| List                                                 | of Figures                                                                                                   | Page                                     |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8 | Block Diagram of the DPU Bus Structure.  Generating /RAS                                                     | .2-8<br>.2-12<br>.2-12<br>.2-14<br>.2-16 |

| List                                                 | of Tables                                                                                                    | Page                                     |

| 2-1                                                  | How the Z80A interprets input from the Winchester Interface Status Port                                      | .2-22                                    |

| 2-2                                                  | Effects of Z80A output to Winchester Interface Command Register 1                                            | .2-24                                    |

| 2-3                                                  | Effects of Z80A output to Winchester Interface Command Register 2                                            | .2-26                                    |

| 2-4                                                  | Effects of Z80A output to the Floppy Interface Command Register                                              | .2-32                                    |

| 2-5                                                  | How the Z80A interprets the BD0-BD4 inputs from the DPU System Status and Options Port                       | .2-33                                    |

| 2-6                                                  | How the Z80A interprets the BD5-BD7 inputs from the DPU System Status and Options Port                       | .2-34                                    |

| 2-7                                                  | Addressing the DMA Controller's Base and Current Address Registers and Base and Current Word Count Registers | .2-40                                    |

| 2-8                                                  | Programming the DMA Controller Command Register                                                              | .2-40                                    |

| 2-9                                                  | Programming the DMA Controller Mask Register                                                                 | .2-41                                    |

| 2-10                                                 | Programming the DMA Controller Mode Registers                                                                | .2-42                                    |

| 2-11                                                 | DMA Controller Master Clear and Write All Mask Register Bits commands                                        | .2-43                                    |

| 2-12                                                 | DMA Controller ports addressable by firmware but not used                                                    | .2-44                                    |

| 2-13                                                 | Addressing and programming the Z80 Counter Timer Chips                                                       | 2-45                                     |

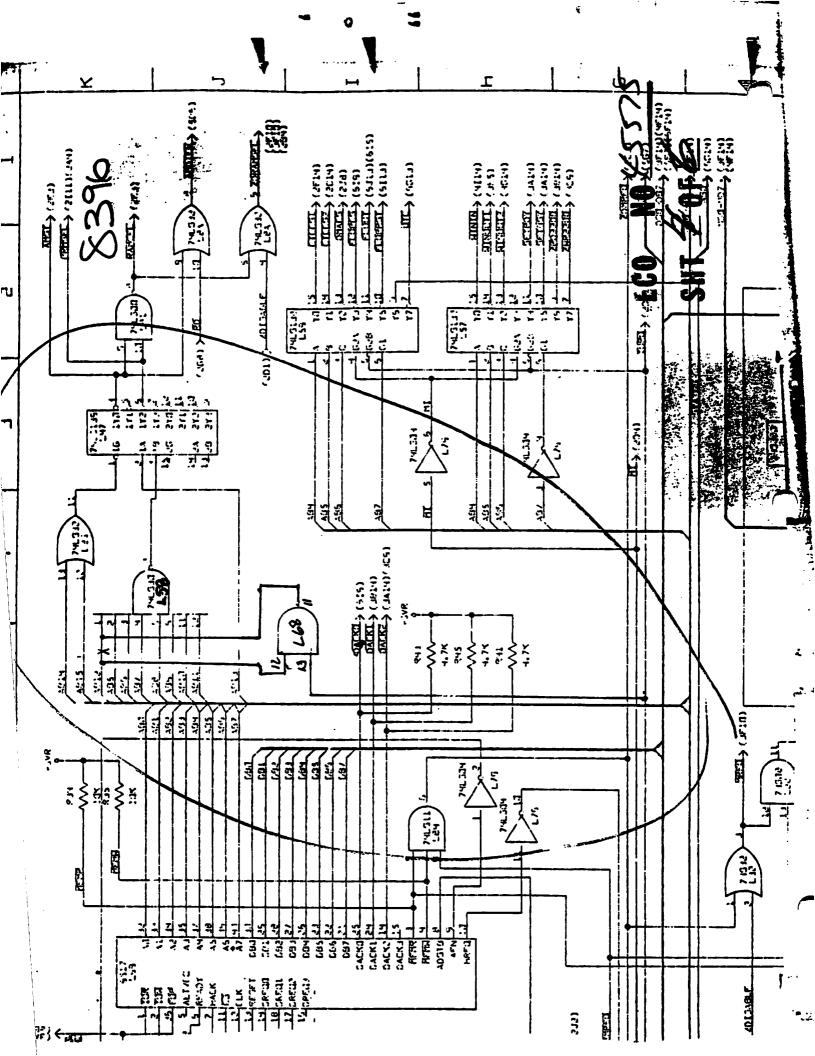

# 2. DPU Bus Architecture, Memory, and I/O

Before looking at how each of the subunits of the DPU functions, it is necessary to look at how information is transferred between these subunits and to look at how these transfers are controlled. This chapter examines the bus architecture of the DPU and discusses the DPU subunits that connect directly to the buses, focusing mainly on memory and I/O.

# 2.1 Bus Overview

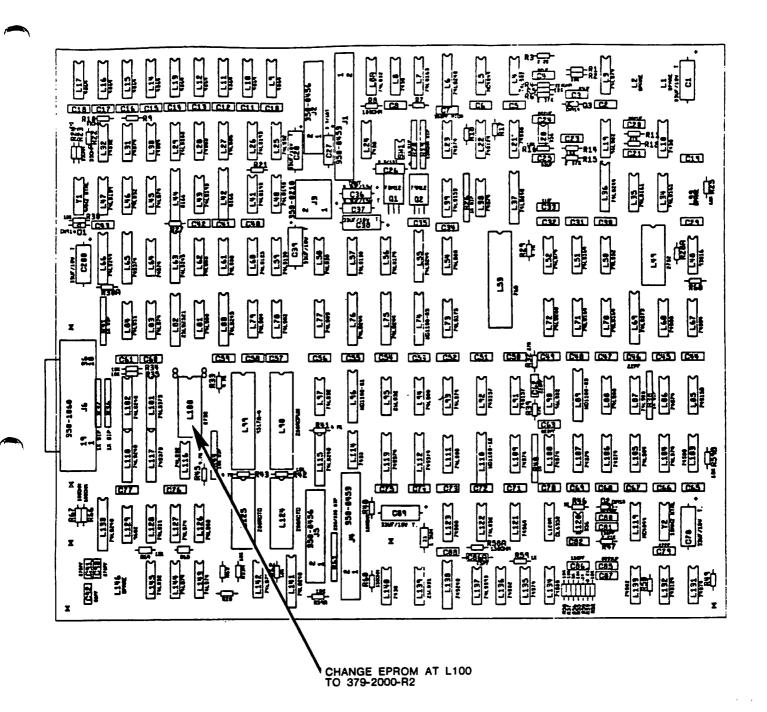

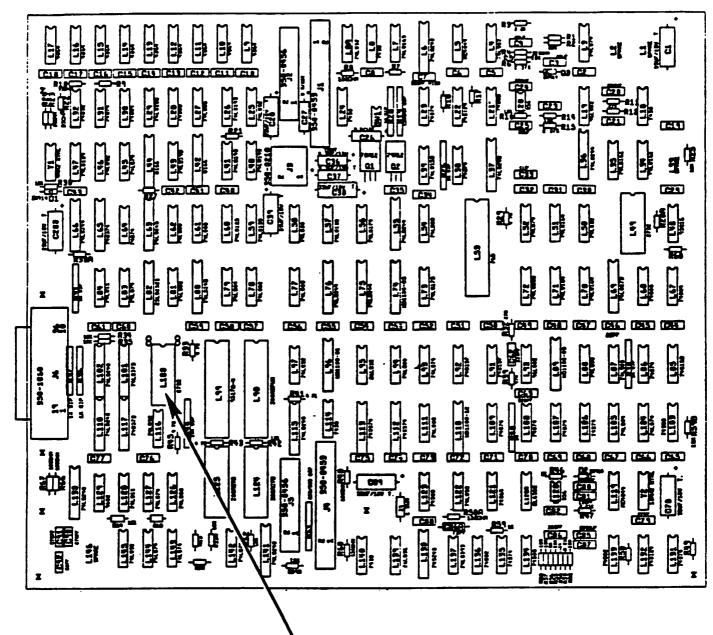

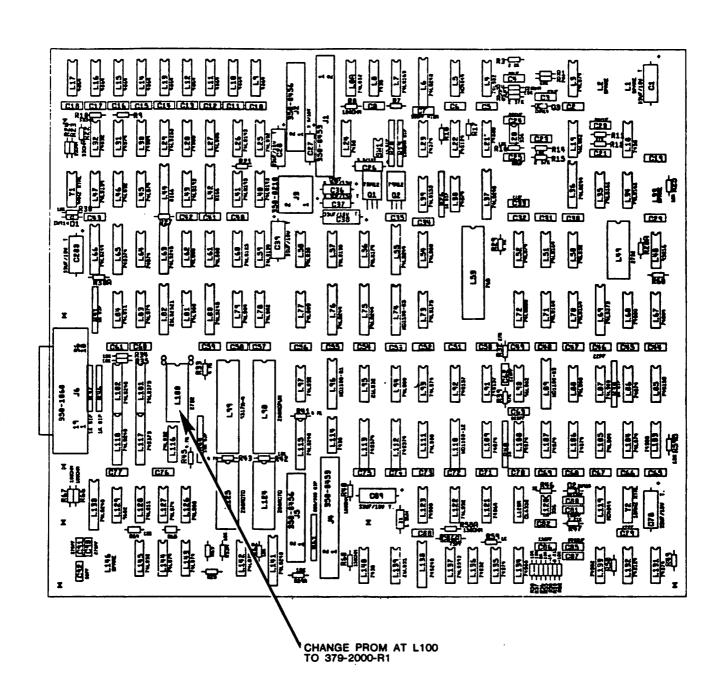

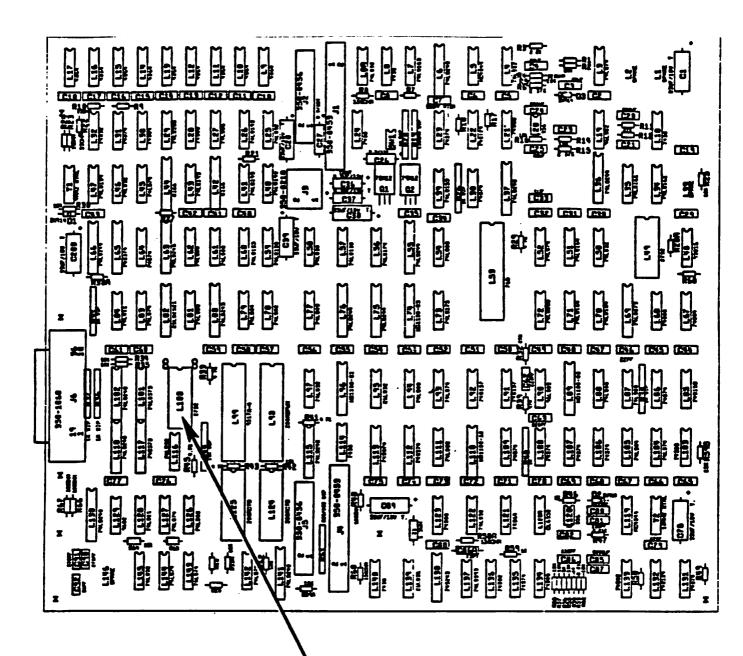

Fig 2-1 is a block diagram of the DPU bus structure. While this diagram shows most of the hardware that is connected to the buses, it does not show all of it. Hardware not shown is discussed at the end of this section. The Main Data Bus, DBO-7, and the Main Address Bus, ABO-15, are controlled by the Z8OA CPU (2I13) and, under the direction of the Z8OA, by the 9517A DMA controller (2I7). Because the DMA controller has only eight address outputs, it must use the DMA Controller High-Order Address Latch (2J10) to form a 16-bit address. The DMA controller writes the high-order byte of the address into the latch, whose outputs are connected to the high-order address bus, and then uses its own eight address outputs to form the low-order byte.

Information flow on the main data and address buses is controlled by the Z80A and the DMA controller. The Z80A operates under the direction of the firmware stored so lovingly in the 8K X 8 ROM (2H10) by that brilliant software engineer, Ken Samel. The DMA controller operates under the direction of the Z80A. The data cache, a 64K X 9 dynamic RAM (3J2-3J99), may be addressed by either the Z80A or the DMA controller through the DMA pointer (3G12-3K12). This pointer is transparent to both the Z80A and the DMA controller and is used by the microsequencer to address the cache during Winchester operations. The DMA pointer and the microsequencer are discussed in

detail in the section on Winchester disk read operations. The row address is gated to the cache from the low-order address bus through the Row Address RAM Driver, L42 (3Ill), and the column address is gated to the cache from the high-order address bus through the column address RAM driver, L44 (3Gll). This hardware is discussed in more detail in the next section.

When the Z80A or the DMA controller address the data cache, data is transferred over the Main Data Bus and the Memory Data Bus through the Main/Memory Data Bus Transceiver, L63 (3G9). The Memory Data Bus is also used by the Winchester control logic to transfer data to or from the cache during read, write, and format operations using a DMA operation. Winchester disk data is transferred to and from memory over the Disk Data Bus and the Memory Data Bus through the Memory/Disk Data Bus Transceiver, L80 (3G7). Because the memory data bus is used by both the Z80A and the Winchester control logic, and since a large portion of the Winchester operations are controlled by the microsequencer while the Z80A marks time, great care has been taken to ensure that the Z80A cannot perform a memory operation when the Winchester control logic is using the cache.

The Z80A controls the Winchester disk drive (or drives) through a pair of I/O ports called the Winchester Interface Command Registers (3D4 and 4H13). Winchester drive status is available to the Z80A at the Winchester Interface Status Port (4I12). I/O ports are selected by a pair of address decoders (not shown), and are discussed in greater detail in the section on I/O ports. The Z80A also addresses the DMA controller and both Z80 CTCs (2C13-2E13) as I/O ports. In addition to performing timing functions for the Z80A, the CTCs function as programmable interrupt prioritizers.

Four DPU system status signals and four options status signals are available to the Z80A through the DPU System Status and Options Port (2E8). Firmware instructs the Z80A to read this port in order to determine what types of disk drives are connected to the DPU. Four switches are connected to this port, and these switches are set to

indicate to the firmware what type of devices it is controlling.

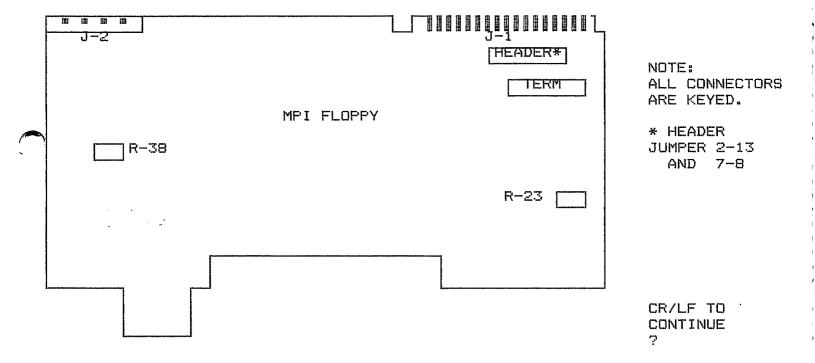

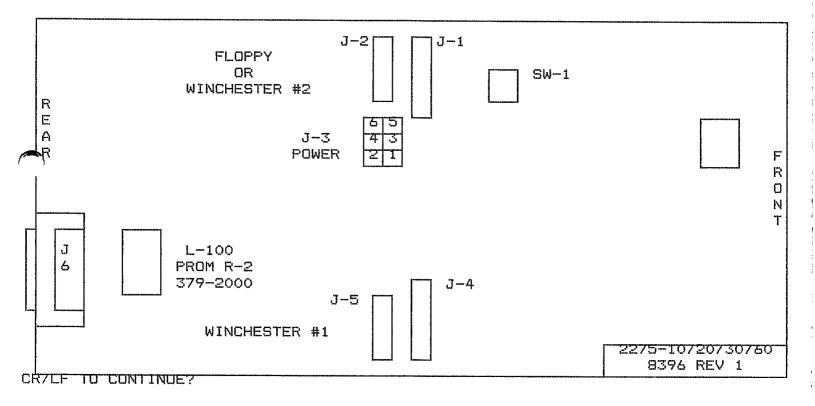

If the removable drive is a mini-floppy, the DPU board will contain a floppy disk controller chip (6H7). This chip is addressed by the Z8OA and the DMA controller as an I/O port. It is programmed by the Z8OA over the Main Data Bus. Floppy disk data is transferred between the cache and the floppy controller by the DMA controller over the Main Data bus and the Memory Data Bus. Floppy control lines that are not manipulated directly by the floppy controller chip are handled by the Z8OA through the Floppy Interface Command Register, L56 (6J4).

The two I/O ports in the bottom right-hand corner of Fig 2-1 allow the Z80A and the DMA controller to communicate with the 2200. The bus nomenclature used here can lead to some confusion. Note that data comes onto the Main Data Bus through the 2200 Data Input Register (3D12) over the Buffered 2200 Output Data Bus. The 2200 buses are named from the 2200's perspective, while ports on the DPU board are named from the DPU's perspective. Thus, the 2200 output bus is connected to a DPU input register, and the 2200 input bus is connected to a DPU output register.

Commands bytes from the 2200 are read and echoed by the Z80A, while block data transfers to and from the 2200 are handled by the DMA controller. The DPU is interfaced to the 2200 through either a Triple Controller Board or a single-connector Disk Interface Board and therefore does not need to decode address information on the 2200 address bus. The controller or interface board handles address decoding, and generates signals to let the DPU know when its services are being requested.

Not shown in Fig 2-1 is the Address Mark Status Port. This memory mapped I/O port, when addressed by the Z80A, places two bits of information on the main data bus: address mark status and header check status. These signals are discussed in the section on Winchester disk read operations. Also not shown is the data cache parity generator/checker, L29 (2E3), which is connected to the memory data

bus. This circuit adds a ninth, parity bit to each byte of data as it is written into the cache, and checks the parity of each byte as data is read from the cache. A non-maskable interrupt is generated when a parity error is detected.

Winchester header data is checked by an 8-bit comparator, L82 (4G8). Header information stored in the data cache by the Z80A is presented to the comparator over the Memory Data Bus, and header information read from the disk is presented to the comparator from the outputs of the serial/parallel converter over the D' data bus. The output of the comparator is used by the Winchester control logic to determine if the head is over the desired sector.

One final piece of hardware connected to the Disk Data Bus but not shown in Fig 2-1 is the 4E/00 bus driver, L75 (4E2). This driver, when enabled by the microsequencer, places a byte of either 4EH or 00H onto the disk data bus. These bytes are routed over the Disk Data Bus to the parallel/serial converter and written onto the disk, where they provide the 4EH filler bytes and the 00H phase locked oscillator synchronization fields. Memory space is saved and execution time is shortened by not requiring the Z80A to write these bytes into the data cache and then have them transferred to the disk.

# 2.2 Memory

DPU memory consists of 8K-bytes of UV-erasable PROM, 64K-bytes of dynamic RAM, and one memory mapped status port. This section looks at how and when each of these segments of memory are accessed.

# 2.2.1 ROM and Memory Mapped Status Port

Z80A firmware is stored in a 2764-2 8K X 8 EPROM that occupies memory locations 0000H through 1FDFH (8,160 bytes). The last 32 bytes of ROM are not used and are not addressable. When the Z80A outputs an

address between 000H and 1FDFH, the 1Y2 output of decoder L47 (2J3) is forced low, asserting /PROMSEL and bringing the ROM /CE input low. The ROM output is enabled when the Z80A brings its /MREQ output low. Note that when ROM is being addressed, the pin 9 input of NAND gate L81 is forced low and /RAMSEL is forced high, ensuring that ROM and RAM cannot be addressed simultaneously. ROM is only addressed by the Z80A, and only during an instruction fetch cycle.

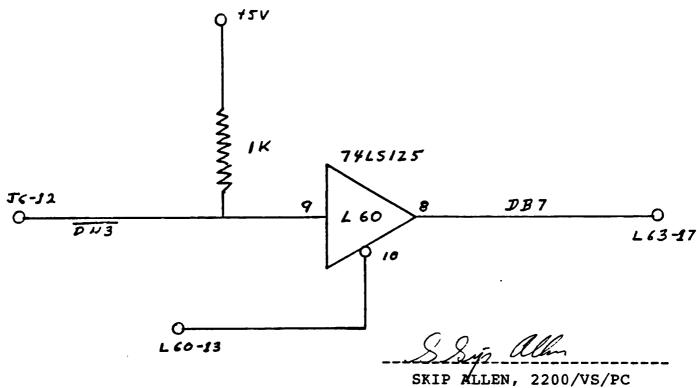

The memory mapped status port occupies memory location 1FEOH. When the Z80A performs a read of this address, the 1YO output of decoder L47 goes low, asserting /AMST. Since /RD is also low, the pin 8 output of OR gate L8A is forced low, asserting /AMSTEN. /AMSTEN enables the pin 6 and pin 11 outputs of buffer L6O (4E6 and 5B6), placing the status of the header check circuit on Main Data Bus line DB2 and the status of the address mark detection circuit on DB1. These signals are used during Winchester operations and are described in more detail in the section on Winchester disk read operations. When the Z80A writes to this address (1FEOH) with bit DB7 set, the rising edge of /WR clocks a one into the 2D input of flipflop L144 (2E3). The Z80A always reads from RAM immediately after setting this flipflop, forcing ZDISABLE to be asserted and cutting the Z80A off from dynamic memory. ZDISABLE is discussed in more detail in the next section.

# 2.2.2 Dynamic RAM

The disk data cache consists of nine, parallel 4864 64K X l DRAMs. Data is stored in L17 through L10, with the least significant bit stored in L17, and L9 stores parity information. The largest block of memory is divided into eight, 16-sector Winchester data caches and an 18-sector floppy data cache. Other blocks of memory are reserved for storage of data to be written to a disk, storage of read-after-write data, and as work space for the ECC correction routine. Additionally, certain blocks are reserved as scratchpad memory for the Z80A. Memory allocation is covered in detail in the

chapter on firmware.

This section looks at the logic that generates the memory timing signals used to control addressing and data transfers. Because of the large number of logic gates and flipflops used to perform these control tasks, it is difficult to see by inspection exactly how memory is controlled. Therefore, the memory control logic has been broken down into several subunits. Each of these subunits is discussed in detail before turning to the general subject of memory timing.

Sixteen address bits are required to directly address 64K-bytes of memory; however, the 4864 DRAMS have only eight address inputs. These inputs are multiplexed to allow two 8-bit addresses to be gated into the chip to form, internally, a 16-bit address. The two 8-bit address segments are gated into the DRAMs by a pair of memory control signals: /RAS and /CAS. The falling edge of the active-low Row Address Strobe signal, /RAS, gates an 8-bit row address into each DRAM. This address is analogous to the low-order address byte in a static RAM. The falling edge of the Column Address Strobe signal, /CAS, gates an 8-bit column address into each DRAM. This address is analogous to the high-order address byte in a static RAM.

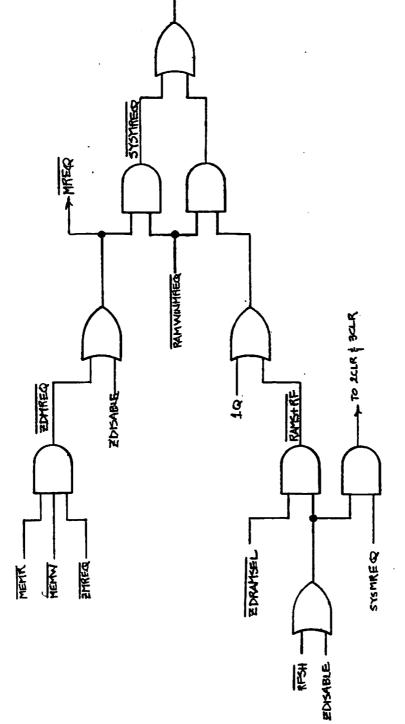

# 2.2.2.1 Generating /RAS

Fig 2-2 shows a schematic of the gates used to generate the /RAS control signal. /RAS is asserted any time that either the Z80A or the DMA controller reads from or writes to the cache. The Winchester control logic also asserts /RAS when taking data from the cache and storing it on a disk or when storing data read from the disk in the cache. Additionally, the Z80A generates /RAS during what is called the '/RAS-only' refresh cycle. /RAS logic also ensures that the Z80A cannot generate /RAS or turn off /CAS when the Winchester control logic is reading from or writing to the cache.

During periods when no device is accessing memory and no

(873)

Winchester operation is in progress, /MEMR and /MEMW (from the DMA controller), /ZMREQ, /RFSH, and /ZDRAMSEL (from the Z8OA), and /RAMWINMREQ (from the Winchester control circuitry) are all in the inactive high states. The input marked 1Q, which comes from the Q output of flipflop L64, is at logic zero. (This signal will be looked at in detail in the section on timing logic). ZDISABLE, which is used to shut the Z8OA off from dynamic memory, is in the inactive low state. /ZDMREQ is therefore in the inactive high state, forcing /MREQ, and /SYSMREQ to be in the inactive high states. Note that since /SYSMREQ is high, SYSMREQ is low and the CLR inputs to both flipflops in L31 are held low. Finally, /RAMS+RF is in the inactive high state and, therefore, /RAS is in the inactive high state.

When the Z80A performs a cache read or write operation, both /ZMREQ and /ZDRAMSEL are forced low, in turn asserting /ZDMREQ, /MREQ, /SYSMREQ, /RAMSEL+RF, and /RAS. At the end of the memory cycle, /ZMREQ returns high, 1Q is forced high, and /RAS is forced to return high. A short time later, /ZDRAMSEL returns high, 1Q again goes low, and the /RAS generator circuit returns to the inactive state. /RAS is generated in essentially the same manner when the DMA controller performs a cache read or write operation. Instead of asserting /ZMREQ, however, the DMA controller pulls either /MEMR or /MEMW low.

Each time the Winchester control logic is ready to read a byte from the cache or write a byte into the cache, it pulls /RAMWINMREQ low, in turn asserting /SYSMREQ and /RAS. Since ZDISABLE is in the active high state when Winchester operations are in progress, the state of /ZDMREQ has no effect on /RAS. In general, neither the Z80A nor the DMA controller can access the cache during Winchester operations. (As always, there is an exception to the rule, and it is discussed in the section on formatting the Winchester).

Before discussing how /RAS is generated during a refresh cycle, a brief review of 'RAS only' refresh is presented. Those who are thoroughly familiar with dynamic memory may wish to skip this paragraph and the next two paragraphs (except Dan, since he has to

review them). The value of a bit of information stored in a dynamic memory cell is indicated by the presence or absence of a charge stored in the capacitance between a transistor gate and the substrate. Because of charge leakage, each cell must be refreshed, or recharged, periodically to avoid losing information. Only those capacitances that are currently holding a charge are recharged, the rest remain discharged.

Memory on a single chip is arranged in 128 rows of data cells. Each row has 512 data cells, or columns, for a total of 128 X 512 = 65,536 data cells. Columns can be further divided into two, 256-cell groups that may be thought of as a right and a left bank. To address a single cell within a chip, an 8-bit row address and then an 8-bit column address are gated into the chip. When a row address is strobed into the chip, the seven least significant bits are decoded to select one of the 128 rows. The eighth and most significant bit is not looked at until the column address is strobed into the chip. At this time, the eighth bit is used to select either the left or the right bank of data cells, and the column address is decoded to select one of the 256 columns in that bank. Also, at this time, the chip's data output is enabled, provided that the write enable input is not active.

Each time a row is addressed, all 256 data cells in that row Since memory access is random, there is no quarantee are refreshed. that every row will be addressed within the 2-msec time limit. CPU therefore sequentially addresses each row at least once every In practice, each row is addressed far more often than this. To perform a refresh, the Z80A outputs a refresh address on its A0-A6 outputs in conjunction with /RFSH and /MREQ. This 7-bit address is decoded by the each memory chip, refreshing all 512 cells in the addressed row. The Z80A automatically performs a refresh cycle after every opcode fetch. One reason for arranging data cells as 128 rows by 512 columns rather than 256 rows by 256 columns is that the former requires only 128 refresh cycles every two msec while the latter requires 256.

During refresh, memory timing logic is prevented from generating /CAS, since no column address is provided and no data output is needed. The write enable input is also held at the inactive high level. /RAS is generated in the same manner for refresh as it is for a normal Z80A read or write from the cache. The only difference is that when /RFSH is asserted, the CLR inputs of both flipflops in L31 are held low, and /CAS is not generated. Since the timing logic is held cleared, lQ remains low, and /RAS is not deactivated until both /ZMREQ and /ZDRAMSEL return high. Note that /RFSH is ORed with ZDISABLE to prevent the Z80A from shutting down the memory timing logic when the Winchester logic is active.

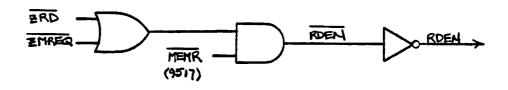

# 2.2.2.2 Generating Read and Write Enable Signals

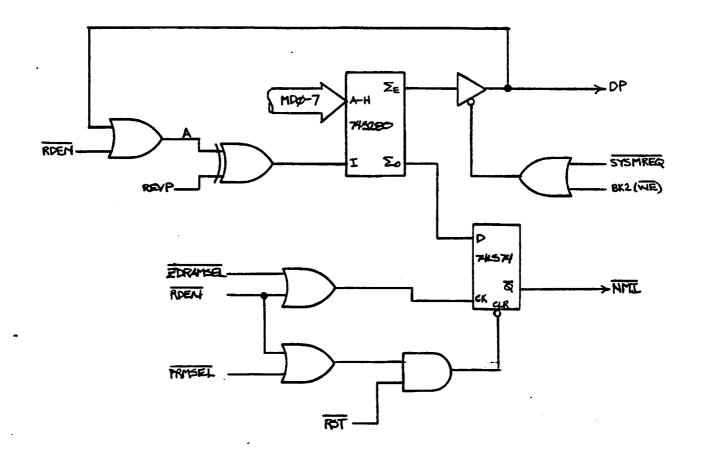

The RDEN signal is generated by the circuit shown in Fig 2-3. This signal, or its complement, is used to control the direction of information flow between the Main and Memory Data Buses, to aid in developing the write enable signal, and to let the cache data parity generator/checker know whether it should be generating parity or checking it. When RDEN is false (low), a write operation is in progress and data flows from the Memory Data Bus to the Main Data Bus. Data can then be gated from the Main Data Bus into either the Z80A or the DMA controller.

When RDEN is true, data flows out of either the Z80A or the DMA controller onto the Main Data Bus, and from there onto the Memory Data Bus and into the cache. Note that the status of RDEN is irrelevant if either /ZDRAMSEL or /MREQ is high, since the Main/Memory Data Bus Transceiver is then disabled. RDEN is only active when the Z80A or the DMA controller is attempting to read data from the cache. In this case, either /ZRD and /ZMREQ will both be low or /MEMR will be low. When data is being written into the cache, or when no operations are being performed on the cache by the Z80A or DMA controller, RDEN is in the inactive low state.

# 2-3 Generating RDEN

# COMPANY CONFIDENTIAL

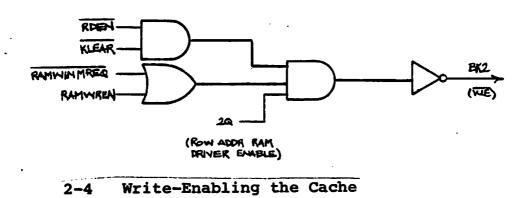

Signals and gates used to write-enable the cache are shown in Fig 2-4. When any of the inputs to the 3-input AND gate are low, /WE is in the inactive high state. When the Z80A or DMA controller is writing data into memory, /RAMWINMREQ remains high and holds the middle input at logic 1. Since a write operation is in progress, /RDEN is in the inactive high state. /KLEAR, as the section on memory timing will show, is in the inactive high state until the end of a write operation, and the top input is therefore at a logic one. The 2Q signal is therefore responsible for asserting /WE. 2Q is part of the timing control logic, and goes high to enable the gating of the column address into the DRAMS. /WE is asserted roughly 125 nsec after /RAS and roughly 125 nsec before /CAS.

When the Winchester control logic is transferring information from a disk drive to the cache, RAMWREN is active high. As with a Z80A write operation, the 2Q signal is responsible for generating /WE. The timing is equivalent to a Z80A write operation. If the Winchester logic is reading information from the cache and storing it on a disk, RAMWREN will be inactive. When the Winchester logic signals a memory operation by bringing /RAMWINMREQ low, the middle input of the 3-input AND gate will be forced low and /WE will not be asserted. The /KLEAR input is responsible for deactivating the /WE signal at the proper time for all memory write operations. /KLEAR returns low when /RDEN returns low, in the case of a Z80A or DMA memory write, or when /RAMWINMREQ returns high, in the case of a Winchester memory write.

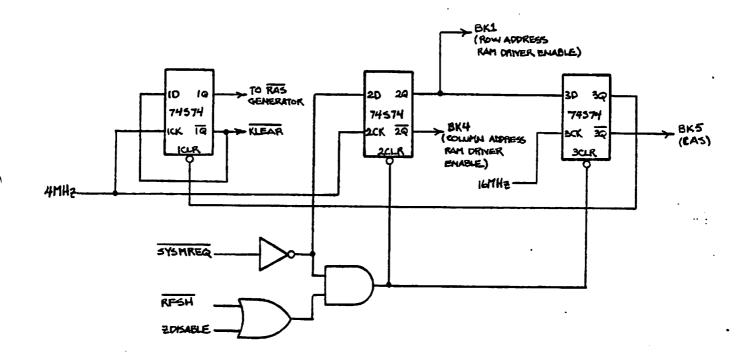

# 2.2.2.3 Memory Timing Logic and Memory Timing

Memory timing is controlled by three flipflops, shown in Fig 2-5. Two of these flipflops are driven by a 4 MHz clock while the third is driven by a 16 MHz clock. These flipflops are shown in the figure in the same order as they are shown on the engineering prints (bottom center of page 2). For convenience, the leftmost flipflop will be designated flipflop 1 in this discussion, followed by

2-5 Memory Timing Logic

flipflops 2 and 3. The Q output of flipflop 1, 1Q, is the source of the 1Q signal described in the section on generating /RAS. Similarly, the Q output of flipflop 2, 2Q, is the source of the 2Q signal mentioned in the previous section.

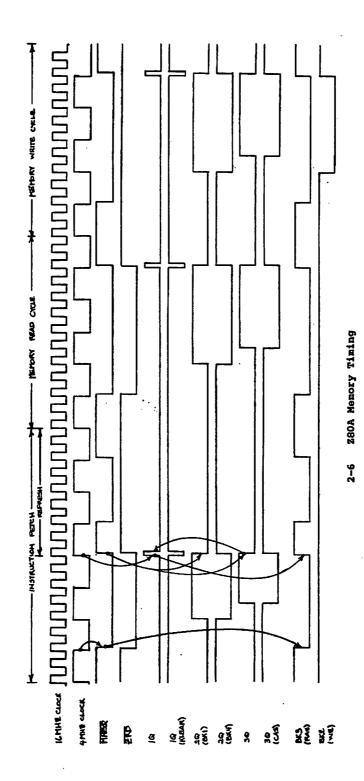

Prior to a cache read or write operation, the 2CLR and 3CLR inputs are held at logic zero. The 3Q output, in turn, holds the ICLR input at logic zero. Fig 2-6 shows how these flipflops control the generation of memory timing signals for various Z80A memory operations. At the start of an instruction fetch cycle, the Z80A asserts /MREQ and /RD on the falling edge of the 4 MHz clock, forcing the /RAS generating logic to assert /RAS. Four gate delays later, the 2CLR and 3CLR inputs are raised to logic one, enabling flipflops 2 and 2Q is connected to the enable input of Row Address RAM Driver L42, allowing the row address to be gated from the Main Address Bus to the inputs of the DRAMS. The falling edge of /RAS strobes the row address into the DRAMS. Note that the /2Q output holds the Column Address RAM Driver, L44, in the disabled state.

At the same time that the 2CLR and 3CLR inputs are raised to logic one, a logic one is presented to the 2D input of flipflop 2. The next rising edge of the 4 MHz clock clocks a one into the 2D input, forcing the 2Q and /2Q outputs to toggle. Row Address RAM Driver L42 is then disabled and Column Address RAM Driver L44 is The column address is then presented to the inputs of the DRAMS and given approximately 70 nsec to stabilize. Since 2Q is now at a logic one, the next rising edge of the 16 MHz clock forces the 3Q and /3Q outputs to toggle, asserting /CAS. 3Q raise the 1CLR input to a logic one, enabling flipflop 1. The next rising edge of the 4 MHz clock forces the 1Q and /1Q outputs to toggle, and 1Q immediately turns off /RAS. In the case of a write operation, /1Q, the source of /KLEAR, immediately turns off /WE. A short time after the rising edge of the 4 MHz clock, /MREQ and /RD return high, forcing the 2CLR and 3CLR inputs to clear flipflops 2 and 3. 3Q in turn clears flipflop 1, and the memory control circuits are all returned to their inactive states.

# COMPANY

All instruction fetch operations are immediately followed by a /RAS only refresh cycle. It is here that the 10 signal plays an important role. According to the manufacturer's specs for the 4864 DRAMS, /RAS must remain high for a minimum of 100 nsec between memory operations. The /MREQ signal does not always return high after the instruction fetch cycle soon enough to meet this timing requirement. 10 is therefore used to turn /RAS off on the rising edge of the 4 MHz clock to allow for the 100 nsec /RAS precharge requirement. As the timing diagram shows, this timing problem only occurs between an instruction fetch and a refresh cycle.

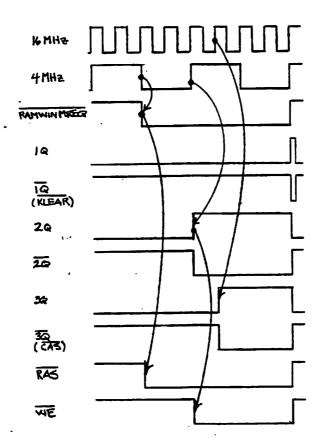

During a refresh cycle, /RFSH goes low in conjunction with /MREQ and holds flipflops 1, 2, and 3 in the cleared state. /CAS cannot be asserted and the data outputs of the DRAMs are not enabled. /RAS simply follows /MREQ. Memory read and memory write cycles are similar to the instruction fetch cycle, but /RAS and /CAS are stretched out an extra 125 nsec. Winchester memory timing, shown in Fig 2-7, is identical to the instruction fetch operation just described, except that /RAMWINMREQ sets the ball rolling rather than /MREQ. Finally, memory timing under the direction of the DMA controller is identical to the timing of the memory read and write cycles for the Z8OA, and is not shown.

# 2.2.2.4 Cache Data Parity Generator/Checker

The circuit responsible for automatically generating and checking the parity of data stored in the cache is shown in Fig 2-8. The easiest way to see how this circuit works is to step through an example. Assume that a byte of OlH is to be written into the cache. Since /RDEN is high for a write operation, the signal named 'A' in Fig 2-8 will be at logic 1. During normal operation, REVP is in the inactive low state. (REVP is only activated during powerup diagnostics to check the operation of the parity circuit). The EXCLUSIVE OR of A (1) and REVP (0) is therefore true, and a logic 1 is presented to the I input of the parity generator chip.

2-7 Winchester Memory Timing

2-8 Cache Data Parity Generator/Checker

Since the data byte has a single one, and since the I input is at logic 1, the EVEN output of the parity generator will be a logic (The EVEN output is at logic 1 if an even number of inputs are at logic 1, and the ODD output is at logic 1 if an odd number of the inputs are ODD). During a write operation, both /SYSMREQ and /WE will go low, enabling the output of the parity buffer. The EVEN output of the parity generator is then connected to the data input of the parity In this example, the parity bit is a logic 1. DRAM.

When this byte is read from memory, /RDEN goes low, and the 'A' signal is forced to reflect the state of the parity bit. The EXCLUSIVE OR of the parity bit (1) and REVP (0) is a logic 1, and the EVEN output from the parity generator is again a logic 1. The ODD output from the parity generator is a logic 0. At the end of the read operation when /RDEN returns to the inactive high state, this zero is clocked into the D input of the flipflop. The /Q output remains high, and /NMI is not asserted.

If one of the DRAMS had failed, resulting in no ones in the data field instead of a single one, the ODD parity output would have been a logic 1. When the logic I was clocked into the flipflop, the /Q output would have gone low and /NMI would have been asserted. parity error is defined as a fatal error. If a parity error is detected during the normal course of events, the board puts the cat out for the night and goes into an idle state.

During powerup diagnostics, the operation of the parity generator/checker is tested by writing data with reverse parity and then reading it back with normal parity. In the example used in this section, the EXCLUSIVE OR of 'A' and REVP during write with reverse parity would be a logic 0, since both 'A' and REVP are at logic 1. Because only one data bit is at logic 1 and the I input is at logic 0, the EVEN output would be logic 0. This zero would be stored in the parity DRAM as the parity bit. On read-back with normal parity, 'A' would be logic 0 and REVP would be logic 0, forcing the I input to the parity generator to be a logic 0. The ODD output from the parity

generator would therefore go high forcing a non-maskable interrupt. If a parity error does not occur during this test, the Z80A knows something is really hosed up. /NMI can be cleared either by a reset or a Z80A read from ROM. The interrupt is automatically cleared when the Z80A attempts to read the first instruction in the service routine (the interrupt vector), since /PRMSEL is necessarily asserted.

# 2.3 Input/Output Ports

I/O ports on the DPU board can be divided into two general categories: those that provide the Z80A with direct input of DPU status signals or allow the Z80A to directly manipulate DPU control signals, and those that interface the Z80A with programmable controllers, counters, and timers. This section examines each of these ports in detail.

### 2.3.1 DPU Status Ports and Z80A Command Ports

These ports provide information ranging from the status of individual signals that allow the Z80A to make control decisions, to the statuses of groups of signals that allow firmware to determine what type of removable disk drive is currently plugged into the board. The Z80A outputs commands to non-programmable circuits on the board be writing to one of eight output ports. These ports provide the Z80A with a way to directly manipulate control signals. This section describes each of these eleven ports in detail.

# 2.3.1.1 Winchester Interface Status Port (Input Port 00)

Five status signals from the Winchester drive (or drives) are made available to the Z80A at this port. If a removable Winchester disk drive is plugged into the board, it must share this port with the

fixed Winchester drive. Only the selected drive will make status information available; outputs from a de-selected drive are floated by circuits in the drive. This port informs the Z80A whether or not the heads are over cylinder 0, alerts the Z80A to any conditions on the drive that might cause data to be written improperly, informs it when the drive is ready and when the heads are over the desired cylinder, and lets it know which drive is supplying the information to ensure that the correct disk drive is responding.

When the Z80A reads this port by outputting xx00 on the Main Address Bus and asserting /IORQ, the Y0 output of decoder L57 (2H2) is forced low and /WININ is asserted. /WININ pulls the enable inputs of driver L115 (4I12) low, placing Winchester status information on the Main Data Bus. The Z80A then latches the information into an internal register and decodes it. Data obtained from this port is interpreted as shown in Table 2-1. Note that signals from the disk drive are inverted by the driver. The logic values shown in the 'State' column of Table 2-1 reflect the values the Z80A sees. The state of the signals coming from the disk drive are actually the inverse of the logic values shown in the 'State' column.

| Bit<br>Number | State  | Interpretation                                                                                                                                                                                                                             |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBO           | 0<br>1 | /TRACKO is at logic 1. Heads are not over track 0.<br>/TRACKO is at logic 0. Heads are over track 0.                                                                                                                                       |

| DBl           | 0      | /WRFLT is at logic 1. Disk drive is OK. /WRFLT is at logic 0. A write fault condition exists. May cause data to be written improperly. All write operations are inhibited until condition is corrected.                                    |

| DB2           | 0      | /READY is at logic 1. The drive is not ready.  Generally this means that the motor is not up to speed yet.  /READY is at logic 0. The drive is ready. When true in conjunction with /SKCOMP, data can be read from or written to the disk. |

Table 2-1. How the Z80A interprets input from the Winchester Interface Status Port.

| DB3        | 0 | /SKCOMP is at logic l. Seek is not complete. Heads are not over the desired cylinder. /SKCOMP is at logic 0. Seek is complete. Heads are positioned over the desired cylinder. |  |  |  |  |

|------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DB4        | 0 | /DRSO is at logic 1. The fixed drive is not selected.  /DRSO is at logic 0. The fixed drive is selected.  (DB5 had better be 0).                                               |  |  |  |  |

| DB5        | 0 | /DRS1 is at logic 1. The removable drive is not selected.  /DRS1 is at logic 0. The removable drive is selected. (DB4 had better be 0).                                        |  |  |  |  |

| DB6<br>DB7 |   | Spare. Not looked at by firmware.<br>Spare. Not looked at by firmware.                                                                                                         |  |  |  |  |

Table 2-1 (continued). How the Z80A interprets input from the Winchester Interface Status Port.

#### 2.3.1.2 Winchester Interface Command Register 1 (Output Port 10)

Four of the signals originating at the outputs of this register are sent to the disk drive. Three of them are combined at the drive to select one of the heads, while the fourth is used to reduce the amount of current passed through the heads when data is being written onto one of the dense inner tracks. The latter output, along with the three of the remaining register outputs, are used either individually or in pairs to generate control signals that enable and disable circuits in the Winchester control logic. These signals allow the Z80A to initiate and halt Winchester read, write, and format operations.

When the Z80A outputs xxl0 on the Main Address Bus and asserts /IORQ, the Yl output of decoder L57 is forced low and /WINOUTl is asserted. At the end of the write cycle, the Z80A deactivates /IORQ, causing /WINOUTl to return high. The rising edge of /WINOUTl clocks data from the main data bus into Winchester Interface Command Register 1, L112 (3D4), forcing the outputs to reflect the commands from the Z80A. The effects of writing to this port, based on the state of each

bit, are shown in Table 2-2. Note that signals sent to the disk drive are inverted before leaving the board.

| Bit<br>Number | State  | Effect on Control Signals                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DB0           | o      | /HDSELO is set to logic 1. /HDSELO-3 are combined at the drive to form a binary number that is used to select a head.                                                                                                                                                                                                                                   |  |  |  |  |

|               | 1      | /HDSELO is cleared to logic O.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DB1           | 0<br>1 | /HDSELl is set to logic l.<br>/HDSELl is cleared to logic 0.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DB2           | 0      | /HDSEL2 is set to logic l.<br>/HDSEL2 is cleared to logic 0.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DB3           | 1      | RWC and /RWC are forced to logic 0 and 1 respectively. Normal write current is passed through the heads, and write precompensation logic on the MFM generator is not activated. RWC and /RWC are forced to logic 1 and 0 respectively. Current flowing in the write head is reduced, the write precompensation logic on the MFM generator is activated. |  |  |  |  |

| DB4           | 0      | TEND is cleared to logic 0. The microsequencer will not execute the format-track-end firmware.  TEND is set to logic 1. The microsequencer will execute the format-track-end firmware.                                                                                                                                                                  |  |  |  |  |

| DB5           |        | Not connected. Has no effect.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| DB6           | 0      | READ is cleared to logic 0, turning off the read control hardware of the Winchester logic. Brought to this state temporarily during a READ operation to clear a header error condition. /FORMAT is set to logic 1.                                                                                                                                      |  |  |  |  |

|               | 1      | READ and RW are set to logic l. Initiates a read operation. If WRITE is asserted simultaneously, /FORMAT will be asserted and a format operation will be performed.                                                                                                                                                                                     |  |  |  |  |

| DB7           | 1      | WRITE is cleared to logic 0, turning off the write control hardware of the Winchester logic. /FORMAT is set to logic 1.  WRITE and RW are are set to logic 1. Initiates a write operation. If READ is asserted simultaneously, /FORMAT will be asserted and a format operation will be performed.                                                       |  |  |  |  |

Table 2-2. Effects of Z80A output to Winchester Interface Command Register 1.

# 2.3.1.3 Winchester Interface Command Register 2 (Output Port 20)

Signals from the outputs of this register are used to select a Winchester disk drive, step the heads, and define the direction in which the heads are to be stepped. When the 2200 commands the Z80A to perform a Winchester operation, the Z80A first figures out which Winchester the 2200 is asking for (even if there is only one), and then writes to this port to select the appropriate drive. If the heads are not over the desired cylinder, they must be moved. After determining which cylinder the heads are currently over, which direction they need to be stepped in, and how many steps need to be made to place the heads over the correct cylinder, the Z80A checks to see if /DIRCT is in the appropriate state. If /DIRCT is indicating a step in the wrong direction, the Z80A writes to this port and changes the step direction.

To step the heads, the Z80A pulses the /STEP signal low for 6.75 usec. /STEP is pulsed by writing to this port twice: once to force /STEP low and once to return it high. If the heads are to be stepped more than one cylinder, the Z80A continues to pulse /STEP every 22.5 usec until a /STEP pulse has occurred for every cylinder the heads are to be moved over. The heads move in or out one cylinder for each pulse of the /STEP line. At the disk drive, the /STEP pulses are counted, and when the drive determines that it has received all the step pulses it is going to get, it moves the heads over the appropriate number of cylinders in one smooth motion. The process of counting the step pulses before moving the heads is known as a buffered seek.

When the Z80A writes to this port by placing xx20 on the Main Address Bus and bringing /IORQ low, the Y2 output of decoder L57 (2H2) is forced low, and /WINOUT2 is asserted. At the end of the write cycle when /IORQ is returned high, the Y2 output of L57 also returns high and the rising edge of /WINOUT2 clocks data from the main data bus into Winchester Interface Command Register 2, L113 (4H13). Table 2-3 shows what actions are forced when this port is written to, based

on the state of the individual bits. Note that signals sent to the disk drive are inverted before leaving the board.

| Bit<br>Number | State  | Effect on Control Signals                                                                     |  |  |  |

|---------------|--------|-----------------------------------------------------------------------------------------------|--|--|--|

| DBO           | 0      | /DRVSELO is cleared to logic O. Fixed Winchester                                              |  |  |  |

|               | 1      | is de-selected.  /DRVSELO is set to logic l. Fixed Winchester is selected.                    |  |  |  |

| DBl           | 0      | DRVSELl is cleared to logic 0. Removable Winchester is de-selected.                           |  |  |  |

|               | 1      | /DRVSELl is set to logic l. Removable Winchester is selected.                                 |  |  |  |

| DB2           | 0<br>1 | /STEP is deactivated by setting to logic 1. /STEP is activated by clearing to logic 0.        |  |  |  |

| DB3           | 0      | /DIRCT is forced to logic l. Direction of step will be out (toward the center of the disk).   |  |  |  |

|               | 1      | /DIRCT is forced to logic 0. Direction of step will be in (away from the center of the disk). |  |  |  |

| DB4<br>DB5    |        | Not connected. Has no effect.<br>Not connected. Has no effect.                                |  |  |  |

| DB6<br>DB7    |        | Not connected. Has no effect.<br>Not connected. Has no effect.                                |  |  |  |

Table 2-3. Effects of Z80A output to Winchester Interface Command Register 2.

# 2.3.1.4 Set Controller Ready Port (Output Port 40) and Set Controller Busy Port (Output Port 50)

Before the 2200 attempts to send a command byte to the DPU, it must check the DPU's ready/busy status to ensure that the DPU is ready. Similarly, before attempting to read data from the DPU's 2200 Data Output Register, the 2200 must ensure that the DPU is ready. The 2200 must always wait until the DPU is ready before attempting to send or receive data. On friday afternoons, the DPU gets incredibly drunk (like its designer) and doesn't raise the ready flag until sometime late saturday afternoon. In the board-busy state the /2Q output of flipflop L83 (3Bl0) is at logic 0; in the board-ready state L83 is in

the cleared state and the /2Q output is at logic 1. This signal is inverted by driver L130 (3A9) before it is routed to the 2200.

The DPU board can be placed in the busy state in any one of four ways. A busy state is automatically entered during both power-on and hardwired resets. When /RST is brought low, the 2PR input of L83 is forced low, and the ready/busy flag is set to the busy state. The board is also automatically placed in the busy state when the DMA controller completes a data transfer from the DPU to the 2200. In this case, the DMA controller simultaneously outputs both /EOP and /DACK2 low, forcing the 2PR input of L83 low.

A third condition also automatically places the controller in the busy state. When the 2200 writes a command byte into the DPU's 2200 Data Input Register, the falling edge of /BOBS (which is inverted by line driver L130) clocks a high into the 2D input of L83, placing the board in the busy state. The Z80A may place the board in the busy state at any time by writing arbitrary data to the Set Controller Busy Port (output port 50). When the Z80A addresses this port by placing xx50 on the Main Address Bus and bringing /IORQ low, the Y5 output of decoder L57 (2H2) is forced low and /SETBSY is asserted. /SETBSY forces the pin 12 output of AND gate L128 low, in turn forcing the 2PR input of L83 low, placing the board in the busy state.

If the board is in the busy state and firmware determines that the board is no longer busy, the Z80A sets the board in the ready state by writing arbitrary data to the Set Controller Ready Port (output port 40). When the Z80A places xx50 on the Main Address Bus and brings /IORQ low, the Y4 output of decoder L57 is forced low and /SETRDY is asserted. /SETRDY forces the pin 6 output of AND gate L61 low, in turn bringing the 2CLR input of flipflop L83 low, placing the board in the ready state.

During DMA transfers from the 2200 to the DPU, as mentioned, the board is automatically placed in the busy state. When the DMA controller reads the 2200 Data Input Register by bringing /RD low, the

pin 6 output of AND gate L61 is forced low (since /DACK1 is also low). The 2CLR input of L83 is brought low, and the board is placed in the ready state. Thus, the board is automatically placed in the busy state when the 2200 sends a byte of data, and automatically placed in the ready state when the DMA controller reads the byte.

### 2.3.1.5 2200 Data Input Register (Input Port 60)

All command and data bytes from the 2200 are passed to the DPU through the 2200 Data Input Register, L65 (3D11). The 2200 places a byte of data on its data output bus, /BOB1-8 (3C-E14), and brings the Output Bus Strobe (/BOBS) low. /BOBS is inverted by line driver L130 and is presented to the A input of 1-shot L129, the 2CK input of flipflop L83, and the CK/TR3 input of CTC1. The falling edge of /BOBS clocks a one into the 2D input of L83, placing the board in the busy state, triggers L129, and generates an interrupt request to the Z80A via channel three of CTC1. The /Q output of L129 is pulsed low for 500 nsec. Since the /Q output is tied to the 1-shot's B input, the A input is disabled for the duration of the pulse, preventing noise on the /BOBS input from re-triggering the 1-shot.

Data on the 2200's output bus is inverted by the 2200-DPU Data Input Buffer, L102, and then presented to the D inputs of the 2200 Data Input Register. When the 1-shot times out, the rising edge of its /Q output clocks data from the 2200 into L65, where the data may then be read by either the Z80A or the DMA controller. When the 1-shot is triggered, the Q output from the 1-shot is presented to the 1D input of flipflop L83. The next rising edge of 4CLK sets the flipflop, asserting OBREQ1, which issues a DMA request to the DMA controller at its DREQ1 input. OBREQ1 is synchronized with 4CLK to satisfy a timing requirement of the DMA controller.

Because OBREQ1 is generated even when the 2200 sends a command byte to the Z80A, the DMA controller is programmed to ignore OBREQ1 when command bytes are being sent. CTCl informs the Z80A when a

command byte has been written into the register, and the Z80A then reads the command byte. Once the Z80A has received all the command bytes from the 2200 and is ready to receive data, CTCl is programmed to ignore the output bus strobe and the DMA controller is programmed to respond to the interrupt request. The DMA controller then takes over the task of reading data from the 2200. After the DMA controller reads all the data it has been programmed to read, it issues an End of Operation (/EOP) signal that is passed through CTC2 to the Z80A. The Z80A then programs the DMA controller to ignore the DMA request, and continues on to the next step of the operation.

The Z80A reads the 2200 Data Input Register by placing xx60 on the Main Address Bus and bringing /IORQ low, forcing the Y6 output of decoder L57 (2H2) to go low asserting /ZRD2200. /ZRD2200 forces the pin 3 output of AND gate L61 low, forcing the OC input of L65 low, which dumps the data in the input register onto the Main Data Bus. Data is strobed into the Z80A on the rising edge of its /RD output. The DMA controller reads the 2200 Data Input Register by simultaneously bringing /DACK1 and /RD low. /RD is asserted when the DMA controller brings its /IOR output low. Pin 6 of OR gate L116 then goes low, forcing the pin 3 output of AND gate L61 and the OC input of L65 low, placing the data in the input register onto the Main Data Bus. Data is latched into the DMA controller on the rising edge of the DMA controller's /IOR output.

#### 2.3.1.6 2200 Data Output Register (Output Port 70)

All data and operation status bytes sent from the DPU to the 2200 must pass through the 2200 Data Output Register, L117 (3D10). The Z80A uses this register to send operation status information to the 2200 when an operation has been completed, and also to echo command bytes as they are received from the 2200. Data is transferred from the data cache to the 2200 through this register by the DMA controller. Before sending any data to the 2200, both the DMA controller and the Z80A must ensure that the 2200 is not busy. When

the 2200 is busy, its BCPB signal (3A9) is in the active high state.

When the Z80A desires to send data to the 2200, it polls the DPU System Status and Operation Port until it finds /CPB is in the inactive high state. Having determined that the 2200 is not busy, the Z80A writes a byte of data into the 2200 Data Output Register by placing xx70 on the Main Address Bus and bringing /IORQ low. The Y7 output of decoder L57 (2H2) is forced low, and /ZWR2200 is asserted. /ZWR2200 then forces the pin 6 output of NAND gate L81 high, which in turn forces the ENB input of L117 high. At the end of the write cycle, the rising edge of /ZWR2200 latches the data on the Main Data Bus into the the 2200 Data Output Register.

The rising edge of /ZWR2200 also clocks a one into the 1D input of flipflop L127, causing its 1Q output to assert the 2200 Input Bus Strobe (IBS). IBS is inverted by driver L130, and /BIBS is presented to the 2200. The /1Q output of L127 brings the /1G and /2G inputs of the DPU-2200 Data Output Buffer, L118, low, gating data in the output register onto 2200 Data Input Bus lines BIB1-8. When the 2200 receives an active /BIBS, it knows that the data on the input bus is valid. The Z80A knows that the 2200 received the data when it sees the 2200 enter the busy state. If the 2200 is busy, /CPB holds the 1CLR input of L127 low, ensuring that a fault in the DPU board cannot accidentally cause data to be placed on the 2200 Data Input Bus.

Data read from a disk is sent to the 2200 under the direction of the DMA controller. When the 2200 goes from the busy state to the ready state, a logic one is presented to the 2D input of flipflop Ll27 (3A6). The first rising edge of 4CLK sets Ll27, forcing its 2Q output high. The rising edge of the 2Q output clocks a one into the 1D input of flipflop Ll43, causing IBREQ2 to be asserted at the 1Q output. IBREQ2 issues a DMA request to channel two of the DMA controller.

The DMA controller writes a byte of data into the 2200 Data Output register by simultaneously bringing /DACK2 and /WR low. /WR is forced low when the DMA controller brings its /IOW output low.

Bringing these two signals low has the same effect as bringing /ZWR2200 low, which has already been covered in detail. In addition, the pin 3 output of AND gate L126 is forced low, clearing L143 and removing the DMA request by forcing /IBREQ2 back to the inactive low state. When the 2200 goes busy to read the data, the 2CLR input of L127 is brought low, clearing the flipflop for the next transfer. Again, /CPB holds the 1CLR input of L127 low, preventing a fault in the controller board from accidentally dumping data onto the 2200 Data Input Bus.

IBREQ2 is also generated when the Z80A is sending status information to the 2200 and echoing command bytes. During these times, the DMA controller is not programmed to respond to the DMA request. When the Z80A is ready to let the DMA controller take over the task of sending data, it programs the DMA controller to respond to the DMA request. After the DMA controller has transferred the number of bytes it was programmed to transfer (generally 257 bytes), it issues an End of Operation (/EOP) signal to the Z80A via channel zero of CTC2. The Z80A then programs the DMA controller to ignore DMA requests on channel two, and continues on to the next phase of the operation.

# 2.3.1.7 Floppy Interface Command Register (Output Port CO)

The Floppy Interface Command Register, L57 (6J4), allows the Z8OA to turn the floppy motor on and off, select and de-select the floppy, clear the floppy door-open flag, and assert REVP during the powerup diagnostics. REVP allows data to be written into the cache with reverse parity so that the operation of the cache data parity generator/checker can be tested.

When the Z80A writes to this port by placing xxC0 on the Main Data Bus and bringing /IORQ low, the Y4 output of decoder L59 (2I2) is forced low, and /FLOUT is asserted. At the end of the write cycle, the rising edge of /FLOUT clocks the data on Main Data Bus lines DB0-5