## Micro VP Computer System

Models:

Micro VP-1 Micro VP-2

Customer Engineering Product Maintenance Manual

741-1668

# PUBLICATION UPDATE BULLETIN

TITLE: Micro VP Computer System

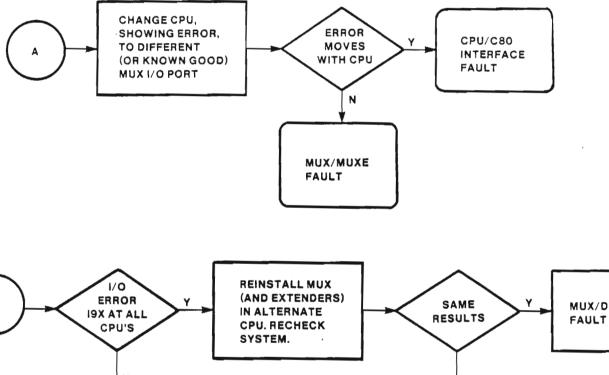

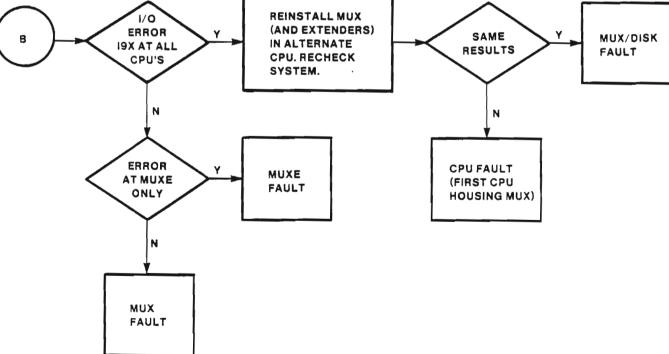

**DATE:** 5/13/88

This PUB affects:

741-1668 742-1668 Color: Yellow

**Previous Notice(s):** 741–1668–1

#### **REASON FOR CHANGE:**

This PUB. provides updated information to the appropriate sections of the Micro VP Computer System Product Maintenance Manual.

#### INSTRUCTIONS:

Remove and insert attached pages and/or microfiche as follows:

|                      | REMOVE PAGES | INSERT PAGES       |

|----------------------|--------------|--------------------|

| 1.<br>2.<br>3.<br>4. | v/vi         | v/vi<br>Appendix B |

| 6.<br>7.             |              |                    |

| 8.<br>9.             |              |                    |

| 10.                  |              |                    |

|    | REMOVE FICHE | INSERT FICHE |  |  |  |  |  |  |  |

|----|--------------|--------------|--|--|--|--|--|--|--|

| _  | 1            |              |  |  |  |  |  |  |  |

| 1. | Fiche 1      | Fiche l      |  |  |  |  |  |  |  |

| 2. | Fiche 2      | Fiche 2      |  |  |  |  |  |  |  |

| 3. |              |              |  |  |  |  |  |  |  |

| 4. |              |              |  |  |  |  |  |  |  |

This page constitutes a permanent record of revisions; place it directly following title page.

LABORATORIES INC

ONE INDUSTRIAL AVENUE, LOWELL, MASSACHUSETTS 01851 TEL (617) 459-5000 TWX 710 343-6769, TELEX 94-7421

#### COMPANY PROPRIETARY STATEMENT

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

© Copyright 1988, Wang Laboratories, Inc.

## Micro VP Computer System

## Models:

Micro VP-1 Micro VP-2

#### COMPANY PROPRIETARY STATEMENT

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

Customer Engineering Product Maintenance Manual

741-1668

#### PREFACE

This document is the Product Maintenance Manual (PMM) for the Wang Micro VP Computer Systems. The manual is organized in accordance with Customer Engineering Technical Documentation's approved PMM outline. The scope of this manual reflects the type of maintenance philosophy selected for this product.

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with sufficient instructions to operate, troubleshoot, and repair the Wang Micro VP Computer System. The manual will be updated on a regular schedule or as necessary. Such updates will be published either as Publication Update Bulletins (PUBs) or as full revisions.

#### First Edition (June, 1985)

Use of the material in this document is authorized only for the purpose stated in the Preface, above.

© Copyright 1985, Wang Laboratories, Inc.

# PUBLICATION UPDATE BULLETIN

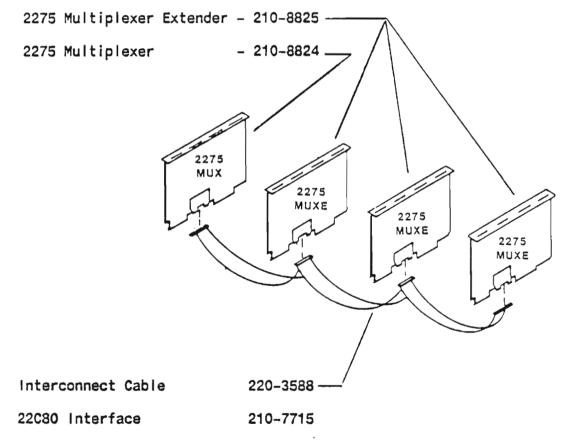

TITLE: 2275 MULTIPLEXER/MULTIPLEXER EXTENDER OPTION DATE: 02/23/87

MICROVP This PUB affects:

741-1668 ? WHAT MNL IS THIS, CLASS CODE: 4103

Previous Notice(s):

None

#### **REASON FOR CHANGE:**

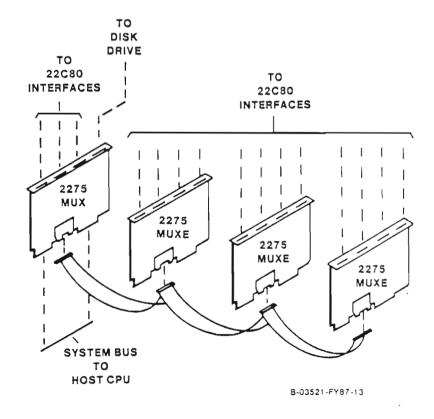

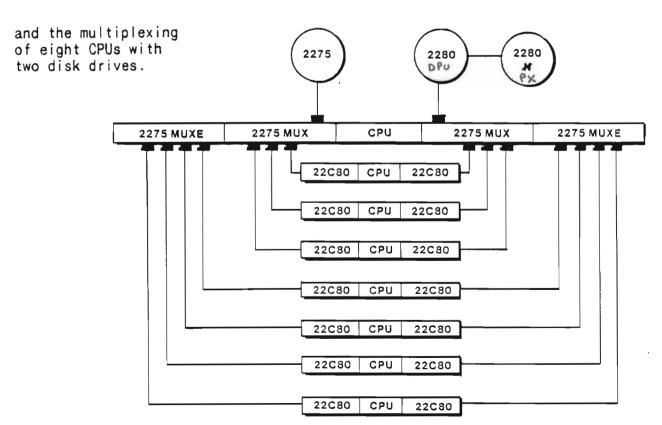

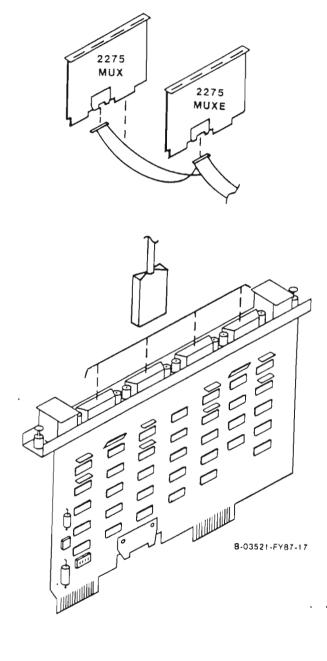

To provide installation, checkout, troubleshooting, and parts-replacement data for the 2275 Multiplexer and 2275 Multiplexer Extender option for the Micro VP Computer System.

INSTRUCTIONS:

Remove and insert attached pages and/or microfiche as follows:

|                                                    | REMOVE PAGES | INSERT PAGES              |

|----------------------------------------------------|--------------|---------------------------|

| 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9. | v, vi        | v, vi<br>A-1 through A-15 |

|    | REMOVE FICHE | INSERT FICHE |

|----|--------------|--------------|

|    |              |              |

| 1. | 1, 2         | 1, 2         |

| 2. |              |              |

| 3. |              |              |

| 4. |              |              |

This page constitutes a permanent record of revisions; place it directly following title page.

LABORATORIES INC

#### **COMPANY PROPRIETARY STATEMENT**

. . L

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

© Copyright 1987, Wang Laboratories, Inc.

#### WARNING

Do not open the switching power supply under any circumstance. Extremely dangerous voltage and current levels (in excess of 300 volts DC and unlimited current) are present within the power supply.

Do not attempt to repair the switching power supply; it is field replaceable only.

After powering the unit down and disconnecting the AC power connector from the power source receptacle, allow one minute before removing the power supply to provide adequate time for any residual voltage to drain through the bleeder resistors.

## TABLE OF CONTENTS

|                                                                                                          |                                                                                                                                                                                                                                                | PAGE                                                               |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Chapter 1                                                                                                | ntroduction                                                                                                                                                                                                                                    |                                                                    |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                          | Scope and Purpose                                                                                                                                                                                                                              | 1-1<br>1-1<br>1-2                                                  |

| Chapter 2 T                                                                                              | heory of Operation                                                                                                                                                                                                                             |                                                                    |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.3.1<br>2.2.3.2<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8 | Introduction CPU Functional Theory Control Memory Bootstrap Proms Data Memory 128K Data Memory 512K Data Memory Memory Partitioning Generating Partitions Global Partitions CPU, Memory, and I/O Interface Switching Power Supply              | 2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-3<br>2-3<br>2-4<br>2-4 |

| Chapter 3 0                                                                                              | peration                                                                                                                                                                                                                                       |                                                                    |

| 3.1<br>3.2<br>3.2.1<br>3.3<br>3.4<br>3.5<br>3.6                                                          | Scope Controls and Indicators Power On/Off Initial Power-on Procedure Daily Power-on Procedure Normal Power-down Procedure Emergency Power-down Procedure                                                                                      | 3-1<br>3-1<br>3-2<br>3-2<br>3-2                                    |

| Chapter 4 I                                                                                              | nstallation                                                                                                                                                                                                                                    |                                                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4.1<br>4.4.2<br>4.5<br>4.6<br>4.6.1<br>4.7<br>4.8<br>4.9                   | Scope Installation Site Check Unpacking and Inspection Installation Switch Settings Cabling Initial Power-up System Verification System Diagnostics Partition Generation Generating Evenly-Divided Partitions Customizing Partition Generation | 4-1<br>4-3<br>4-3<br>4-8<br>4-11<br>4-12<br>4-12<br>4-14<br>4-22   |

| 4.10                                                                                                     | System Turnover to Customer                                                                                                                                                                                                                    | 4-22                                                               |

## TABLE OF CONTENTS (CONT.)

|                |                                    | PAGE   |

|----------------|------------------------------------|--------|

| Chapter 5      | Preventive Maintenance             |        |

| <u> </u>       |                                    |        |

| 5.1            | Scope                              |        |

| 5.2            | Special Tools and Equipment        |        |

| 5.3            | Maintenance Procedures             |        |

| 5.3.1          | Central Processing Unit            |        |

| 5.4            | Alignments and Adjustments         |        |

| 5.4.1          | Voltage Adjustments                |        |

| 5.5            | Removal and Replacement Procedures |        |

| 5.5.1          | Top Cover Removal                  |        |

| 5.5.2          | Top Cover Replacement              |        |

| 5.5.3          | Switching Power Supply Removal     |        |

| 5.5.4          | Switching Power Supply Replacement |        |

| 5.5.5<br>5.5.6 | CPU/Memory Board Removal           |        |

| 5.5.7          | CPU/Memory Board Replacement       |        |

| 5.5.7          | I/O Controller Board Replacement   |        |

| 5.5.9          | Motherboard Removal                |        |

| 5.5.10         | Motherboard Replacement            |        |

| 5.5.11         | Cooling Fan Removal                |        |

| 5.5.12         | Cooling Fan Replacement            |        |

| 0,000          |                                    |        |

|                |                                    |        |

| Chapter 6      | Illustrated Parts Breakdown        |        |

|                |                                    |        |

| 6.1            | Scope                              | 6-1    |

|                |                                    |        |

| Chapter 7      | Troubleshooting                    |        |

|                | <del>-</del>                       |        |

| 7.1            | Scope                              | 7-1    |

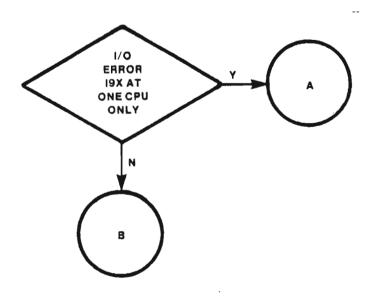

| 7.2            | Bootstrap Diagnostics              | 7-1    |

| 7.2.1          | Initialization Errors              |        |

| 7.2.2          | Reset Errors                       |        |

| 7.2.3          | System Errors                      |        |

| 7.2.3.1        | Memory Errors                      |        |

| 7.2.3.2        |                                    |        |

| 7.3            | Microcode Diagnostics              | 7-6    |

| 7.3.1          | CPU Instructions Diagnostic        | 7-7    |

| 7.3.2          | Control Memory Diagnostic          | 7-8    |

| 7.3.3          | Data Memory Diagnostic             | 7 10   |

| 7.3.4          | CPU Registers Diagnostic           | , /~IC |

| 7.4            | Peripheral Device Diagnostics      | , /-10 |

| 7.5            | Diagnostic Error Messages          | . /-10 |

|                |                                    |        |

| Chapter 8      | Schematics (Microfiche Only)       | . 8-1  |

## TABLE OF CONTENTS (CONT.)

|                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Appendix A                                                                                                                                                     | 2275 Multiplexer/Multiplexer Extender Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A-1                                                                                                                               |

| Appendix B                                                                                                                                                     | CPU/Memory PCB Upgrade Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B-1                                                                                                                               |

|                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

|                                                                                                                                                                | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   |

| FIGURE                                                                                                                                                         | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PAGE                                                                                                                              |

| 2-1<br>2-2<br>2-3<br>3-1<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>5-2<br>5-3<br>5-4<br>5-5<br>5-7<br>5-8<br>5-1<br>6-2<br>6-3 | CPU/Memory Board Memory Partition CPU/Memory Board Block Diagram AC Power On/Off Switch 120/240 AC Voltage Switch Device Address Switches MXD Multiplexer Device and Baud Rate Switches MXE Multiplexer Device and Baud Rate Switches 22C32 Triple Controller Switches Printer Interface Cabling Disk Interface Cabling TC, Tapes, Plotters, and Terminal Cabling Multiplexer Cabling 120/240 AC Line Voltage Select Switch Operating Voltage Testpoints Top Cover Screws Bottom Retaining Screw Power Supply Retaining Screws Motherboard Connectors AC Power On/Off Switch Wiring CPU/Memory Board I/O Board Slots Fan Power Connection CPU/Memory Board Micro VP Motherboard Switching Power Supply | 2-2<br>2-3<br>2-6<br>3-1<br>4-2<br>4-5<br>4-6<br>4-7<br>4-6<br>4-1<br>4-1<br>5-4<br>5-5<br>5-6<br>5-7<br>5-6<br>5-7<br>5-6<br>6-4 |

|                                                                                                                                                                | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

| TABLE                                                                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PAGE                                                                                                                              |

| 4-1<br>4-2                                                                                                                                                     | Typical Device Addressing Device Address Switch Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3<br>4-4                                                                                                                        |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 SCOPE AND PURPOSE

This Product Maintenance Manual (PMM) concerns the the Wang Micro VP Computer System, and provides field personnel with the information necessary to:

- Unpack and Install the System

- Perform Preventive Maintenance Procedures

- Perform Diagnostic Tests

- Analyze Failure Indications

- Replaced Failed Assemblies

#### 1.2 APPLICABLE DOCUMENTATION

A complete listing of Wang technical documentation is presented in the Technical Documentation Catalog/Index (742-0000). Other product documentation is identified in the Corporate Resource Catalog (700-7647).

#### 1.3 SYSTEM DESCRIPTION

The Wang Micro VP is an interactive, multi-user, multi-task, disk-based computer system, utilizing VLSI (Very Large Scale Integration) technology. The Micro VP supports up to thirteen terminals and sixteen jobs (partitions) concurrently as well as a wide range of peripheral devices, such as printers, plotters, disk drives, tape drives, and TC devices.

By utilizing VLSI, the Micro VP processor design is incorporated into a single chip. This allows the Micro VP CPU, control memory, and user memory to reside on a single PC board. There are two models of Micro VP Computer systems. The Micro VP-1 contains 128K of data memory while the Micro VP-2 contains 512K. In addition, both systems contain 32K of control memory.

#### 1.4 SYSTEM SPECIFICATIONS

#### Physical Dimensions:

Width: 15-1/8 in. (38.4 cm) Depth: 21-3/4 in. (55.25 cm) Height: 8-3/4 in. (22.24 cm)

#### Power and Environmental Requirements:

Input Circuit: Dedicated 20A circuit

Voltage: 115/230 VAC ± 10%

Frequency: 50/60 HZ.

Running Current: 2.0 amps @ 115 vac 1.0 amps @ 230 vac

#### Operating Environment:

Ambient Temp.: 60 to 80 degrees Fahrenheit 15 to 28 degrees Celsius

#### Government and Industry Standards and Approvals:

Domestic: UL Standard 114

FCC Class A

Int'l: CSA Standard C22.2 NO 154

IEC 435

VDE Standard for Germany

#### Service Space Required:

Allow 30" between wall and each unit in

system.

Special Specifications:

None

#### 1.5 SYSTEM OPTIONS

Both the Micro VP-1 and Micro VP-2 Computer Systems require a minimum configuration of one workstation, one disk drive, and one printer. A number of peripherals are supported, a list of which follows;

| Mode I | Description                |

|--------|----------------------------|

| 2201L  | Character Printer          |

| 2209AV | Nine-Track Mag. Tape Drive |

| 2211M  | Printer Multiplexer        |

| 2221W  | Matrix Line Printer        |

## 1.5 SYSTEM OPTIONS CONT.

| Mode I                         | Description                                                                                                      |

|--------------------------------|------------------------------------------------------------------------------------------------------------------|

| 2227B<br>2228B,C,D,E,F<br>2229 | Buffered Asyncronous Communications Controller<br>Binary Syncronous Communications Controller<br>Tape Controller |

| 2230MXA<br>2230MXB             | Master Daisy Chain Disk Mux Controller<br>Slave Daisy Chain Disk Mux Controller                                  |

| 2231                           | Line Printer                                                                                                     |

| 2231W-1,2,6                    | Matrix Line Printers                                                                                             |

| 2231W-3<br>2232A/B             | Aux. Printer for the X2282 Graphics Terminal Digital Flatbed Plotter                                             |

| 2232A7 B<br>2233               | Matrix Line Printers                                                                                             |

| 2234,34A                       | Hopper-Feed Punched Card Reader                                                                                  |

| 2235                           | Matrix Line Printer                                                                                              |

| 2236MXD                        | Multiplexer                                                                                                      |

| 2236MXE                        | Multiplexer                                                                                                      |

| 2236D, DE, DW                  | Interactive Terminal                                                                                             |

| 2336DE,DW                      | Ergo Interactive Terminal                                                                                        |

| 2240-1,-2                      | Dual Removable Flexible Disk Drive                                                                               |

| 2241                           | Thermal Printer                                                                                                  |

| 2244A,44B                      | Hopper-Feed, Mark-Sense Punched Card Reader                                                                      |

| 2245                           | Matrix Line Printer<br>Matrix Line Printer                                                                       |

| 2251<br>2260,60BC,60C          | Fixed/Removable Disk Drives                                                                                      |

| 2261,61W                       | Matrix Line Printer (240 lpm)                                                                                    |

| 2262-1,-2,-3                   | Digitizer                                                                                                        |

| 2270                           | Removable Diskette Disk Drive                                                                                    |

| 2270A-1,-2,-3                  | IBM 3740-Compatible Diskette Drive                                                                               |

| 2271,2271-P                    | Bidirectional Output Writer                                                                                      |

| 2272-1,-2                      | Triple Pen Drum Plotter                                                                                          |

| 2273                           | Band Printer                                                                                                     |

| 2275                           | Disk                                                                                                             |

| 2280-1,-2,-3                   | Fixed Removable Disk Drive (Pheonix)                                                                             |

| 2281                           | Daisy Output Writer                                                                                              |

| 2281P                          | Daisy Plotting Output Writer                                                                                     |

| 2281W                          | Wang Daisy Output Writer                                                                                         |

| 2282                           | Graphics CRT Plotter                                                                                             |

#### CHAPTER 2

#### THEORY OF OPERATION

#### 2.1 INTRODUCTION

Overall operation of the Micro VP CPU (Micro VP-1 and Micro VP-2) is controlled by the CPU/Memory board (210-8034). This chapter provides a brief description of this CPU.

#### 2.2 CPU FUNCTIONAL THEORY

The Micro VP CPU/Memory board contains the Micro 2200 chip, a 121 pin gate-array which comprises the entire CPU. The chip requires +5 volts at VDD1-2 (pins B7 and M7) and ground at VSS1-2 (pins G2 and G12). A 5 MHZ square wave at pin F1 provides the system clock.

#### 2.2.1 Control Memory

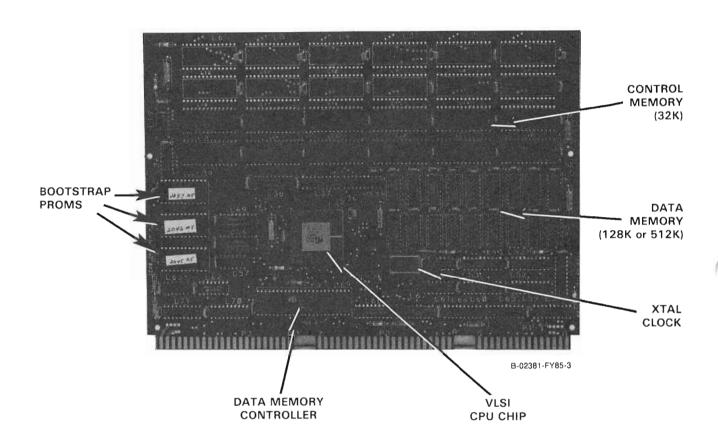

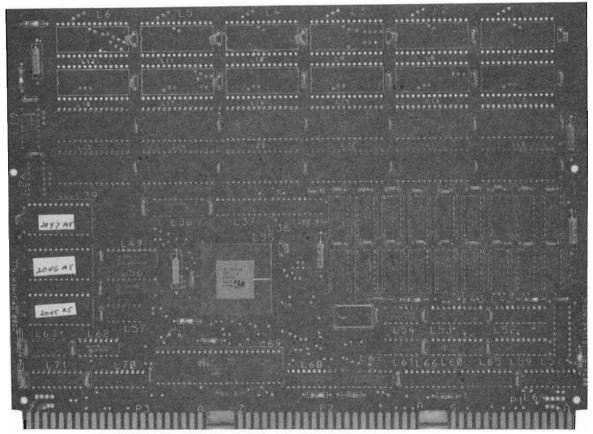

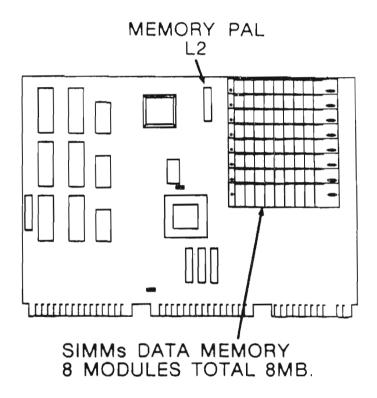

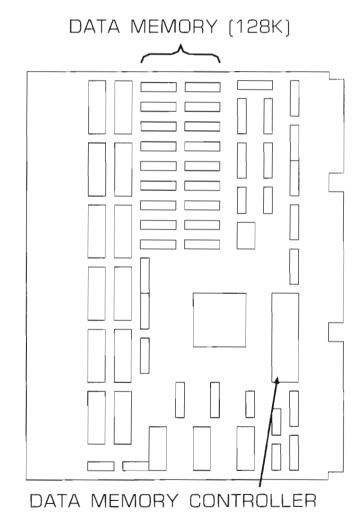

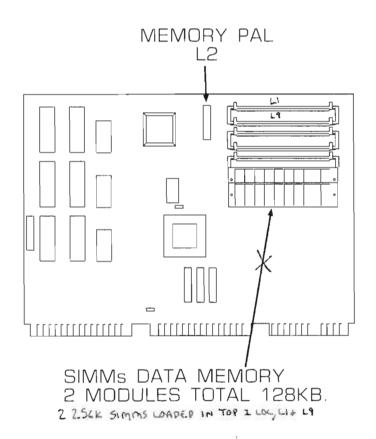

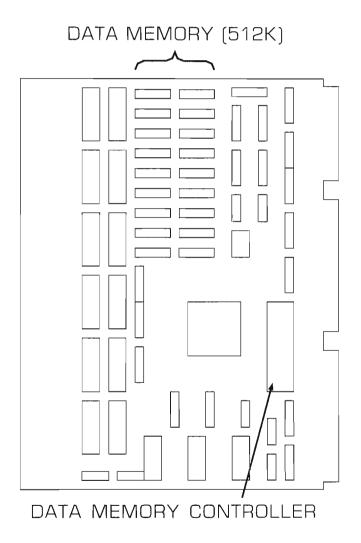

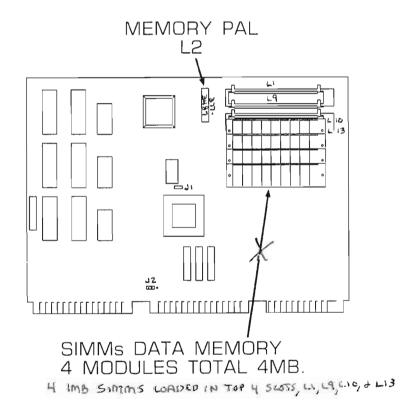

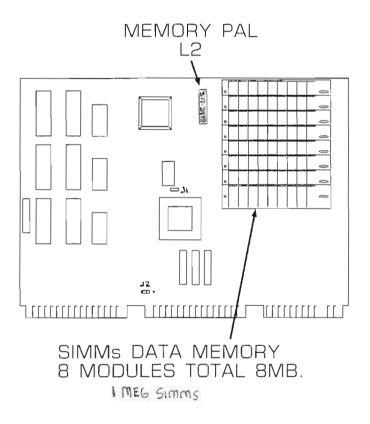

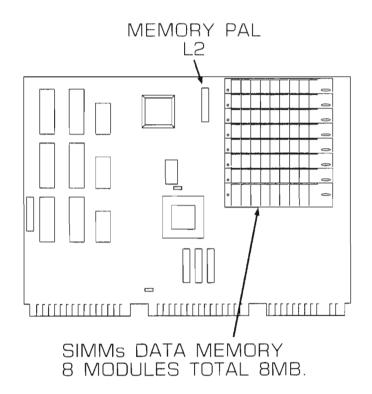

The CPU/Memory Board contains 32K of Control Memory. This is accomplished by loading 12 memory chips in board locations L13 through L18 and L20 through L25 (ref. Fig. 2-1).

Locations L1 through L12 of the CPU/Memory board are not loaded with memory chips. These locations are for possible future expansion.

The Control Memory is made up of 8k x 8 Static RAM configured in groups of three so that each group forms 8K of 24 bit words (one bank). Four of these groups (banks) produce 32K of control memory.

#### 2.2.2 Bootstrap Proms

Three  $2K \times 8$  proms, configured to form 24 bit words, comprise the bootstrap prom. If the address decoded on the system bus is between 8000 and 83FF the bootstrap proms are enabled and chip select for the control memory store is inhibited.

#### 2.2.3 Data Memory

#### 2.2.3.1 128K Data Memory (Micro VP-1)

With a 128K Data Memory configuration there are 2 banks, with 9 chips in each bank, for a total of 18 chips. Each chip contains 64K x 1 bit which produces 64K x 9 bits (8 bits data plus 1 bit parity) in each bank. Together the two banks produce 128K 8 bit bytes plus parity.

#### 2.2.3.2 512K Data Memory (Micro VP-2)

With a 512K memory configuration, there are 2 banks, with 9 chips in each bank, for a total of 18 chips. Each chip contains 256K x 1 bit which produces 256K x 9 bits (8 bits data plus 1 bit parity) in each bank. Together the two banks produce 512K 8 bit bytes plus parity.

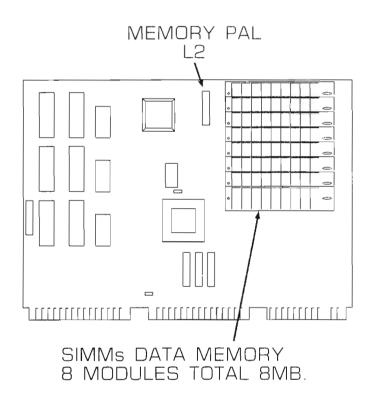

Fig. 2-1 CPU/Memory Board

#### 2.2.4 Memory Partitioning

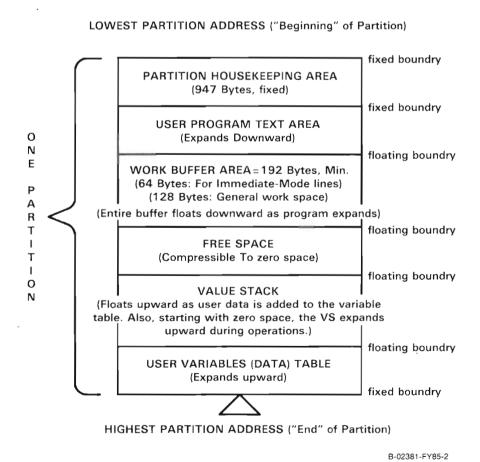

Memory Partitioning is a technique used in the allocation of available data (user) memory space. Each "partition" represents a block of memory space with specified address boundaries. The Micro VP is configured such that each user is allocated one or more blocks (partitions) of data memory which belong exclusively to him.

#### 2.2.5 Generating Partitions

The number of partitions to be created and the amount of data memory to be allocated to each partition are specified by the user in a process called "partition generation". This process involves specifying certain attributes for each partition and supplying the addresses of peripheral devices connected to the system (ref. Chapter 4).

Once the Operating System has been loaded into Control Memory, a special utility program called @GENPART is loaded and executed at workstation #1. This program, through a series of display prompts, guides the system operator through the necessary steps for "partition generation" (ref Chapter 4).

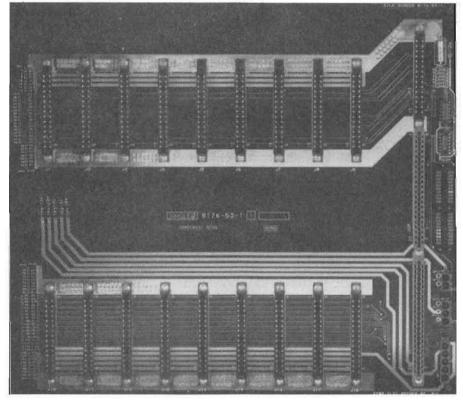

With partition generation implemented, the system handles each partition as it would the entire data memory space of a single-user system, with space allocated for housekeeping, user program, work areas, and data tables. (See Fig. 2-2.)

Figure 2-2 Memory Partition

#### 2.2.5 Partition Generation (Cont.)

The Micro VP Operating System will support a maximum of 16 partitions and 13 system users. All 16 partitions may be allocated to a single user, or multiple-partition configurations may be created. Partition sizes are specified in 256 byte increments. The minimum size that may be specified for a partition is 1.25K (1280 bytes), with some portion of each partition accessable to all users (ref. 2.2.6). The guideline for maximum size, is that each partition must be defined wholly within the confines of one memory bank; no user partition is allowed to extend from one bank to another. The Micro VP-1 system contains 2 banks of user data memory, with each bank comprised of 64K of memory space, while the Micro VP-2 system has 8 banks of user data memory, also comprised of 64K each. (Ref. Fig. 2-1.)

#### 2.2.6 "Global Partitions"

Although partitions function independently, there are situations in which it is highly expedient for two or more partitions to cooperate with one another, to share common information, common programs. This sharing eliminates needless duplication of applications software and data, thus allowing more efficient use of available data memory space.

Partitions can therefore be "global"; that is, each partition designated as such, contains programs and/or data which become conditionally shareable. A foreground or background program that is running in a partition in one bank can access any global partition residing in that same bank. Additionally, a user terminal that is attached to a partition in that same bank can access those global routines and/or data.

Another form of "Global Partition" is an area in memory which contains programs and/or data which must be accessible to all system users. This area is restricted to the first 5K block of data memory and is called a "Universal Global Partition".

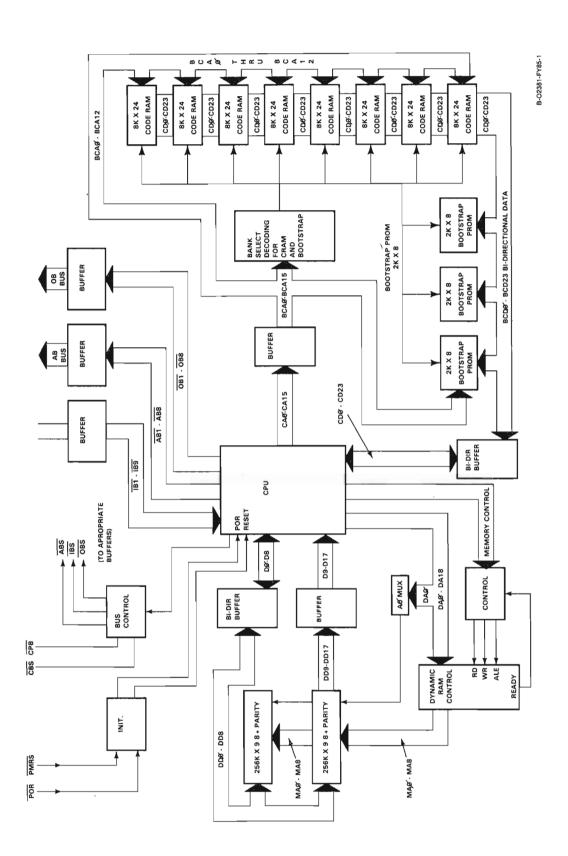

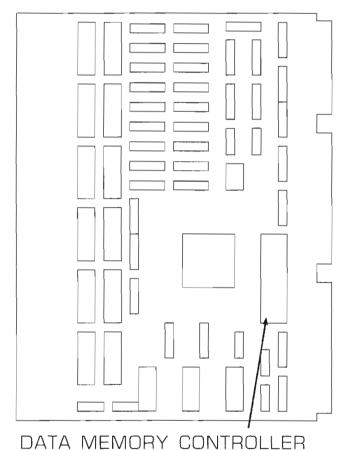

#### 2.2.7 CPU, Memory, and 1/0 Interface

As previously mentioned, the CPU functions are handled by a single VLSI chip (L55) on the CPU/Memory Board. Control Ram is accessed through Control Memory Access Lines CAO through CAl5 and bi-directional data is passed through Control Memory Data Lines CDO through CD23. Two rows of data ram are accessed through Dynamic Ram Control and Data Address Lines DAO-DAl8. Data is then transfered through memory data lines DDO-17, with DD9-17 being used as input for 16 bit read operations (18 if parity bits are included) only. Data lines DDO-8 are bi-directional and are used for both read and write operations.

I/O devices are accessed through an 8 bit address bus  $\overline{\text{AB1-AB8}}$  and  $\overline{\text{data}}$  is passed through an 8 bit output data bus  $\overline{\text{OB1-OB8}}$ . A 9-bit input bus,  $\overline{\text{IB1-IB9}}$ , from the I/O devices to the CPU completes the interface. Overall control of  $\overline{\text{the}}$  address bus, output bus, and input Bus is accomplished by the CPU pulses  $\overline{\text{OBS}}$ ,  $\overline{\text{IBS}}$ ,  $\overline{\text{ABS}}$ , and  $\overline{\text{CBS}}$ . (Ref. Fig. 2-3).

#### 2.2.8 Switching Power Supply

The SPS255 Switching Power Supply is capable of outputting four supply voltages +5, -5, +12, and -12 volts dc. The power supply input circuit converts the ac line voltage (either 115 or 230 vac) into rectified and

#### 2.2.8 Switching Power Supply (Cont.)

filtered high voltage dc. The high voltage dc is chopped at a frequency of 25 KHz by a pulse width modulator presenting high voltage pulsating dc to a multiple output transformer. This transformer steps down the high voltage pulsating dc.

All output voltages are full-wave rectified through their associated diode rectifier circuits. The power-on reset signal (WOLFTRAP) is an output of a comparator circuit that forward-biases a NPN transistor once the output voltages are stabilized.

Two voltages are adjustable; +5 and +12 volts. The voltage adjustment pots are accessible from the outside of the power supply enclosure. Refer to Chapter 5 of this document for adjustment procedures and voltage measurement locations.

#### WARNING

Do not open the switching power supply under any circumstance. Extremely dangerous voltage and current levels (in excess of 300 volts DC and unlimited current) are present within the power supply.

Do not attempt to repair the switching power supply; it is field replaceable only.

After powering the unit down and disconnecting the AC power connector from the power source receptacle, allow one minute before removing the power supply to provide adequate time for any residual voltage to drain through the bleeder resistors.

Figure 2-3 CPU/Memory Bd. Block Diagram

#### CHAPTER 3

#### **OPERATION**

#### 3.1 SCOPE

This Chapter outlines the operation of the Micro VP-1 and Micro VP-2 Computer Systems. Included in this chapter are the daily-turn on and normal and emergency shut-down procedures.

#### 3.2 CONTROLS AND INDICATORS

#### 3.2.1 Power On/Off

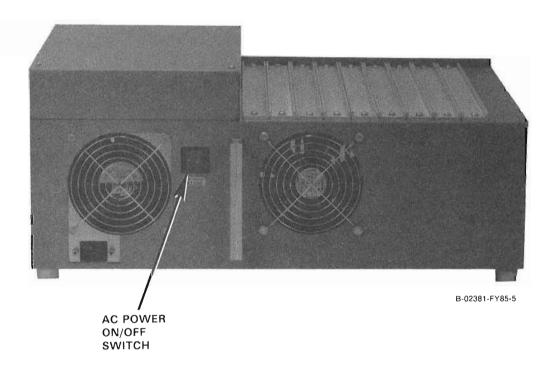

The ac power On/Off switch is mounted on the side of the Micro VP cabinet. (Ref. Fig. 3-1.)

Figure 3-1 AC Power On/Off Switch

#### 3.3 INITIAL POWER-ON PROCEDURE

- 1. Remove the covers from the Micro VP. (Ref. Chapter 5).

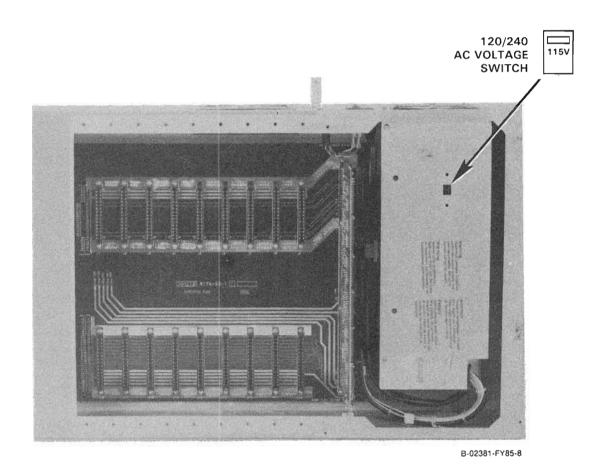

- 2. Ensure that the 120/240 ac voltage switch is set correctly.

- 3. Ensure that all boards are seated properly in the motherboard.

- 4. Plug the unit in and depress the ac power switch to the "l" position.

- 5. Check voltages and adjust if necessary as outlined in Chapter 5 of this document.

- 6. Remove power from the system, and replace covers.

#### 3.4 DAILY POWER-ON PROCEDURE

1. Whenever powering on the CPU and accociated peripherals, always Apply power first to terminal 1, then to the Micro VP, and finally the system disk.

#### 3.5 NORMAL POWER-DOWN PROCEDURE

- 1. Ensure that all users have logged off the system.

- 2. Remove power from the system disk and any other drives configured into the system.

- Depress the ac power On/Off switch to the "0" position.

#### 3.6 EMERGENCY POWER-DOWN PROCEDURE

- 1. Depress the ac power On/Off switch to the "0" position.

- 2. Remove ac plug from the power recepticle.

#### **CHAPTER 4**

#### INSTALLATION

#### 4.1 SCOPE

This chapter describes the procedures for unpacking, inspecting, and installing the Micro VP Computer System. Included in this chapter are instructions for system interconnection and power-up. Actual installation should not begin until all site requirements detailed in the Customer Site Planning Guide (700-5978), and System Installation Guide (729-0907), have been met.

#### 4.2 INSTALLATION SITE CHECK

The following conditions must be met prior to installation:

- 1. All site plans must have been approved by both the customer and a Wang service representative.

- 2. All building alterations must have been completed and inspected.

- 3. All electrical wiring, air conditioning, and telecommunications modifications must have been installed and tested.

- 4. The CE will perform a preinstallation inspection two weeks prior to delivery. At this time, the CE will check the site for compliance with Micro VP site specifications. The CE will bring any unsatisfactory condition noted to the attention of the customer for correction.

#### 4.3 UNPACKING AND INSPECTION

Each peripheral device has its own unpacking and inspection procedures. Refer to section 1.2 of this document for applicable documentation.

- Before unpacking any equipment, check all packing slips to make sure that

the proper equipment has been delivered. After checking packing slips,

inspect all shipping containers for damage (crushed corners, punctures,

etc.).

- 2. If damage is discovered during inspection, file an appropriate claim promptly with the carrier involved, and Wang Laboratories, Inc.

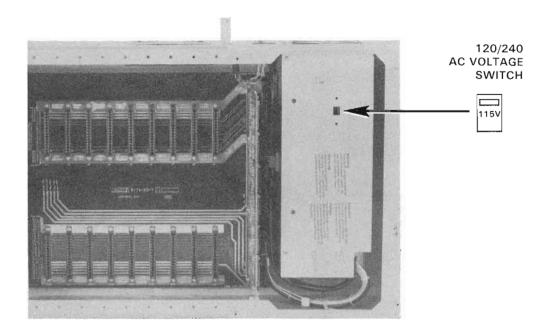

3. Remove the Micro VP from its shipping container. Remove the outer covers as outlined in Chapter 5. Inspect the unit for damaged or loosened assemblies. Also check for loose hardware. Be certain that each PC board is in its proper location and fully seated. Insure that the 120/230 volt switch is in its proper position. (Ref. Fig. 4-1)

Figure 4-1 120/240 AC Voltage Switch

#### 4.4 INSTALLATION

1. Assemble all peripherals as required for the system configuration. Refer to the applicable maintenance manual for each peripheral.

#### 4.4.1 Switch Settings

Each peripheral device must be assigned a unique address as specified in Table 4-1. A configuration with one device in a class will use the <u>first</u> <u>device address</u> for that class. Additional devices belonging to that class will have addresses sequentially assigned. Refer to Table 4-1 and assign a device address for each peripheral to be configured into the system.

| Device                                        | Address(es)                                                                         |  |  |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Keyboards<br>CRT Units<br>A.C. Tape Drive     | 001, 002, 003, 004<br>005, 006, 007, 008<br>018                                     |  |  |  |  |  |  |  |

| Tape Cassette Units<br>Printers               | 10A, 10B, 10C, 10D, 10E, 10F<br>215, 216                                            |  |  |  |  |  |  |  |

| Disk Units<br>Card Reader<br>Hopper-Feed Card | 310, 320, 330<br>517                                                                |  |  |  |  |  |  |  |

| Readers Paper Tape Readers                    | 628, 629<br>618                                                                     |  |  |  |  |  |  |  |

| Teletype                                      | 019, 01A, 01B<br>Input: 01D, 01E, 01F Output                                        |  |  |  |  |  |  |  |

| Teletype Tape Units Telecommunications        | 41D, 41E, 41F                                                                       |  |  |  |  |  |  |  |

| Output                                        | 219, 21A, 21B Input: 21D Output: 21E, 21F                                           |  |  |  |  |  |  |  |

| Parallel I/O Interface                        | 23A, 23C, 23E,<br>Input: 23B,<br>Output: 23D, 23F                                   |  |  |  |  |  |  |  |

| BCD Input Interface<br>Nine-Track Tape Unit   | 25A, 25B, 25C, 25D, 25E, 25F<br>07B, 07D, 07F                                       |  |  |  |  |  |  |  |

| Triple Controller                             | 001, 005, 009, 013 (Workstation)<br>310, 320, 330 (Disk)<br>215, 216, 217 (Printer) |  |  |  |  |  |  |  |

Table 4-1 Typical Device Addressing

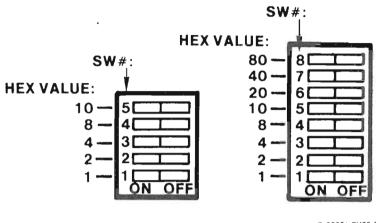

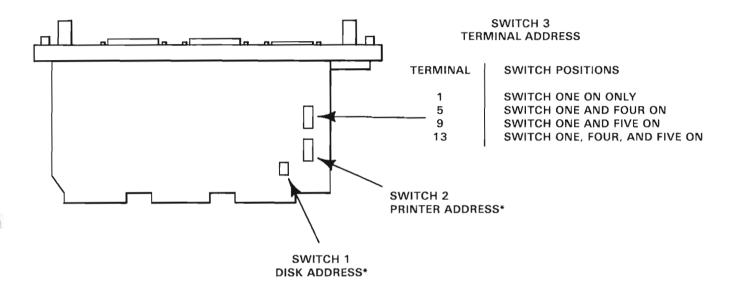

- Once an address has been assigned to each peripheral, the addresses must be inserted into the address switches located on each device controller board.

- 3. The most significant digit of the device address is used by the Operating System to identify the device type. It is not used in the device-address switch settings.

- 4. The last two digits of the device address correspond to the actual unit's address which must be set on each device controller board in the Micro VP. These digits must be broken down into binary bits and these bits are selected using the appropriate switch. (Ref Fig. 4-2 and Table 4-2.)

## ADDRESS SETTING ON PERIPHERAL DEVICE I/O CONTROLLER BOARDS

B-02381-FY85-9

Figure 4-2 Device Address Switches

#### Switch Numbers

| Digit<br>(Hex) | Sec<br>8 | ond D<br>7 | igit<br>6 | 5 | 4 | Last | Digit<br>2 | 1 |

|----------------|----------|------------|-----------|---|---|------|------------|---|

| 0              | 0        | 0          | 0         | 0 | 0 | 0    | 0          | 0 |

| 1              | 0        | 0          | 0         | 1 | 0 | 0    | 0          | 1 |

| 2              | 0        | 0          | 1         | 0 | 0 | 0    | 1          | 0 |

| 3              | 0        | 0          | 1         | 1 | 0 | 0    | 1          | 1 |

| 4              | 0        | 1          | 0         | 0 | 0 | 1    | 0          | 0 |

| 5              | 0        | 1          | 0         | 1 | 0 | 1    | 0          | 1 |

| 6              | 0        | 1          | 1         | 0 | 0 | 1    | 1          | 0 |

| 7              | 0        | 1          | 1         | 1 | 0 | 1    | 1          | 1 |

| 8              | 1        | 0          | 0         | 0 | 1 | 0    | 0          | 0 |

| 9              | 1        | 0          | 0         | 1 | 1 | - 0  | 0          | 1 |

| A              | 1        | 0          | 1         | 0 | 1 | 0    | 1          | 0 |

| В              | 1        | 0          | 1         | 1 | 1 | 0    | 1          | 1 |

| C              | 1        | 1          | 0         | 0 | 1 | 1    | 0          | 0 |

| D              | 1        | 1          | 0         | 1 | 1 | 1    | 0          | 1 |

| E              | 1        | 1          | 1         | 0 | 1 | 1    | 1          | 0 |

| F              | 1        | 1          | 1         | 1 | 1 | 1    | 1          | 1 |

Table 4-2 Device Address Switch Setting

For example, when inserting an printer address of 215, switches 5, 3, and 1 would be set to ON.

#### 4.4.1 Cont.

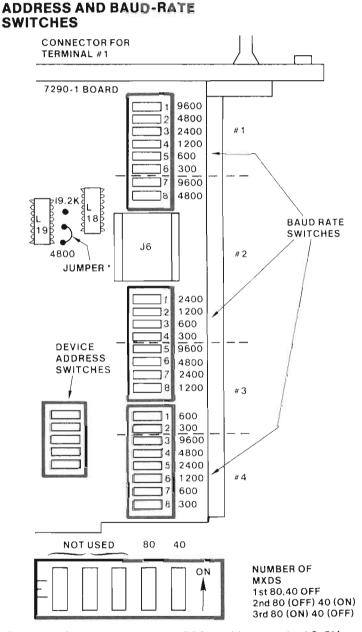

5. Other switch settings (baud rate, etc.) may be required depending on the I/O Controllers installed in the Micro VP. Some examples of these are as follows;

MXD MULTIPLEXER DEVICE

For 19.2K set switches to 4800 and jumper to 19.2K

B-02381-FY85-10

Fig. 4-3 MXD Multiplexer Device Address and Baud Rate Switches

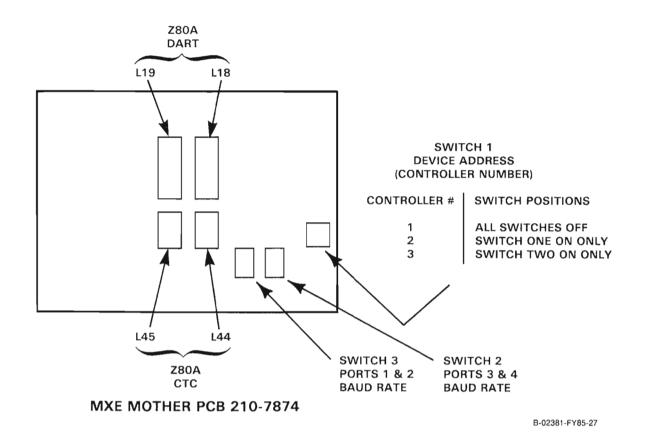

Fig. 4-4 MXE Multiplexer Device Address and Baud Rate Switches

#### MXE HARDWARE SWITCH SETTINGS

| Baud Rate |     | Switch 3 |     |     |        |     |     |     |        | Switch 2 |     |     |        |     |     |     |

|-----------|-----|----------|-----|-----|--------|-----|-----|-----|--------|----------|-----|-----|--------|-----|-----|-----|

| Port 1    |     |          |     |     | Port 2 |     |     |     | Port 3 |          |     |     | Port 4 |     |     |     |

|           | 1   | 2        | 3   | 4   | 5      | 6   | 7   | 8   | 1      | 2        | 3   | 4   | 5      | 6   | 7   | 8   |

| 110       | OFF | OFF      | OFF | OFF | OFF    | OFF | OFF | OFF | OFF    | OFF      | OFF | OFF | OFF    | OFF | OFF | OFF |

| 134.5     | ON  | OFF      | OFF | OFF | ON     | OFF | OFF | OFF | ON     | OFF      | OFF | OFF | ON     | OFF | OFF | OFF |

| 150       | OFF | ON       | OFF | OFF | OFF    | ON  | OFF | OFF | OFF    | ON       | OFF | OFF | OFF    | ON  | OFF | OFF |

| 200       | ON  | ON       | OFF | OFF | ON     | ON  | OFF | OFF | ON     | ON       | OFF | OFF | ON     | ON  | OFF | OFF |

| 300       | OFF | OFF      | ON  | OFF | OFF    | OFF | ON  | OFF | OFF    | OFF      | ON  | OFF | OFF    | OFF | ON  | OFF |

| 600       | ON  | OFF      | ON  | OFF | ON     | OFF | ON  | OFF | ON     | OFF      | ON  | OFF | ON     | OFF | ON  | OFF |

| 1200      | OFF | ON       | ON  | OFF | OFF    | ON  | ON  | OFF | OFF    | ON       | ON  | OFF | OFF    | ON  | ON  | OFF |

| 2400      | OFF | OFF      | OFF | ON  | OFF    | OFF | OFF | ON  | OFF    | OFF      | OFF | ON  | OFF    | OFF | OFF | ON  |

| 4800      | OFF | ON       | OFF | ON  | OFF    | ON  | OFF | ON  | OFF    | ON       | OFF | ON  | OFF    | ON  | OFF | ON  |

| 9600      | OFF | OFF      | ON  | ON  | OFF    | OFF | ON  | ON  | OFF    | OFF      | ON  | ON  | OFF    | OFF | ON  | ON  |

| 19600     | ON  | OFF      | ON  | ON  | ON     | OFF | ON  | ON  | ON     | OFF      | ON  | ON  | ON     | OFF | ON  | ON  |

\*SWITCH SETTINGS ARE IDENTICAL TO NORMAL HARDWARE SWITCH SETTINGS (REF. FIG. 4-2).

B-02381-FY85-28

Fig. 4-5 22C32 Triple Controller Switches

#### 4.4.2 Cabling

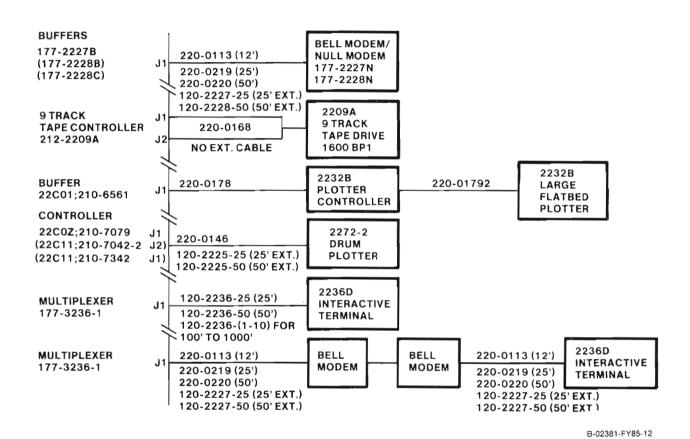

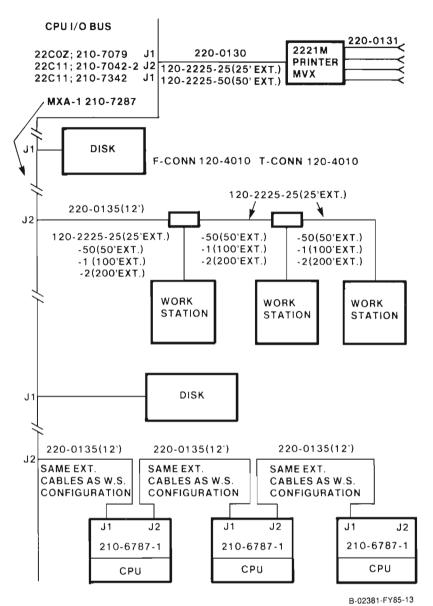

1. Exact system cabling will differ with each system configuration. Below are some examples of the cabling required for typical configurations.

#### **Printer Interface** CONTROLLER BUFFERS 2201L CHARACTER 220-0181 22C01:210-6561 J1 120-2201-25(25' EXT.) PRINTER 120-2201-50(50' EXT.) 2221W 22C02;210-7079 J1 {22C11;210-7042-2) J2} {22C11;210-7342) J1) 220-105-3 MATRIX PRINTER 120 CPS 120-2225-25(25' EXT.) 120-2225-50(50' EXT.) 2231W 220-0105-1 MATRIX SAME AS 2221W PRINTER 120 CPS EXT. SAME AS 2221W MATRIX 220-0156 SAME AS 2221W PRINTER 110 CPS EXT. SAME AS 2221W 2261W 220-0171 MATRIX SAME AS 2221W PRINTER EXT. SAME AS 2221W 240 LPM 2263 CHAIN PRINTER 400/600 LPM 220-0105-3 SAME AS 2221W EXT. SAME AS 2221W 2271/2271P 220-0156 BI-DIRECTIONAL WRITER/PLOTTER SAME AS 2221W EXT. SAME AS 2221W 15 CPS 2281/2281P DAISY WRITER 220-0161 SAME AS 2221W EXT. SAME AS 2221W 220-0105-3 SAME AS 2221W 2231W-3 GRAPHIC CRT EXT. SAME AS 2221W PLOTTER 220-0105-3 MATRIX PLOTTER 120 CPS EXT. SAME AS 2221W

Fig. 4-6 Printer Interface Cabling

Fig. 4-7 Disk Interface Cabling

Fig. 4-8 Telecommunications, Tapes, Plotters, and Terminal Interface Cabling

Fig. 4-9 Multiplexer Cabling

#### 4.5 INITIAL POWER-UP

- 1. With the covers removed from the system (ref. chapter 5), ensure that the 120/240 ac line voltage switch is set correctly. (Ref. Fig. 4-9).

- 2. Ensure that the CPU/Memory Bd. is seated properly in slot 1 and all I/O controllers are fully seated in the motherboard.

- 3. Apply power to terminal 1, the Micro VP, and finally the system disk.

- 4. Check operating voltages and adjust if necessary as outlined in Chapter 5.

- 5. With the operating voltages set, replace all system covers. (Ref. chapter 5).

741-1668 4-11 COMPANY CONFIDENTIAL

#### 4.5 INITIAL POWER-UP CONT.

Fig. 4-10 120/230 AC Line Voltage Select Switch

#### NOTE

Operating voltages must be checked and adjusted if necessary on all peripherals attached to the system. Please refer to the appropriate maintenance manual (section 1.2) for detailed instructions on checking and adjusting these voltages.

#### 4.6 SYSTEM VERIFICATION

#### 4.6.1 System Diagnostics

Once power has been applied, the terminal connected as workstation 0 should be displaying the following screen;

MOUNT SYSTEM PLATTER PRESS RESET

Place the System Platter Disk into the system drive and press the RESET key on the keyboard. (Press RESET if the terminal is model #2336DE, and SHIFT RESET if the terminal is model #2336DW.)

The following screen should now be displayed; KEY SF'? Depress the special function key which corresponds to the drive you wish to IPL from. Disk addresses start with SF'00 and increment thereafter. For example; SF'00 accesses a disk address of 310, SF'01 an address of B10, SF'02 an address of 320, SF'03 an address of B20, etc. 5. The screen should display; \*\*\*\*SYSTEM 2200\*\*\*\* Select item with SPACE & BACKSPACE MEMORY XXXXK Key RUN to execute, CLEAR or PREV SCRN for previous screen Terminal X MVP BASIC-2 Diagnostics Space down to Diagnostic and key RUN. The screen will appear as follows; 6. \*\*\*\*CUSTOMER DIAGNOSTIC MENU\*\*\*\* Select item with SPACE & BACKSPACE MEMORY XXXXK Terminal X Key RUN to execute, CLEAR or PREV SCRN for previous screen CPU Instructions

CPU Instructions

Control Memory

Data Memory

CPU Registers

All of the above

7. Space down to All of the above and key RUN. The diagnostics will begin immediatly. As each set of tests are completed the Chain Mode Pass will increment. These tests will run continuously until RESET is keyed to terminate the diagnostics.

#### NOTE

Please refer to Chapter 7 of this document for interpretations of all CPU diagnostics mentioned here.

- 8. When a sufficient number of successful test passes have occured (5 to 10 passes), key RESET.

- 9. The system software must now be configured to support the attached peripherals.

### 4.7 PARTITION GENERATION

1. After all required system diagnostics have successfully completed the partitions must be generated. Apply power to the system or key RESET. The screen will appear as follows;

MOUNT SYSTEM PLATTER PRESS RESET

3. Mount the system disk and press RESET. The screen appears;

KEY SF'?

4. Depress the special function key which corresponds to the drive containing the operating system. Disk addresses start with SF'00 and increment thereafter. For example; SF'00 accesses a disk address of 310, SF'01 an address of Bl0, SF'02 an address of 320, SF'03 an address of B20, etc.

## NOTE

If the wrong SF key was depressed (there was no system disk at the device specified), the following screen will appear;

\*\*\*SYSTEM ERROR (DISK 00XX)\*\*\*

PRESS RESET

If this error occurs, press RESET, then the correct SF key.

5. The screen will now appear:

\*\*\*\*SYSTEM 2200\*\*\*\*

Select item with SPACE & BACKSPACE

Key RUN to execute, CLEAR or PREV SCRN for previous screen

MEMORY xxxxK Terminal X

- MVP BASIC-2 Diagnostics

- 6. Select MVP BASIC-2 and key RUN. The following screens will now appear:

LOADING: MVP BASIC-2 RELEASE X.X

#### \*\*\*WANG 2200MVP PARTITION GENERATION PROGRAM\*\*\*

LIST OF STORED CONFIGURATIONS (# PARTITIONS)

1. current (X)

2. ...

LIST OF OPTIONS

SF'00 - CLEAR PARTITIONS

SF'01 - CLEAR DEVICE TABLE

SF'02 - DIVIDE MEM. EVENLY

SF'04 - EDIT PARTITIONS

SF'05 - EDIT DEVICE TABLE

SF'06 - EDIT \$MSG

SF'08 - LOAD CONFIGURATION

SF'09 - SAVE CONFIGURATION

SF'10 - DELETE CONFIGURATION

SF'15 - EXECUTE

FN - HELP

CONFIGURATION "CURRENT" LOADED. NAME OF CONFIGURATION TO LOAD?

7. Configuration parameters must now be entered into the Operating System. If partition-generation modules have been previously defined, a list of those module names will appear in the @GENPART menu screen. The user can select and load one of these modules by typing in the name of the module and pressing RETURN, and SF'15. If the user wishes to define a new partition module, he can do so by depressing the appropriate Special Function keys. This will initiate partition generation.

Descriptions of @GENPART SF Key Options:

- <u>SF'00 Clear Partitions</u>: Clears partition configuration parameters currently in memory, allowing the user to specify the total number of terminals and partitions in each bank, then automatically advances to SF'04 (Edit Partitions). Any number of partitions between 1 and 16 is allowable.

- SF'01 Clear Device Table: Clears Master Device Table parameters currently stored in memory, resets the default peripheral addresses to 215 (printer), 310 (system disk), and 320 (secondary disk), allocates these devices to all users, then advances to SF'05 (Edit Device Table). Default device addresses can then be edited.

- <u>SF'02 Divide Memory Evenly:</u> Divides remaining User Memory equally among the number of partitions specified with SF'04.

- **SF'04 Edit Partitions**: Displays and allows editing of partition parameters such as size, terminal assignment, programmability, and name of bootstrap program. SF'04 <u>does not</u> allow addition or deletion of defined partitions in an existing configuration.

- <u>SF'05 Edit Device Table:</u> Displays and allows editing of device addresses for all peripherals. All peripherals connected directly to I/O controllers must be specified in the Master Device Table.

- <u>SF'06 Edit \$MSG:</u> Displays and allows editing of a user-defined broadcast message that will be displayed on each terminal's CRT whenever the READY message is displayed. This message appears on line 0 of the CRT, immediately above the READY message.

- <u>SF'08 Load Configuration:</u> Loads a named configuration from the Configuration File, which is located on the system disk. To modify and/or execute any previously defined configuration other than "current", this option must be used.

- <u>SF'09 Save Configuration:</u> Used to save a system configuration in the Configuration File under a user-specified name (up to eight characters in length). If the user specifies a configuration name already used, @GENPART will verify that the user desires to replace the old configuration on disk file with the configuration currently in memory.

- <u>SF'10 Delete Configuration:</u> Deletes a configuration from the Configuration File on the System Disk.

- SF'15 Execute Configuration: Allows the operator to first review, and then to execute, a configuration. This configuration will automatically be saved in the Configuration File under the name "current" when the configuration is executed. Once a configuration has been executed, the system may be reconfigured again only after the Master Initialization procedure has been repeated.

- FN Help: Displays @GENPART operating instructions.

In general, the order of executing these @GENPART options is as follows;

- 1. SF'08 to load a configuration

- 2. SF'00 to modify this configuration by adding or deleting partitions

- 3. SF'04 to create the new partition parameters

- 4. SF'05 to create the Master Device Table

- 5. SF'06 to create the broadcast message

- 6. SF'09 to save the configuration with a name other than "current"

- 7. SF'15 to execute the configuration

These steps will create a permanent system configuration.

The following section outlines the screen loads given when in @GENPART

## Load a Configuration (SF'08)

| LIST OF ST    | ORED CONFIGURATION current | (#PARTITIONS) (1)              |

|---------------|----------------------------|--------------------------------|

| CONFIGURATION | 'current' LOADED.          | NAME OF CONFIGURATION TO LOAD? |

The last configuration executed (called 'current') is automatically loaded. To load any other configuration, enter its name, then press RETURN.

# Clear Partitions (SF'00)

AVAILABLE USER MEMORY = xxK REMAINING USER MEMORY = xxK NO. OF TERMINALS? NO. OF PARTITIONS?

The program responds with a display that requests the total number of terminals that are to be configured into the system and the number of partitions that will be created. Available User Memory is automatically calculated and displayed. Remaining memory is updated and displayed as memory is allocated to the partitions. When all information has been entered, and RETURN is pressed, the program automatically invokes SF'04 (Edit Partition) to allow the editing of partition parameters.

# Edit Partitions (SF'04)

| PARTITION | SIZE | (K) | TERMINAL | PROGRAMMABLE | PROGRAM |

|-----------|------|-----|----------|--------------|---------|

| 1         |      |     | 1        | Υ            |         |

| 2         |      | •   | 2        | Υ            |         |

| 3         |      |     | 3        | Y            |         |

| 4         |      |     | 4        | Υ            |         |

EDIT WHICH PARTITION (DEFAULT = 1)?

This option displays parameters for all partitions and initiates a cycle of prompts for the altering of these parameters. The cycle recurs until another option is selected. The user is thus allowed to modify parameters for each partition. The display is updated each time an item is entered.

For example to enter parameters for partition #2, enter 2 then key RETURN. An asterisk appears beside the number of the partition whose parameters are being edited, and the following series of prompts will be displayed in succession at the bottom of the screen:

PARTITION SIZE (default = 0)

Any value greater than 1.25K and less than the amount of remaining User Memory is a valid response. Note that the default value is not a valid response unless all remaining user memory is to be divided evenly. After the amount of user memory allocated to this partition has been entered, the screen will appear;

TERMINAL (default = 2)?

Enter the terminal number which will be assigned to this partition. The following screen will appear;

ENABLE PROGRAMMING (Y or N)?

By default, programming is allowed for all partitions; however, to prevent inadvertant modification of certain programs, it may be desirable to disable the programming mode in some partitions. After responding to this prompt, the name of a program to be automatically loaded into this partition will now be requested. The screen appears as follows;

NAME OF PROGRAM TO LOAD?

Enter the name of the program and key RETURN. When the configuration is executed, the program will be automatically loaded from the system disk into its' partition, and will then be run.

Other partitions which require modification may be serviced at this time following the same procedure. Once all partitions have been edited (if necessary), SF'05 is used to leave the "Edit Partition" cycle and invoke the "Edit Master Device Table" option. With this option selected, the screen will appear as follows;

| DEVICE | PARTITION | DEVICE | PARTITION |

|--------|-----------|--------|-----------|

| 1.     | /215      | all    | 17.       |

| 2.     | /310      | all    | 18.       |

| 3.     | /320      | all    | 19.       |

|        |           |        |           |

| •      |           |        | •         |

| •      |           |        | •         |

| 16.    |           |        | 32.       |

EDIT WHICH ENTRY (default = 1)?

Enter the device number of the item you wish to edit. An asterisk (\*) will appear next to the device number selected. The screen appears as follows;

DEVICE ADDRESS (default = /000,/000 to delete entry)?

Enter the device address, then RETURN. The screen now appears;

ALLOCATE DEVICE TO WHICH PARTITION (default = all)?

Enter the partition number to allocate the peripheral and its controller. These screens will continue, in order to allow the user to edit all entries in the Master Device Table. When the parameters for all peripheral/partition allocations have been specified, the user can select another Special Function option to exit the "Edit Device Table" mode.

Broadcast Message (SF'06) When SF'06 is depressed, the following display appears at the bottom of the screen;

| BROADCAST MESSAGE: |  |

|--------------------|--|

You may now enter a broadcast message. While in the broadcast message mode, all S.F. keys revert to their system defined EDIT functions. The S.F. keys cannot be used for any @GENPART function until the entry of the broadcast message is complete.

<u>Save Configuration (SF'09)</u> When SF'09 is depressed, the following display appears at the bottom of the screen;

CHECK CONFIGURATION TO SAVE. CONFIGURATION NAME? ------

To save a configuration, ensure that the system diskette or hard disk is write-enabled, enter a unique name for the configuration, and key RETURN. The configuration currently in memory will automatically be saved under the name 'current'. However, each time a new configuration is executed, the new parameters replace the old parameters in the 'current' file.

Execute Configuration (SF'15) Once all parameters of a configuration have been defined, the system configuration can be executed. When SF'15 is depressed the configuration table will appear at the bottom of the screen, along with a prompt requesting the operator to verify the configuration parameters to be executed.

CHECK CONFIGURATION OK TO EXECUTE (Y or N)?

If Y (RETURN) is chosen, the configuration will be executed. If N (RETURN) is entered, the system returns to the beginning of the "Edit Partition" cycle. Once executed, a configuration can only be changed by first Master Initializing the system, and then, by specifying the new parameters.

<u>Delete a Configuration (SF'10)</u> When this is depressed, the following prompt will request which configuration to delete;

DELETE WHICH CONFIGURATION?

Enter the name of the configuration to be deleted, then RETURN. The configuration will be deleted from the system disk.

## 4.8 GENERATING EVENLY-DIVIDED PARTITIONS

To generate evenly-divided partitions, first load the BASIC-2 operating system by keying in the appropriate SF' key on terminal 1. Next, key SF'00 to initialize all terminals and clear the partitions. The prompt "NO. OF TERMINALS?" refers to the number in each bank of user memory. Answer this prompt with the number of terminals attached, then answer the "NO. OF PARTITIONS?" with the same number, then key EXECUTE. Now key SF'02 to divide memory evenly in each bank. Available memory will now be apportioned equally among the number of terminals entered earlier. Finally, key SF'15 to execute the configuration. A prompt will appear "CHECK CONFIGURATION. OK TO EXECUTE (Y or N)?". Enter Y and key EXECUTE if the configuration is correct. All terminals should now display "READY (BASIC-2)". Each terminal can now be used as an independent processor.

### 4.9 CUSTOMIZING PARTITION GENERATION

The user may write his own partition generation utility if he desires. Directions for this are given in the BASIC-2 Language Reference Manual.

## 4.10 SYSTEM TURNOVER TO CUSTOMER

When all diagnostics required for system installation have been successfully completed, and the software has been correctly completed, the system can be turned over to the customer. To turn over the system to the customer:

- 1. Demonstrate to the customer or to the responsible computer operator the disk initialization procedure.

- 2. Perform the Daily Power-Down procedure (ref. section 3.4), and explain each step to the applicable customer personnel.

- 3. Perform the Daily Power-Up procedure (ref. section 3.5), and explain each step to the applicable customer personnel.

- 4. Allow the customer to test the system using his programs. If the customer is satisfied with the operation of the system, officially turn the system over to the customer. This should be a verbal notification given by the CE performing the installation.

#### CHAPTER 5

## PREVENTIVE MAINTENANCE

### 5.1 SCOPE

This chapter contains preventive maintenance, adjustment/alignment, and removal/replacement procedures for the Micro VP-1 and Micro VP-2 Computer Systems. This document only provides information for the maintenance of the CPU systems themselves. Maintenance for attached peripherals is documented in the appropriate product manual(s).

# 5.2 SPECIAL TOOLS AND EQUIPMENT

No special tools or equipment are required for maintaining the Micro VP Computer Systems.

### 5.3 MAINTENANCE PROCEDURES

To ensure proper operation, the Micro VP must have periodic preventive maintenance consisting of inspection, cleaning, and adjustments. The following preventive maintenance procedures should be performed in conjunction with the preventive maintenance done to the system disk drive. This assumes a clean operating environment and normal operating time of 40 hours per week. A dusty environment or a substantial increase in the operating time will require that these preventive maintenance procedures be carried out more frequently. In addition, these procedures should be performed during each unscheduled service call.

## 5.3.1 Central Processing Unit

The following procedure should be followed for the Preventive Maintenance of the Micro VP CPU:

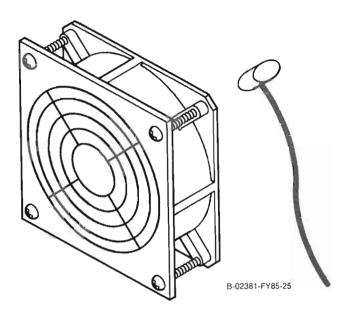

- 1. Check the cooling fan for proper operation.

- Clean the unit as outlined below.

- a. Remove the top cover from the system.

- b. Remove the I/O controllers and the CPU/Memory board.

- c. Remove all dust from the interior of the unit.

- d. Clean the finger connectors of each PCB.

- e. Reinstall all PC boards into the system.

- f. Using a mild detergent and a soft cloth or sponge, clean the CPU cabinetry. Do not use abrasive or corrosive chemicals.

- Check the operating voltages and ripple as defined in Section 5.4 of this document.

- Replace the top cover on the system and run diagnostics as required to ensure proper operation of the equipment.

#### 5.4 ALIGNMENTS AND ADJUSTMENTS

## 5.4.1 Voltage Adjustments

- 1. Remove the top cover from the system.

- 2. Ensure that the 120/240 AC line voltage select switch is set properly.

- 3. Depress the ac-power switch to the "1" position.

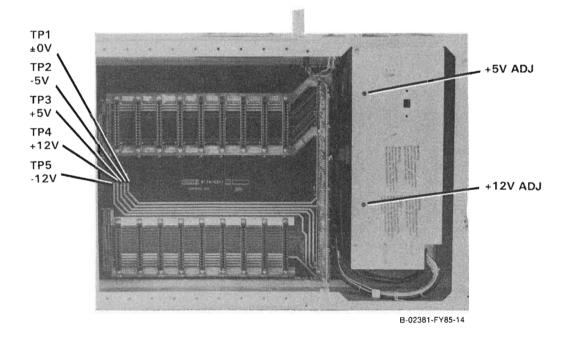

- 4. Using a Fluke Digital Voltmeter or equivalent, check -5vdc, +5vdc, +12vdc, and -12vdc at TP2 through TP5, on the motherboard. TP0 may be used as a ground reference. (Ref. Fig. 5-1). Refer to table 5-1 for the correct operating voltage levels.

- 5. +5vdc an +12vdc are the only adjustable voltages. Refer to Fig. 5-1 and adjust these voltages as required to achieve the correct operating voltage levels.

Do not open the switching power supply under any circumstance. Extremely dangerous voltage and current(in excess of 300 volts DC and unlimited current are present within the power supply.

Do not attempt to repair the switching power supply; it is field replaceable only.

After powering the unit down and disconnecting the AC power connector from the power source receptacle, allow one minute before removing the power supply to provide adequate time for any residual voltage to drain through the bleeder resistors.

Fig. 5-1 Operating Voltage Testpoints

| VOLTAGE | LIMITS                 | RIPPLE   |

|---------|------------------------|----------|

| +5vdc   | +4.95vdc to +5.05vdc   | 15mv p-p |

| -5vdc   | -4.95vdc to -5.05vdc   | 15mv p-p |

| +12vdc  | +11.95vdc to +12.05vdc | 15mv p-p |

| -12vdc  | -11.95vdc to -12.05vdc | 15mv p-p |

Table 5-1 Operating Voltage Limits

If any voltage is missing or the +5 and/or +12 volts can not be adjusted, remove all PCB boards (ref. section 5.5 of this document) and perform the adjustment procedure again. If the voltage can be adjusted, one or more PCB is possibly causing the problem, however the power supply itself should not be ruled out. If a PCB is found to be at fault, replacement of the defective board is required.

If the voltage problem exists with no PCB boards installed, replacement of the Switching Power Supply is required. Refer to the Removal and Replacement procedure described in section 5.5.

#### 5.5 REMOVAL AND REPLACEMENT PROCEDURES

## 5.5.1 Top Cover Removal

To remove the top cover of the Micro VP system;

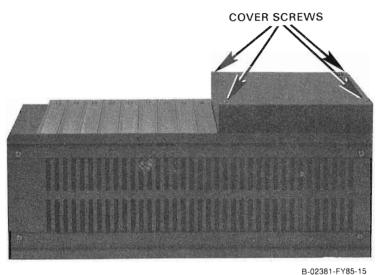

- 1. Remove 4 phillips-head screws on top cover (ref. Fig. 5-2).

- 2. Carefully lift cover off the unit.

## 5.5.2 Top Cover Replacement

To replace the top cover of the Micro VP system;

- 1. Place cover on unit.

- 2. Insert 4 phillips-head screws and tighten.

Figure 5-2 Top Cover Screws

# 5.5.3 Switching Power Supply Removal

To remove the Switching Power Supply from the Micro VP system;

- 1. Depress the ac power on/off switch to the "0" position.

- 2. Remove the ac plug from the power receptacle.

- 3. Wait 1 minute for residual voltage to drain through the bleeder resisters. If top cover is installed on the system, remove it as described in Section 5.5.1.

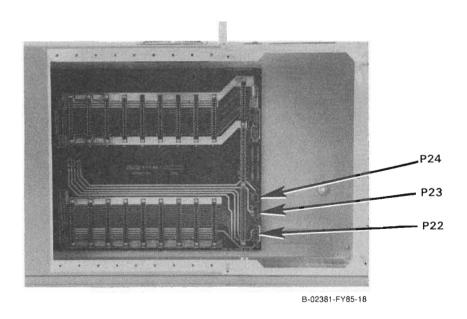

- Remove the CPU/Memory Bd. from the system (Ref. section 5.5.5), and set it aside. Unplug connectors P22, P23, and P24 from the motherboard (Ref. Fig. 5-6).

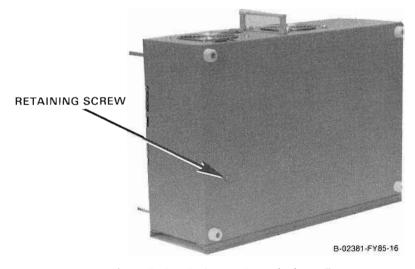

- Remove the phillips head screw from the bottom of the system (Ref. Fig. 5-3).

Fig. 5-3 Bottom Retaining Screw

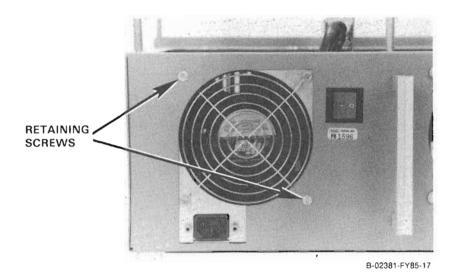

- 6. Remove the 2 hex head screws from the system as shown in Fig. 5-4.

- 7. Unplug the following connectors;

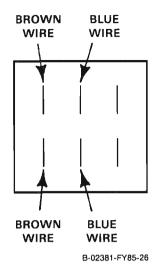

The 4 lug connectors on the ac power on/off switch. (Ref. Fig. 5-6).

The power connector to the system cooling fan.

8. Carefully lift the power supply out of the unit.

Fig. 5-4 Power Supply Retaining Screws

Fig. 5-5 Motherboard Connectors

Fig. 5-6 AC Power On/Off Switch Wiring

## 5.5.4 Switching Power Supply Replacement

To replace the Switching Power Supply in the Micro VP system;

- 1. Insert the power supply into the unit.

- 2. Insert P22, P23, and P24 into their proper recepticles in the motherboard.

- 3. Reconnect the power connector to the system cooling fan.

- 4. Reconnect the 4 lug connectors on the ac power on/off switch. The correct wiring for these is shown in Fig. 5-6.

- 5. Insert the 2 hex head screws into the system and tighten. (Ref. Fig. 5-4.)

- 6. Insert the phillips head screw into the system and tighten. (Ref. Fig. 5-3.)

- 7. Re-install the CPU/Memory Bd (Ref. section 5.5.6).

- 8. Replace the top cover onto the unit.

## 5.5.5 CPU/Memory Board Removal

To remove the CPU/Memory board from the Micro VP system;

- 1. Ensure that ac power to the unit has been disconnected.

- 2. Remove the top cover from the system.

- 3. Carefully lift the CPU/Memory board from its motherboard slot and out of the unit.

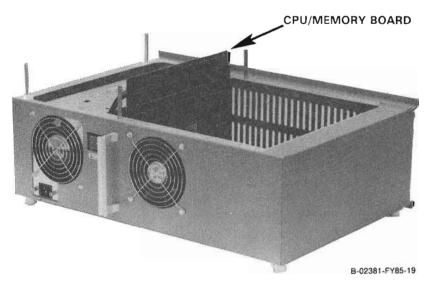

## 5.5.6 CPU/Memory Board Replacement

To replace the CPU/Memory board in the Micro VP system;

- 1. Insert the CPU/Memory board into its slot in the Micro VP motherboard. (Ref. Fig. 5-7).

- 2. Install the top cover onto the system.

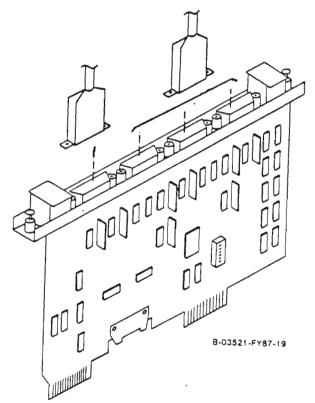

Figure 5-7 CPU/Memory Board

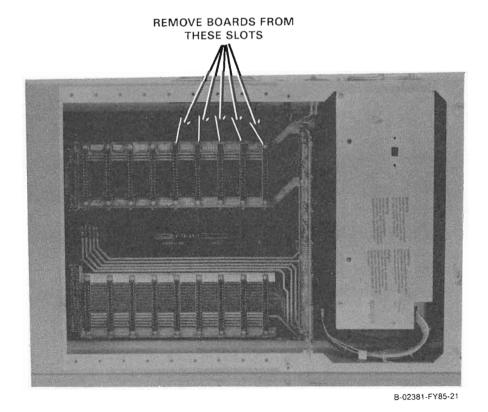

## 5.5.7 I/O Controller Board Removal

To remove an I/O Controller board from the Micro VP system;

- 1. Ensure that ac power to both the unit and the connected peripheral has been disconnected.

- 2. Remove any external cabling to the I/O controller board.

- Unscrew the two screws securing the I/O Controller Board to the unit.

- 4. Carefully lift the unit from its motherboard slots and out of the system.

## 5.5.8 I/O Controller Board Replacement

To replace an I/O Controller board in the Micro VP system;

- Remove AC power from both the CPU and the peripheral to be connected.

- Insert the I/O Controller board into a slot in the Micro VP motherboard.

- 3. Secure the board to the system with two screws.

- 4. Connect any external cabling to the I/O Controller.

## 5.5.9 Motherboard Removal

To remove the Motherboard from the Micro VP system;

- 1. Ensure that AC power has been removed from the system.

- 2. Remove top cover from the system.

- 3. Remove external cabling from the I/O boards.

- 4. Remove all I/O boards.

- 5. Remove CPU/Memory board.

- 6. Unplug connectors P22, P23, and P24 from the motherboard. Ref. Fig. 5-5.

- 7. Remove 42 phillips-head retaining screws and lift motherboard from the system.

## 5.5.10 Motherboard Replacement

To replace the motherboard in the Micro VP system;

- 1. Insert motherboard into the unit.

- 2. Insert 42 phillips-head retaining screws and tighten.

- 3. Plug connectors P22, P23, and P24 into the motherboard. Ref. Fig. 5-5.

- 4. Install CPU/Memory board.

- 5. Install all I/O boards and reconnect any associated cabling.

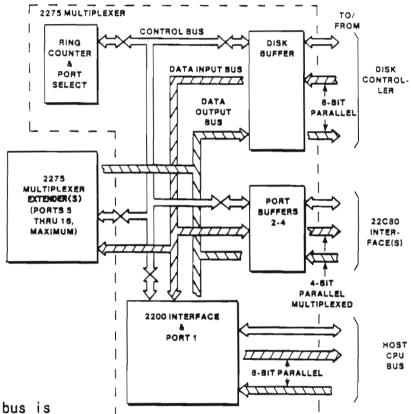

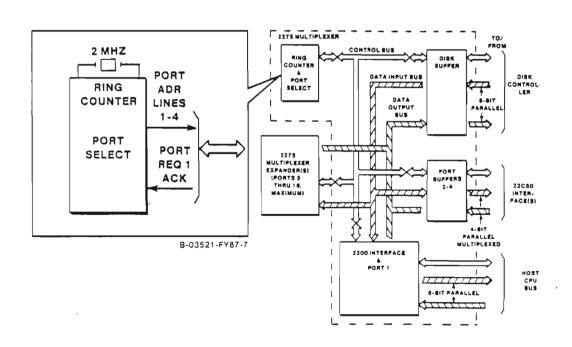

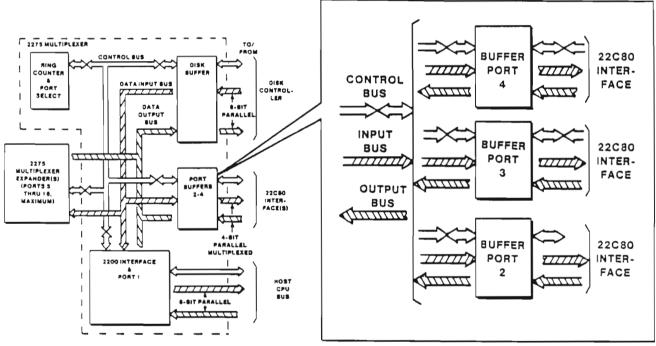

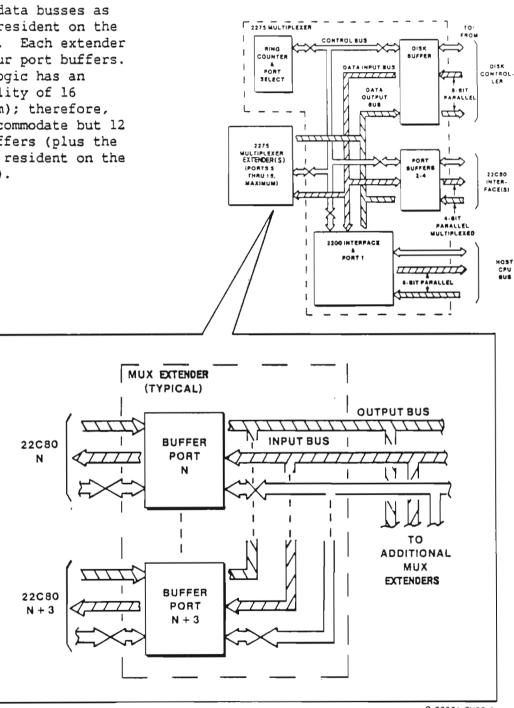

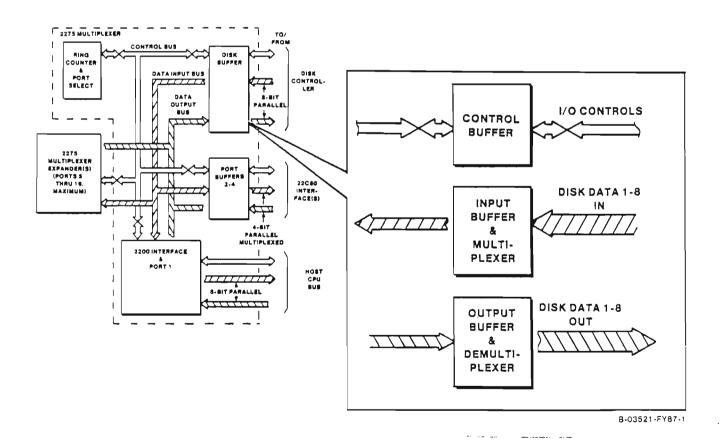

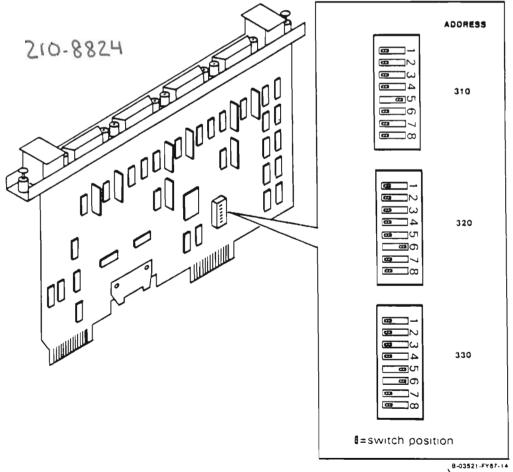

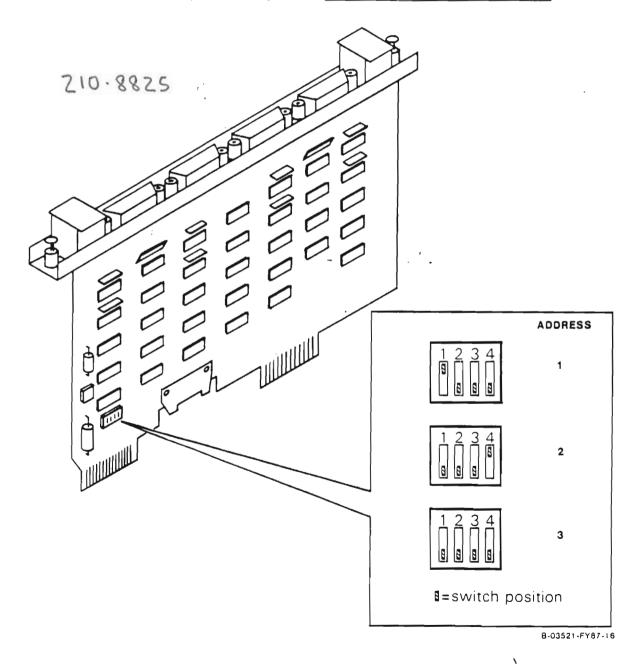

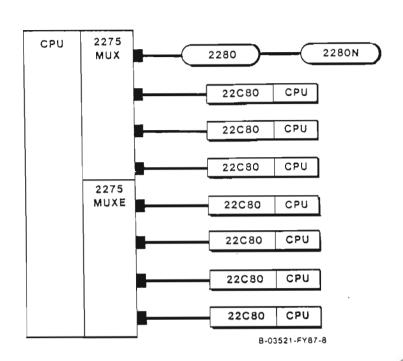

- 6. Install top cover on the system.