# Model 44B Disk Drive

**Maintenance Manual**

#### WARRANTY

The Diablo Model 44B Disk Drive is warranted against defects in materials and workmanship for 1 year from the date of shipment. Any questions with respect to the warranty should be taken up with your Diablo Sales Representative.

All requests for repairs should be directed to the Diablo Repair Depot in your area. This will assure you the fastest possible service.

# PREFACE

This preliminary maintenance manual for the Model 44B Disk Drive contains the latest information available at the time of writing. Subsequent engineering design changes will be accounted for in later editions of the manual.

Diablo Systems, Incorporated, reserves the right to make changes and/or improvements' to its products without prior notification, and without incurring any obligation to incorporate such changes or improvements in units previously sold or shipped.

Information in this manual is proprietary, and is not to be reproduced or disseminated in any form without written consent of Diablo Systems, Inc. Comments on this manual or its use are invited. Please address all comments to:

> Manager, Technical Publications Customer Service Department Diablo Systems, Inc. 3190 Corporate Place Hayward, CA 94545

United States and foreign Diablo products are covered by U.S. and foreign patents and/or patents pending.

"Diablo" is a trademark of Xerox Corporation.

"Xerox" is a trademark of Xerox Corporation.

©Copyright 1976 by Diablo Systems, Inc., Hayward, California

Publication No. 81903-00 - First Edition

| SECTION 1 - GENERAL DESCRIPTION AND SPECIFICATIONS           |              |

|--------------------------------------------------------------|--------------|

| 1.1 Operational Characteristics                              | 1-1          |

| 1.2 General Specifications                                   | 1-3          |

| 1.3 Related Documents                                        | 1-3          |

|                                                              |              |

| SECTION 2 - INSTALLATION AND OPERATION                       |              |

| 2.1 Installation                                             | 2-1          |

| 2.1.1 Dimensions                                             | 2-1          |

| 2.1.2 Unpacking/Packing                                      | 2-1          |

| 2.1.2.1 Unpacking Procedure                                  | 2-1          |

| 2.1.2.2 Packing Procedure                                    | 2-1          |

|                                                              | 2-4          |

|                                                              | 2-4          |

| 2.2 Operating Instructions                                   | 2-6          |

| 2.2.1 Operating Precautions                                  | 2-6          |

| 2.2.1.1 Disk Drive Operation                                 | 2-6          |

| 2.2.1.2 Cartridge Handling and Storage                       |              |

|                                                              | 2-7          |

| 2.2.2 Controls and Indicators                                |              |

| 2.2.2.1 LOAD/RUN Switch                                      |              |

| 2.2.2.2 LOAD Indicator                                       |              |

|                                                              |              |

|                                                              |              |

|                                                              |              |

|                                                              |              |

|                                                              |              |

|                                                              |              |

| SECTION 3 - INTERFACE INFORMATION                            |              |

| 3.1 AC Power Requirements                                    | 3-1          |

| 3.2 Signal Interface                                         |              |

| 3.2.1 Interface Connector                                    |              |

|                                                              | 3-1          |

| 3.2.2.1 Input Lines                                          |              |

| 3.2.2.2 Output Lines                                         |              |

| 3.2.2.3 Output Line Drive Capability                         |              |

|                                                              | 3-7          |

| 3.3 Input/Output Cables                                      | 3-9          |

|                                                              | 3-9          |

| 3.3.1 Flat Cable                                             | 3-9          |

|                                                              | 3-11         |

| 3.3.3 Cable Lengths                                          | 3-11         |

| 3.4 Terminating Resistors                                    | 3-11         |

| 3.5 Double Frequency Recording                               | 3-11         |

| 3.6 Disk Format                                              | 3-14         |

| 3.6.1 Sector Mark Format                                     | 3-18         |

| 3.6.2 Typical Write Format, Write Data and Read Operations . | 3-19         |

| 3.6.2.1 Typical Write Format Operation                       | 3-19         |

| 3.6.2.2 Typical Write Data Operation                         | 3-19         |

| 3.6.2.3 Typical Read Operation                               | 3-20         |

| 3.6.3 Address Mark Format                                    | 3-20         |

| 3.6.3.1 Write Data                                           | 3-20<br>3-22 |

| 3.6.3.2 Data Read                                            | 3-22         |

5

-

e

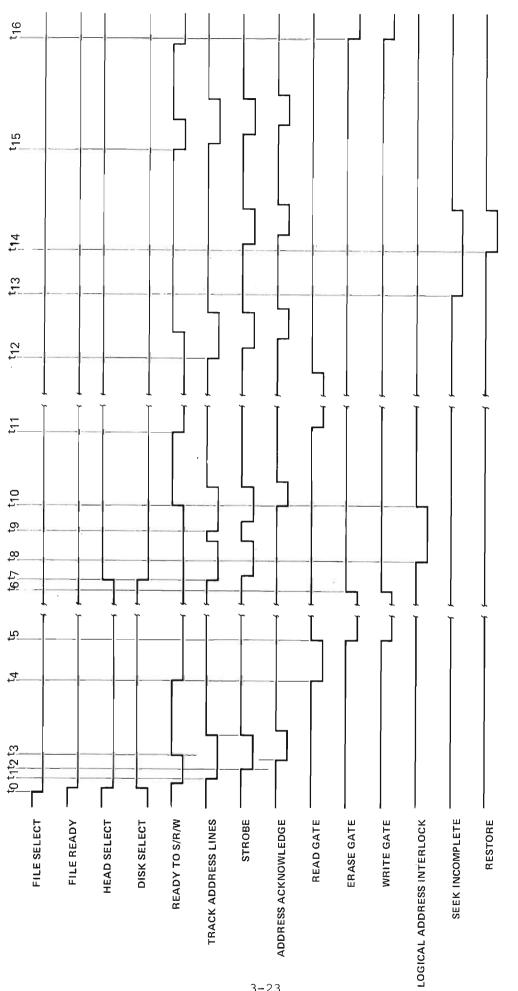

| 3.7 Typical St    | ignal Timing at the Interface               | 3-22         |

|-------------------|---------------------------------------------|--------------|

| SECTION 4 - PRINC | IPLES OF OPERATION                          |              |

|                   |                                             | 4-1          |

|                   | l Description                               |              |

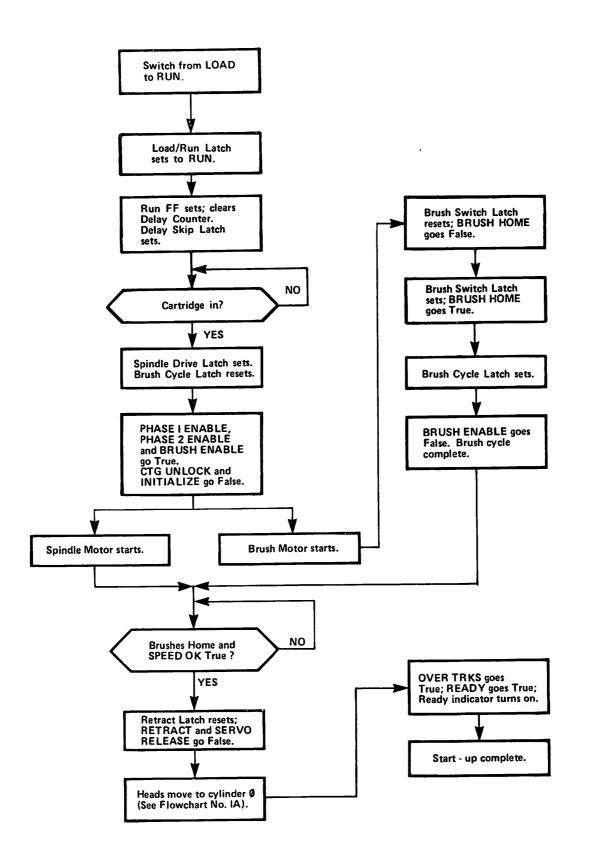

|                   | t-up and Interlock Control                  |              |

|                   | Power-Off Condition                         |              |

|                   |                                             |              |

|                   | Initial Power-On                            |              |

|                   | Start-up Sequence                           | 4-3          |

|                   | dle Drive and Speed Control                 | 4-4          |

|                   | Loading/Unloading                           | 4-4          |

| 4.2.4 Head        | Positioning                                 | 4-6          |

| 4.2.4.1           | Normal Seek                                 | 4-6          |

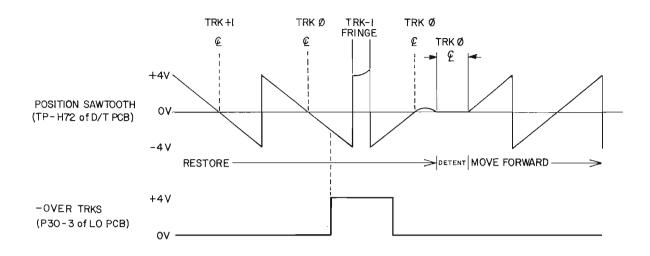

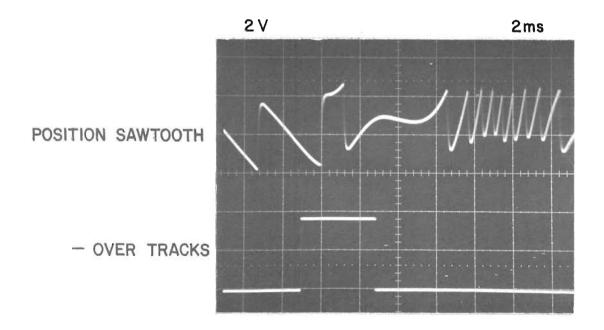

| 4.2.4.2           | Restore                                     | 4-10         |

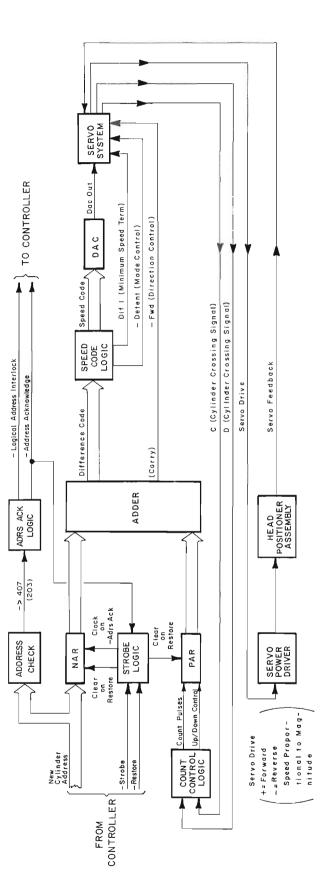

| 4.2.5 Serve       | o System                                    | 4-11         |

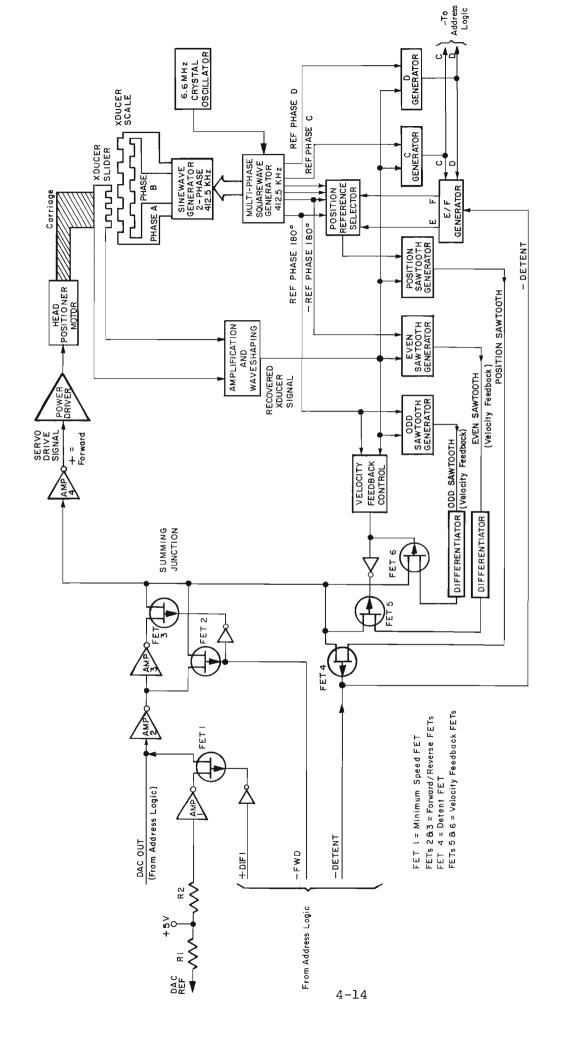

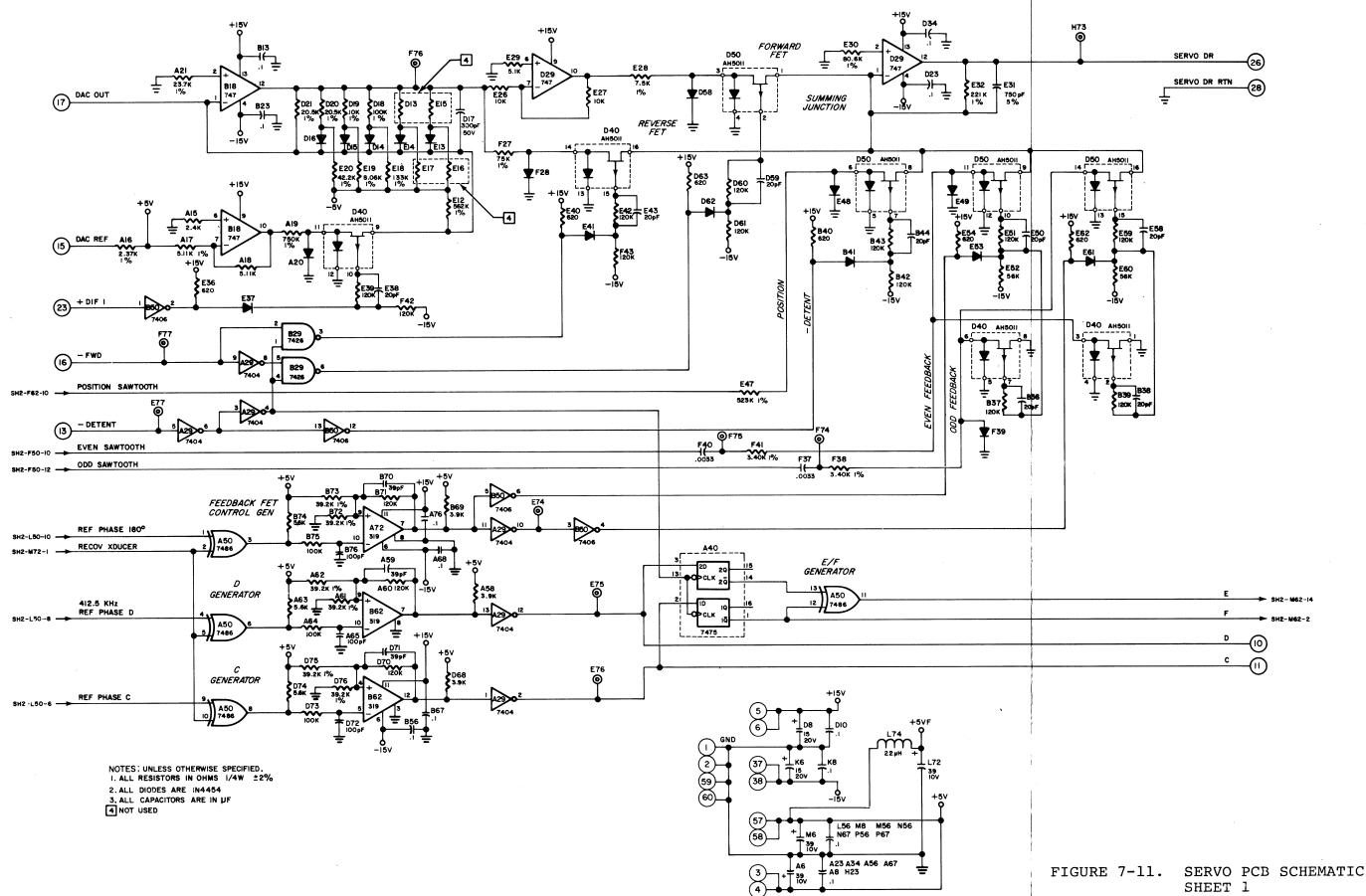

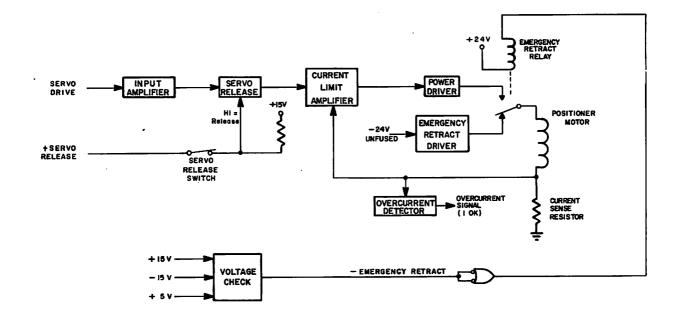

| 4.2.5.1           | Expanded Servo Diagram                      | 4-11         |

| 4.2.5.2           | Temperature Compensation                    | 4-20         |

| 4.2.6 Inde        | x/Sector Information Control                | 4-20         |

|                   | Transfer Functions                          |              |

| 4.2.7.1           |                                             |              |

| 4.2.7.2           |                                             |              |

| 4.2.7.3           |                                             |              |

| 4.2.7.4           |                                             |              |

| 4.2.7.5           |                                             |              |

|                   | Read Channel                                |              |

|                   |                                             | 4-25         |

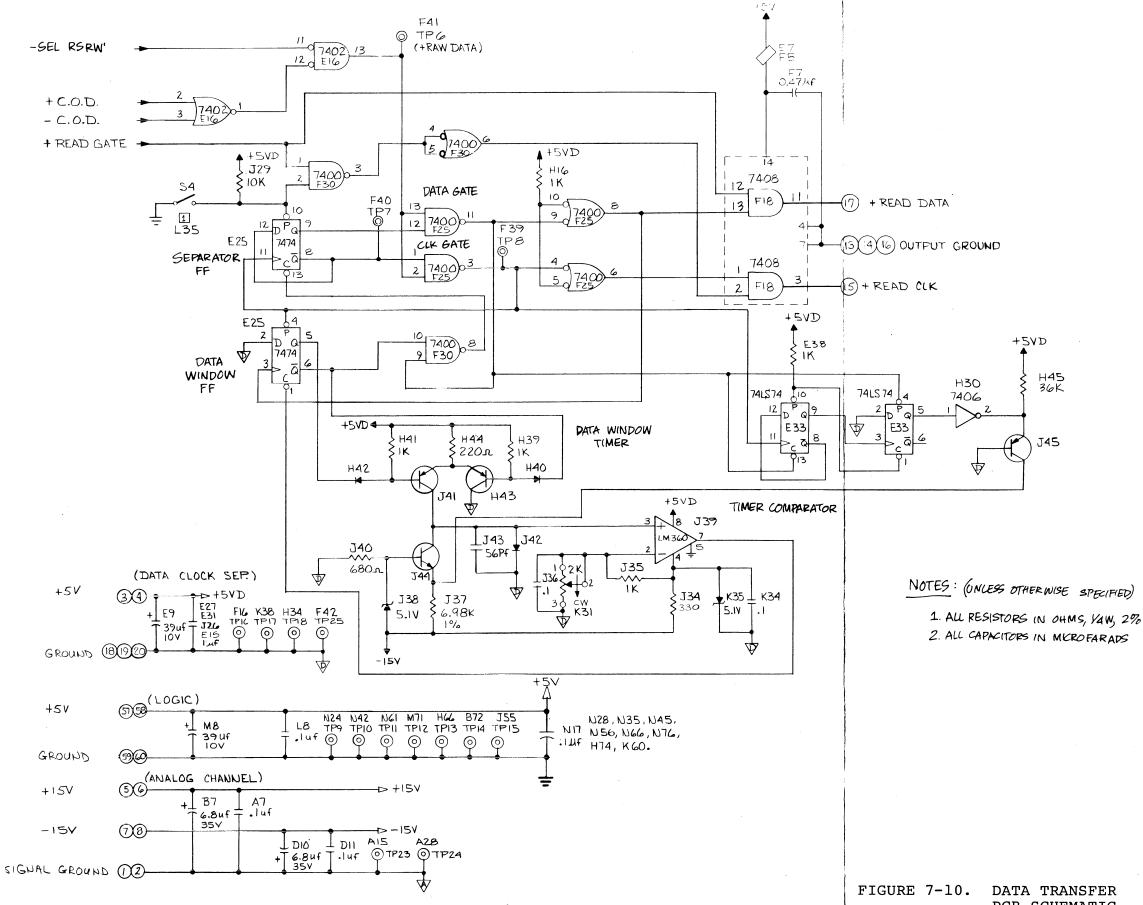

|                   | Data/Clock Separation                       |              |

|                   | .7.1 Single-Shot Separator                  |              |

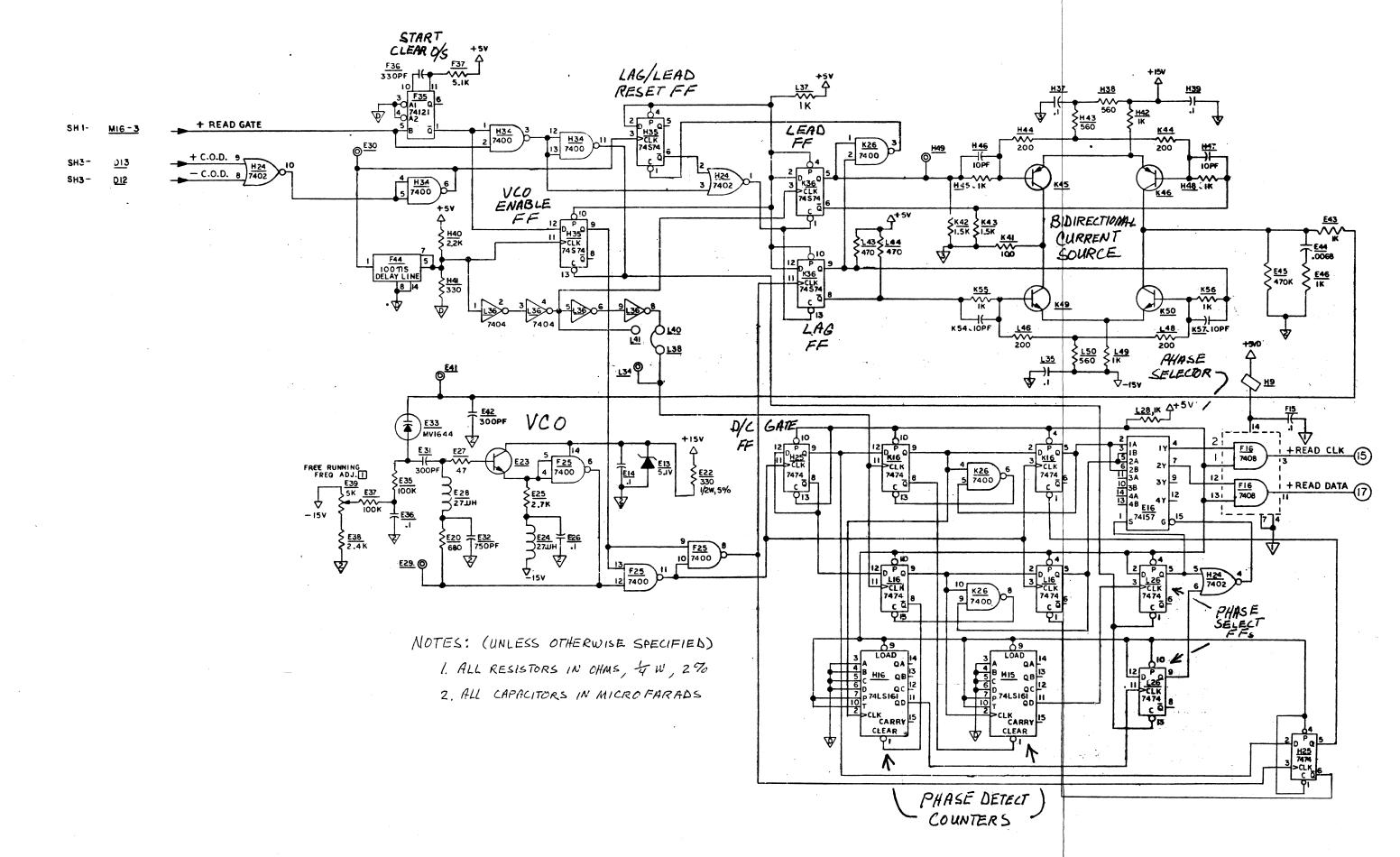

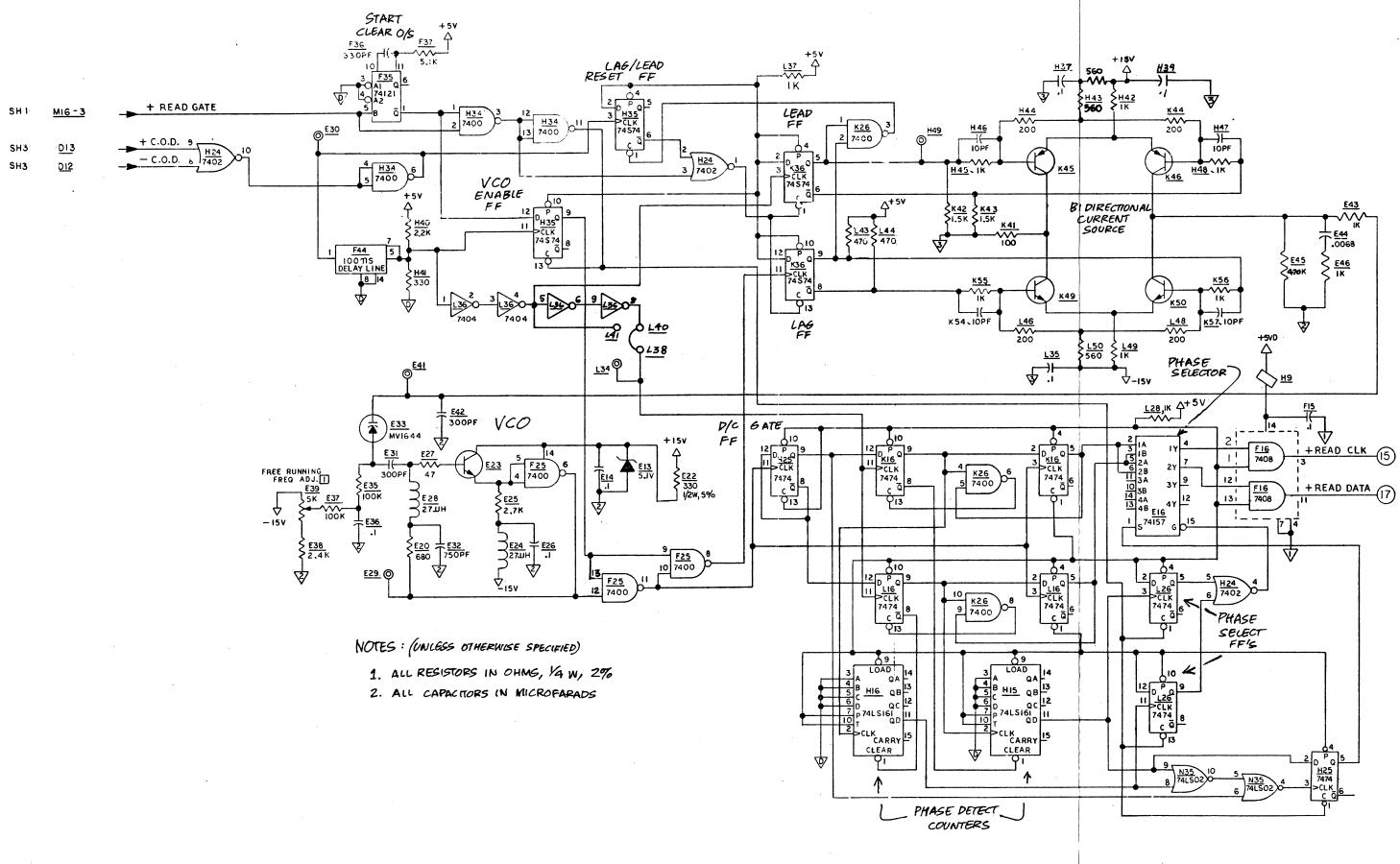

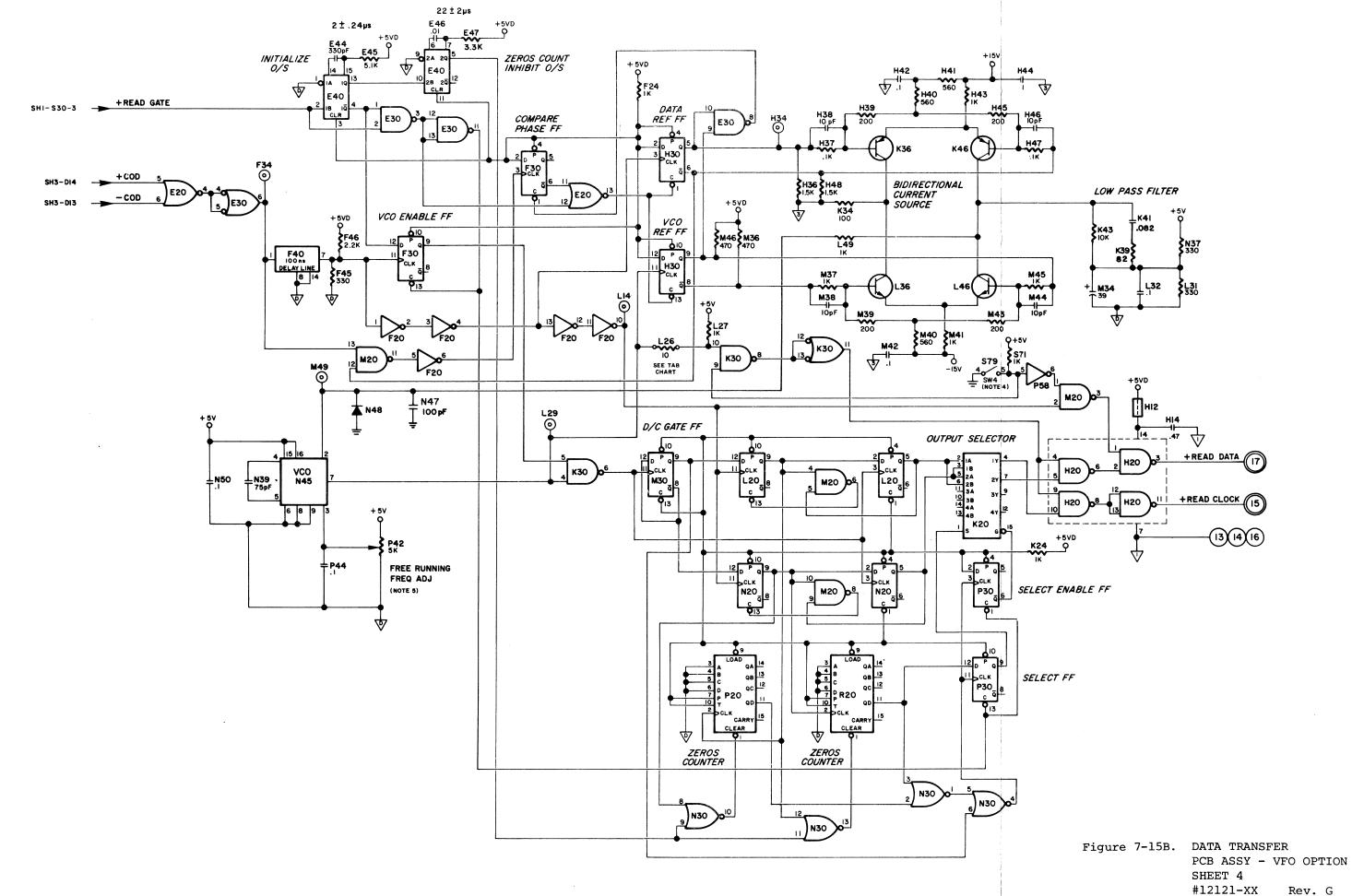

|                   | .7.2 VFO Separator Option                   |              |

| 4.2.7.8           |                                             | 4-26         |

| 4.3 Circuit De    | escriptions                                 | 4-27         |

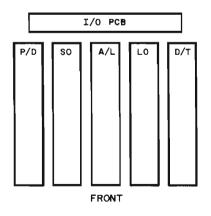

|                   | t/Output (I/O) PCB (#12025)                 |              |

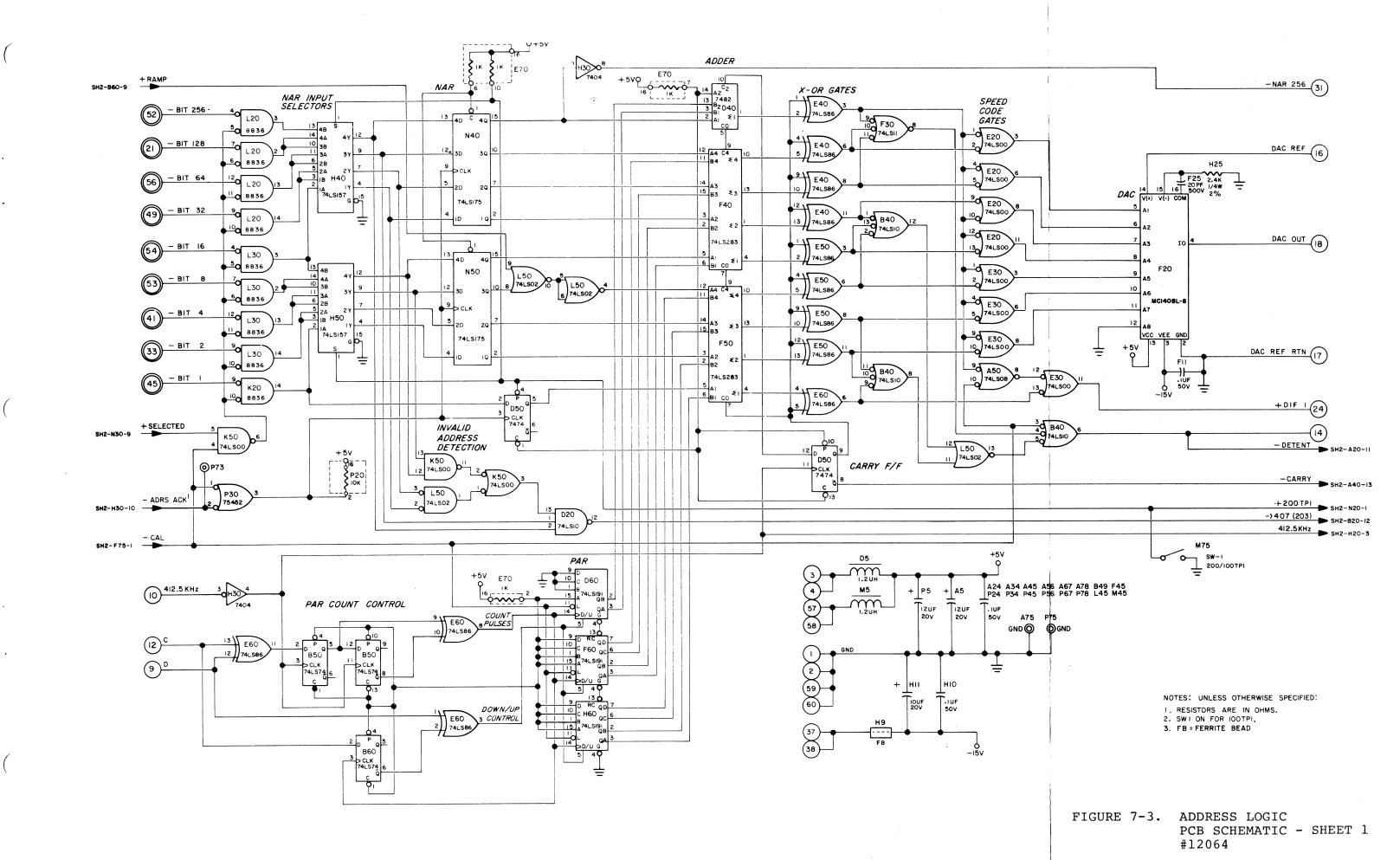

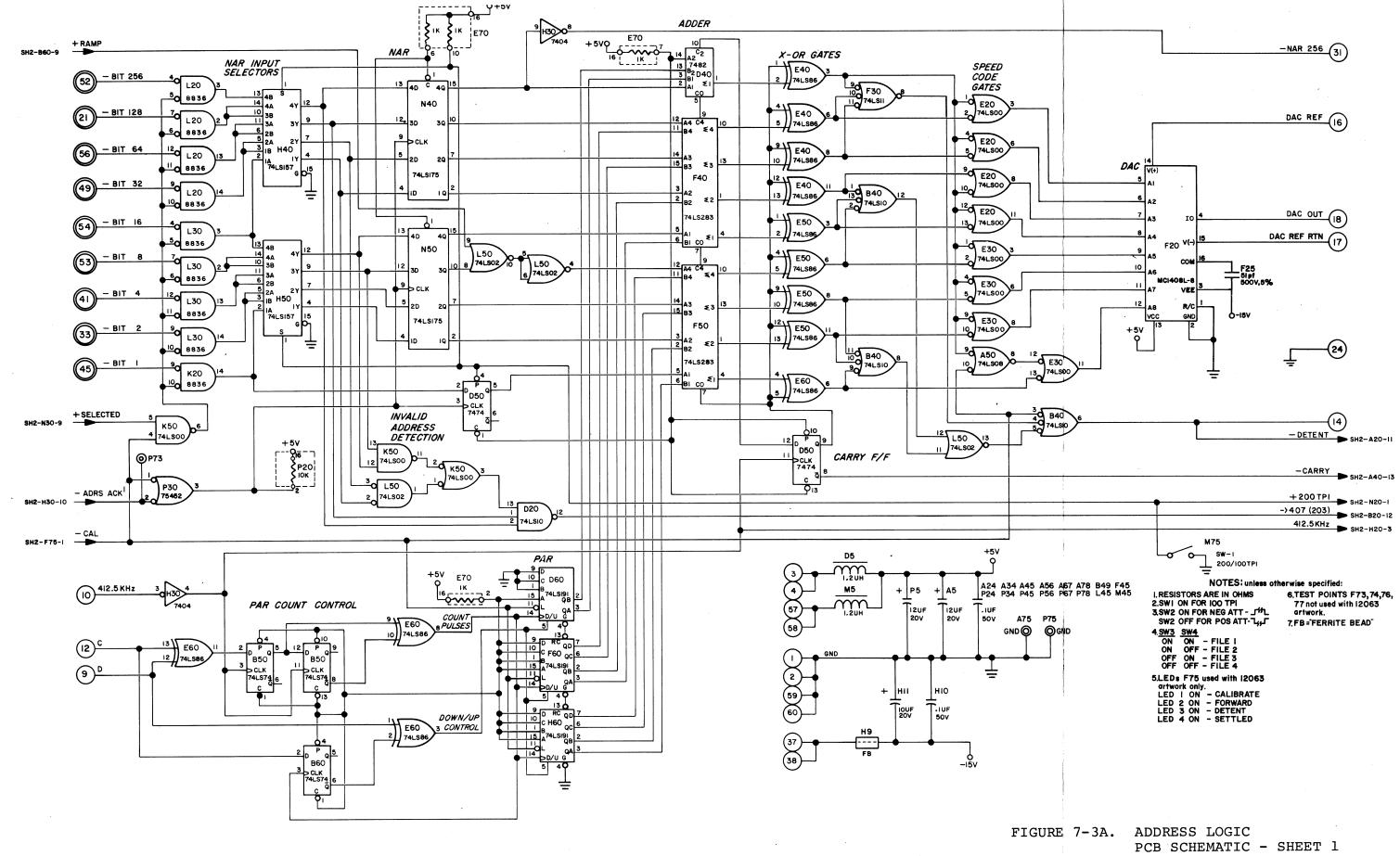

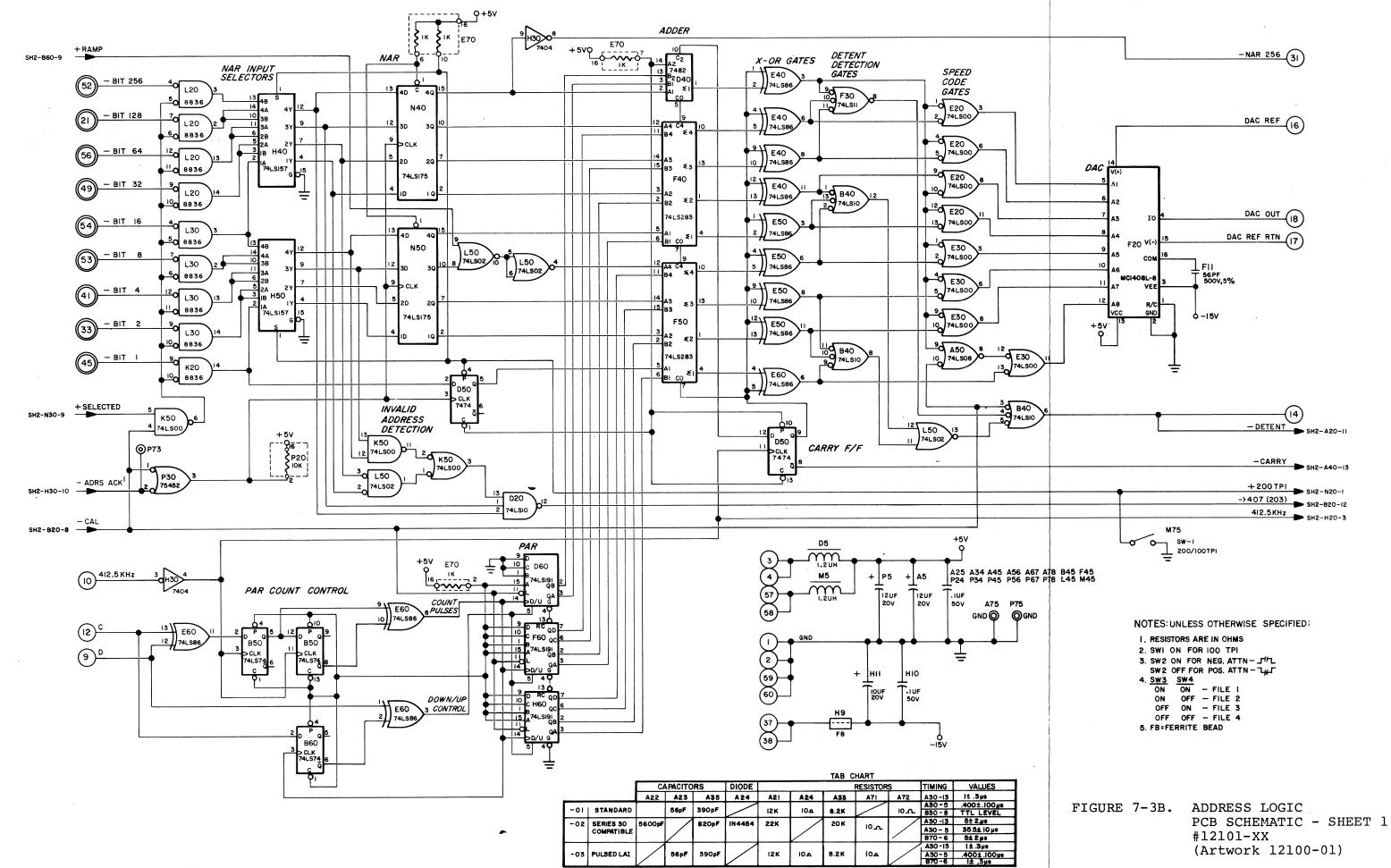

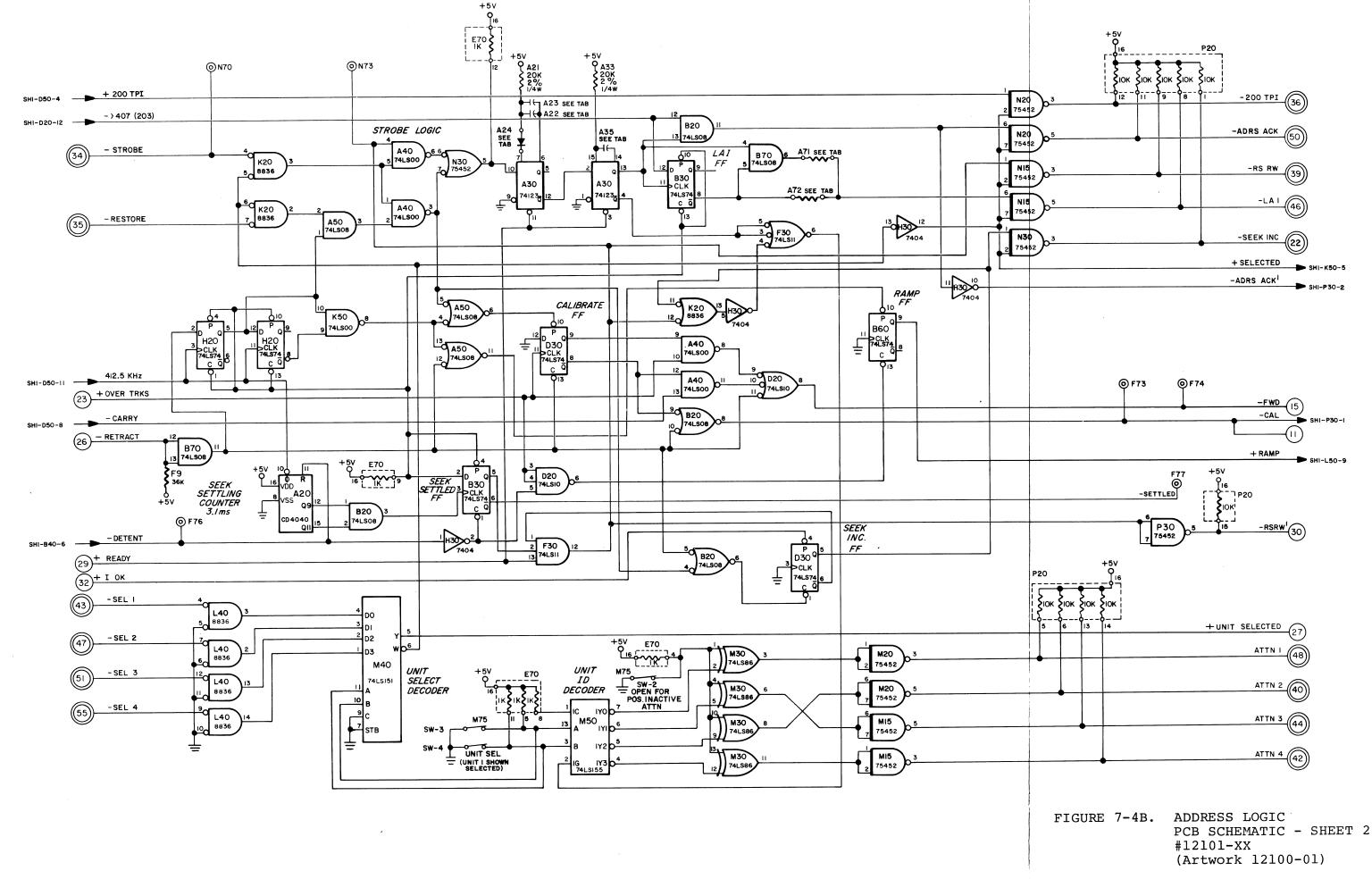

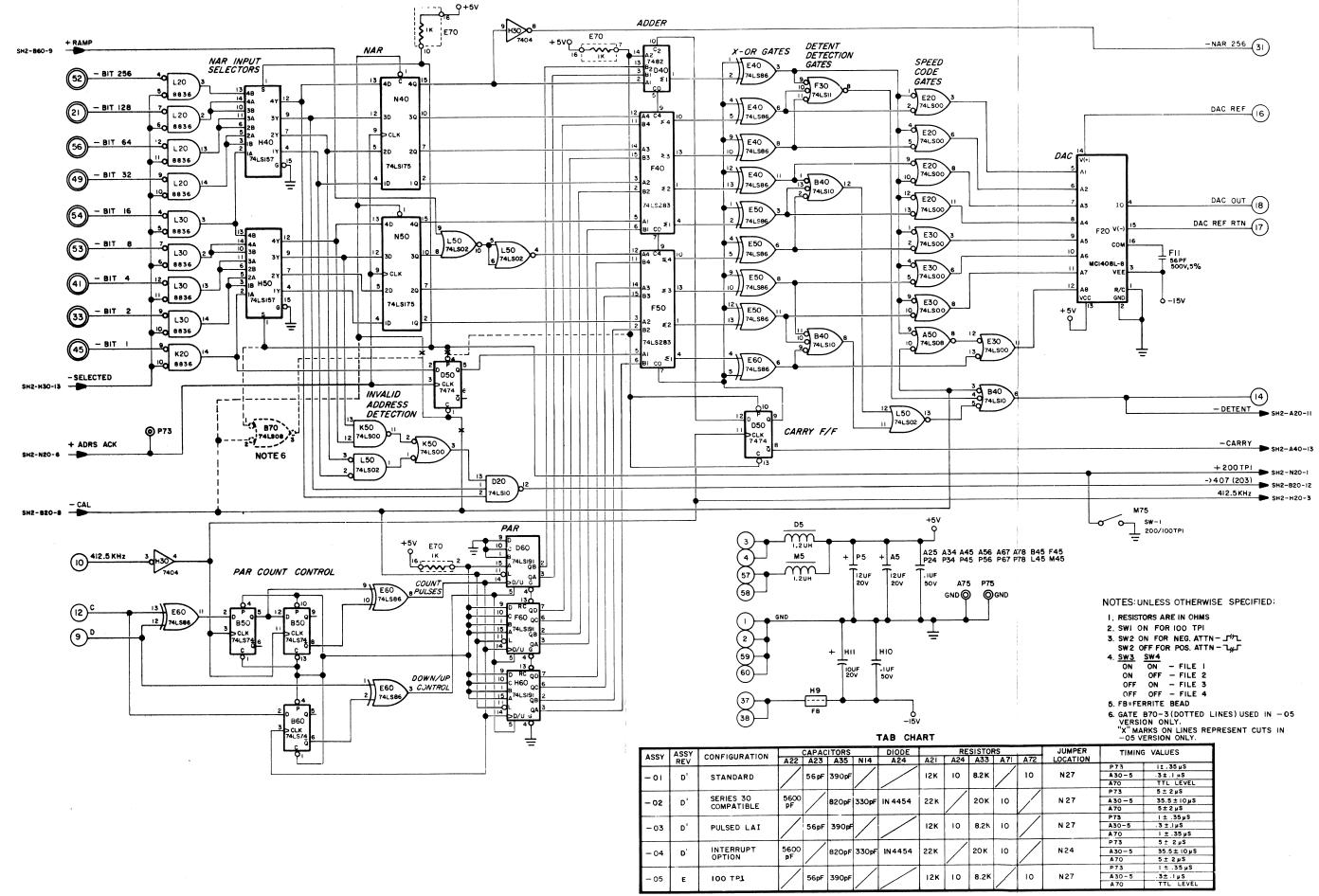

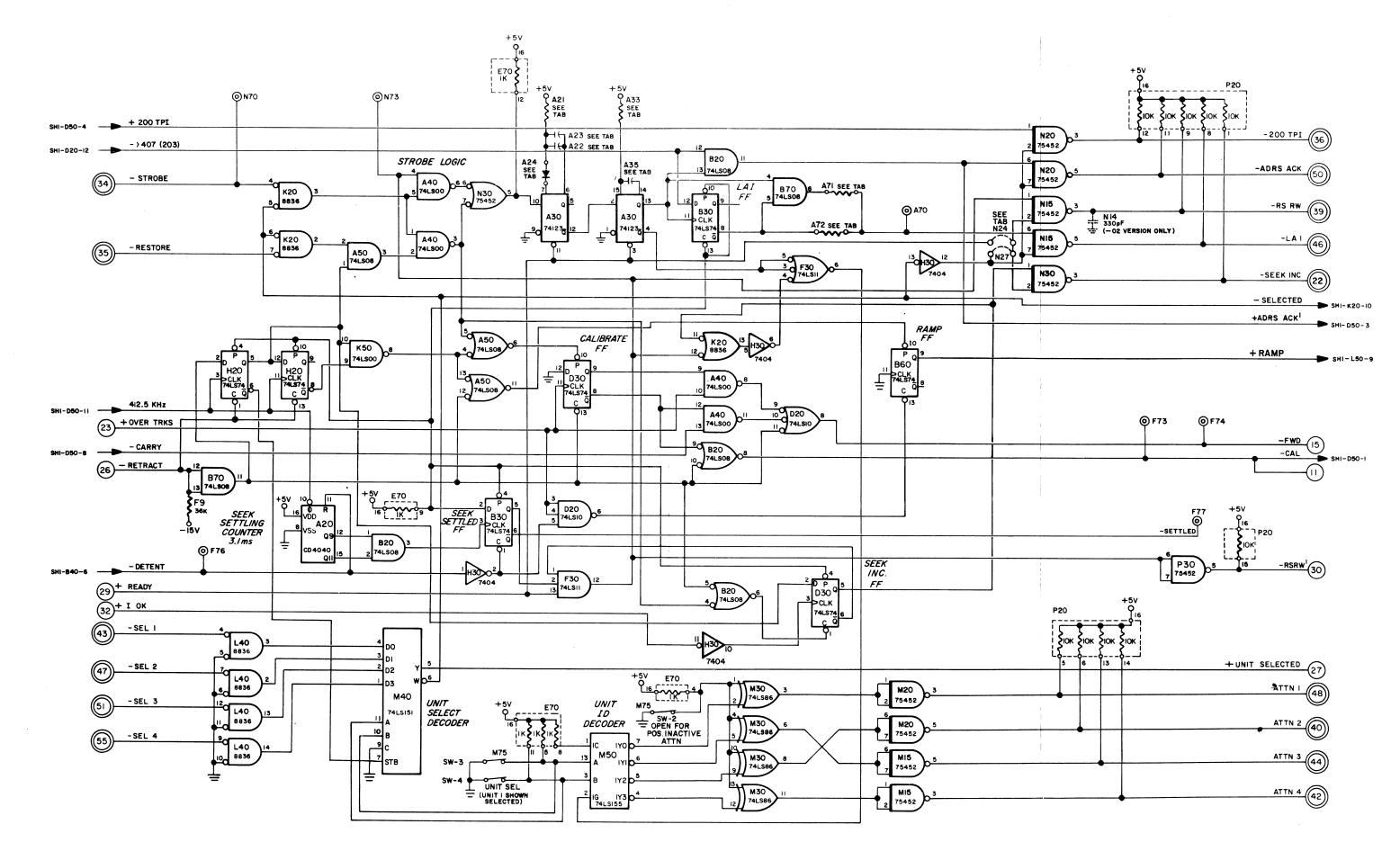

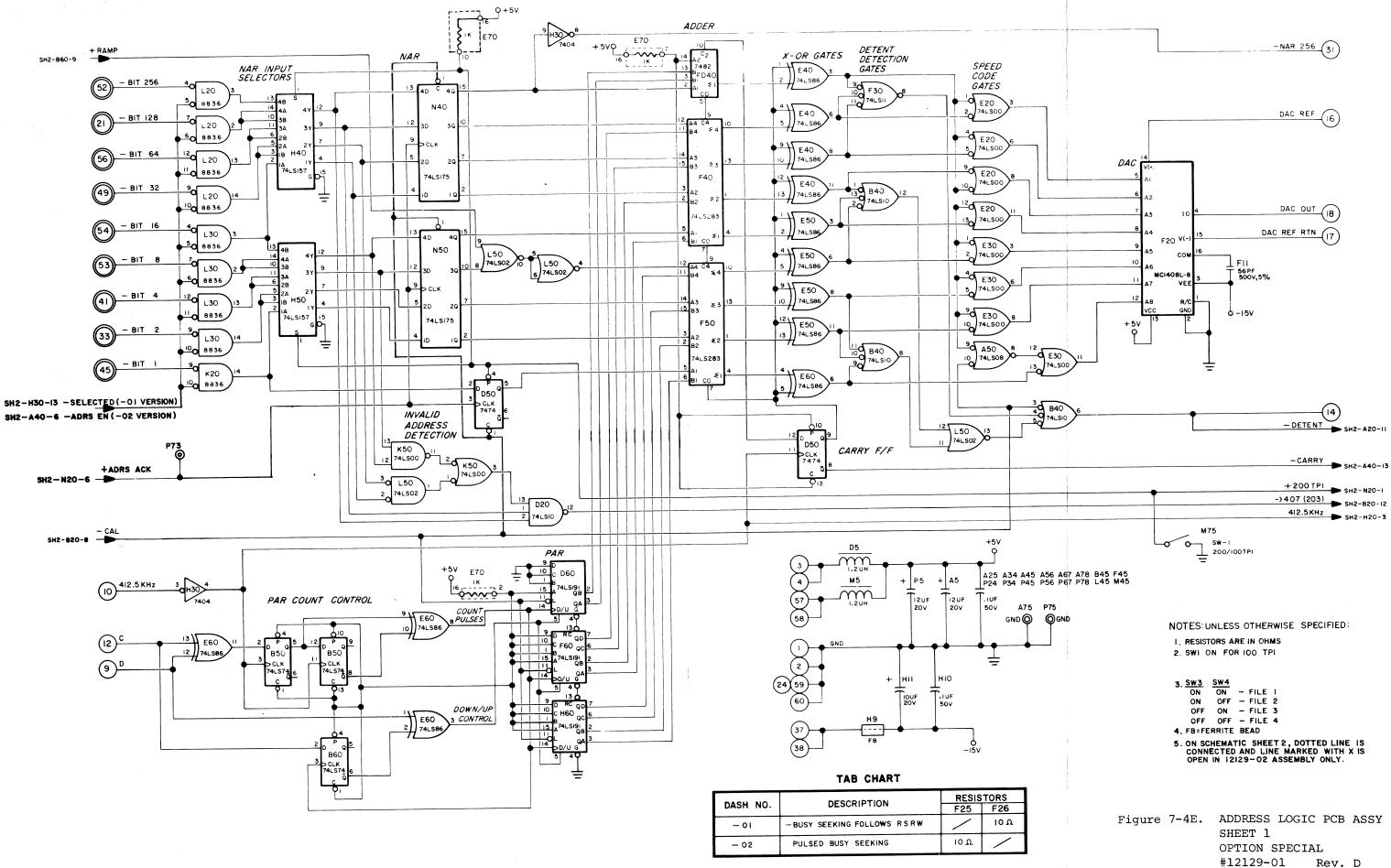

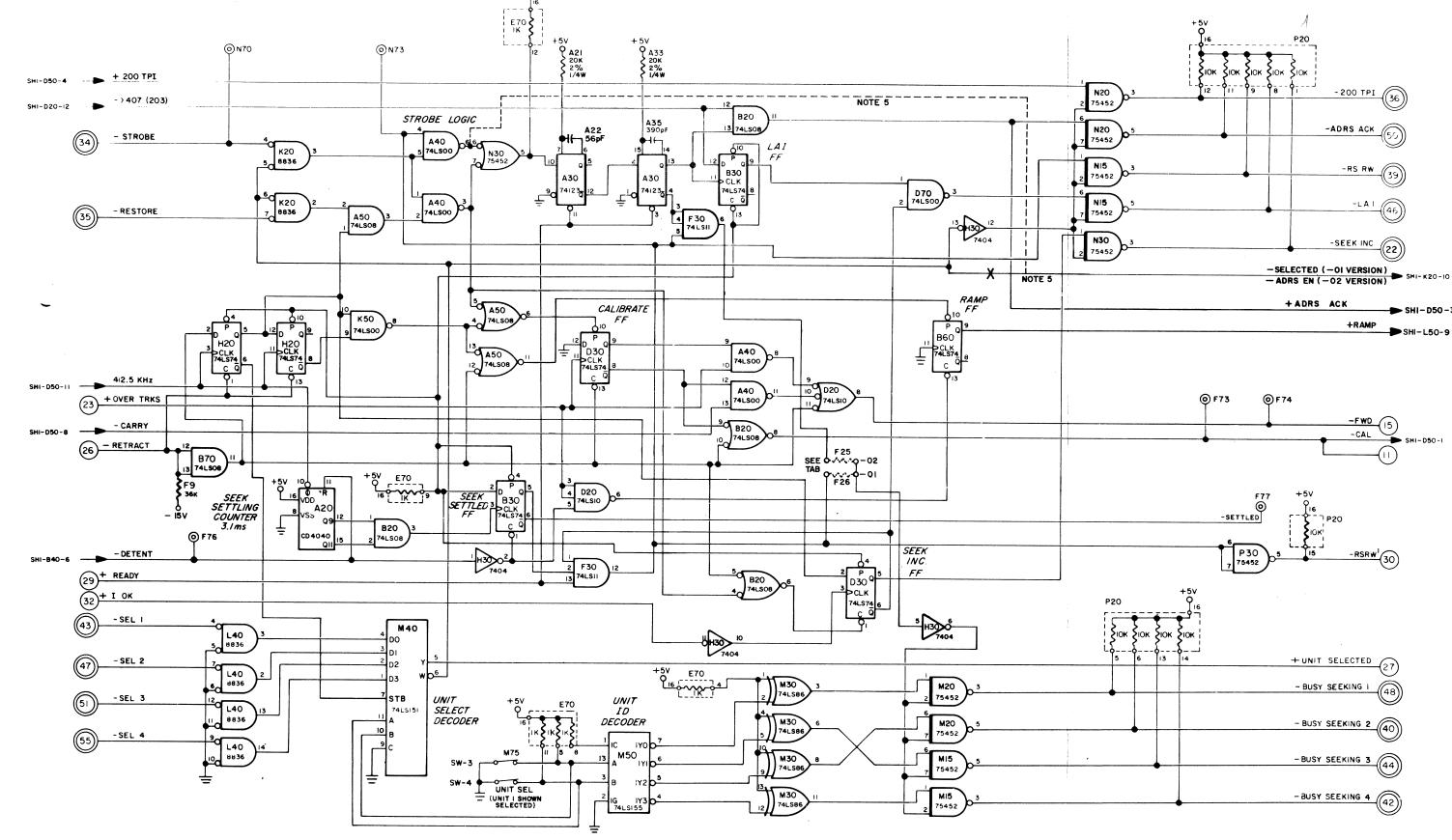

| 4.3.2 Addr        | ess Logic (A/L) PCB (#12064)                |              |

| 4.3.2.1           |                                             | 4-27         |

| 4.3.2.2           |                                             |              |

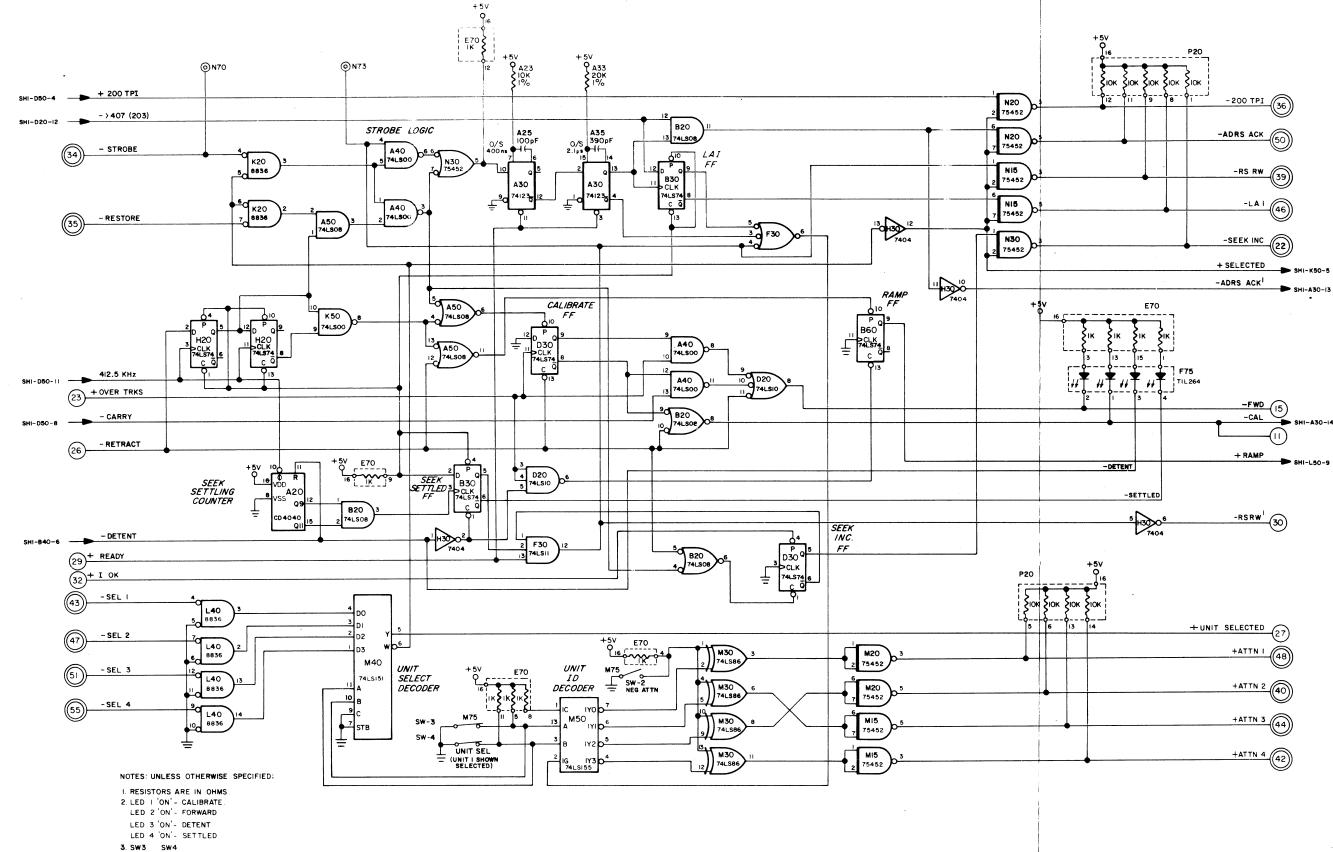

|                   | Control Logic                               | 4-28         |

| 4.3.2.3           | Servo Speed Control Logic                   | 4-29         |

| 4.3.2.4           |                                             |              |

| 4.3.2.5           | Direction Control, Calibrate and RAMP Logic | 4-32         |

| 4.3.2.6           | Seek Settling Logic                         | 4-36         |

| 4.3.2.7           | Seek Incomplete                             | 4-36         |

| 4.3.2.8           | Unit Select and Attention                   | 4-37         |

|                   | o (SO) PCB (#12068)                         | 4-37         |

| 4.3.3.1           | Speed Command Inputs                        | 4-37         |

| 4.3.3.2           | Direction Control                           | 4-38         |

|                   |                                             | 4-38         |

| 4.3.3.3           | SERVO DRIVE Signal                          | 4-38<br>4-38 |

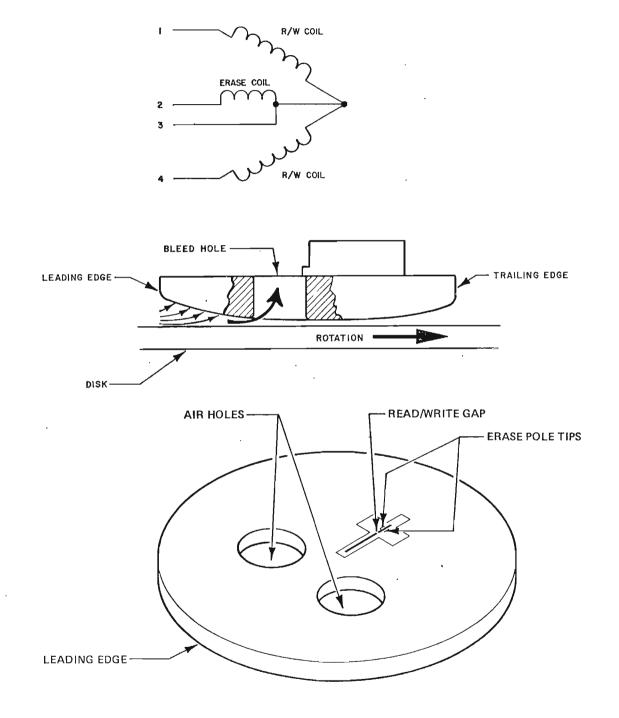

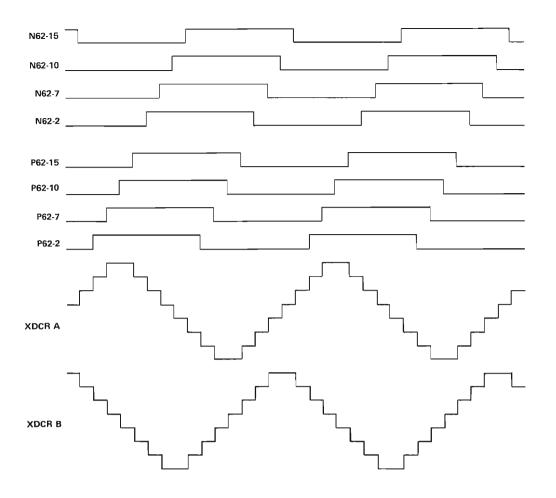

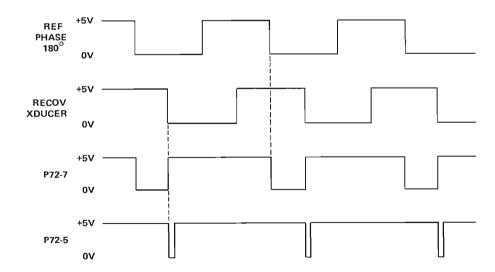

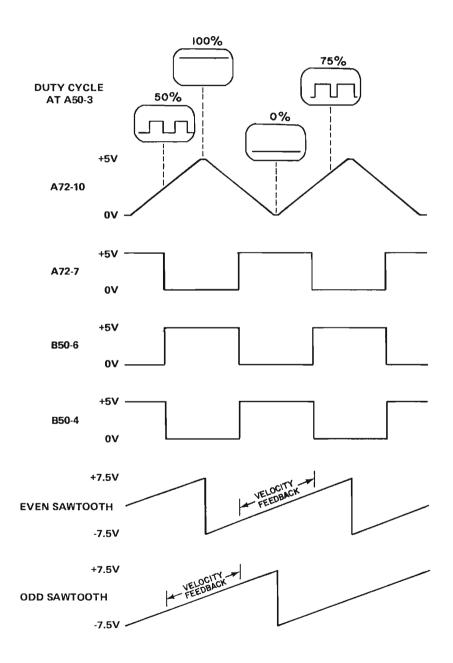

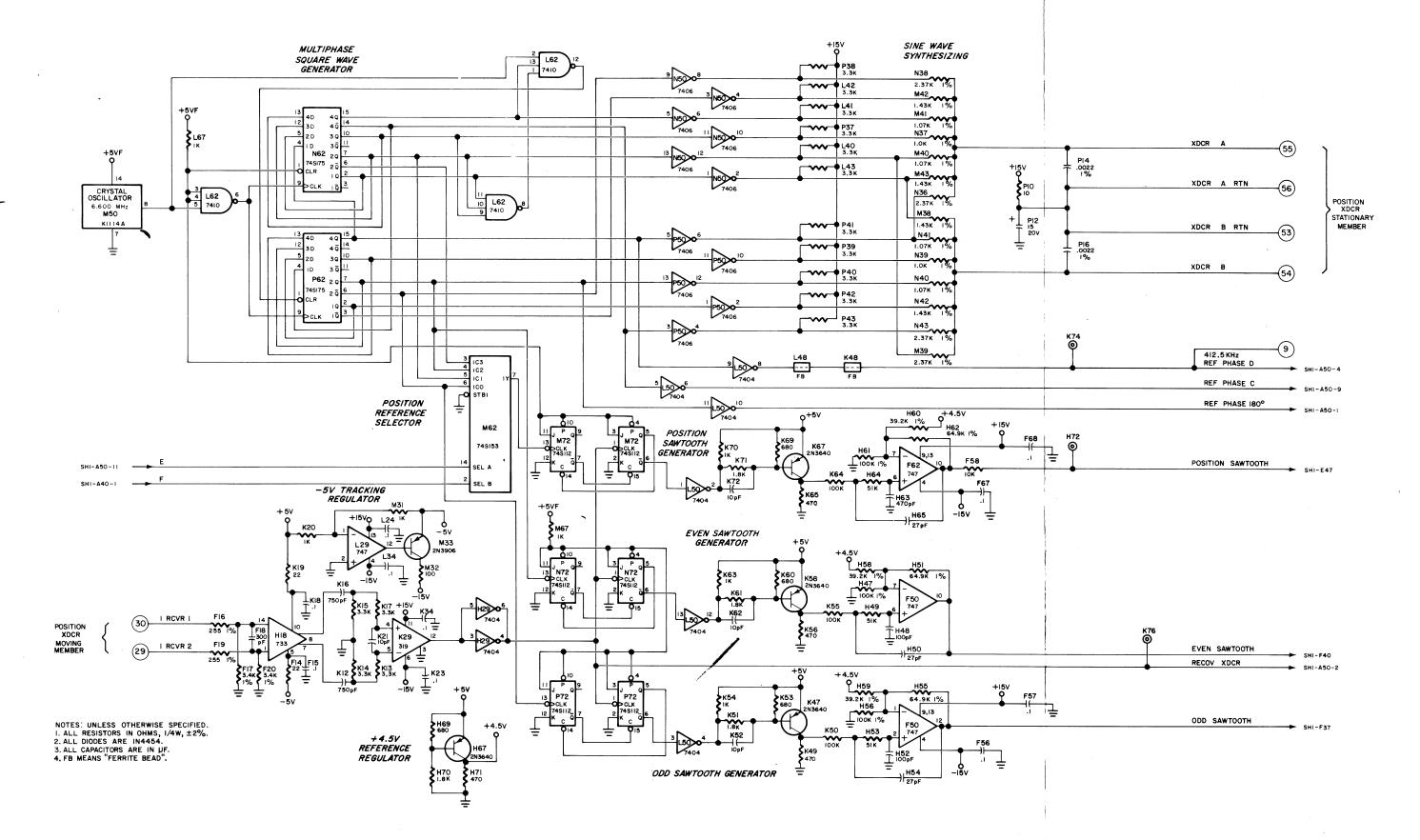

| 4.3.3.4           | Multi-Phase Squarewave Generator            | 4-38<br>4-41 |

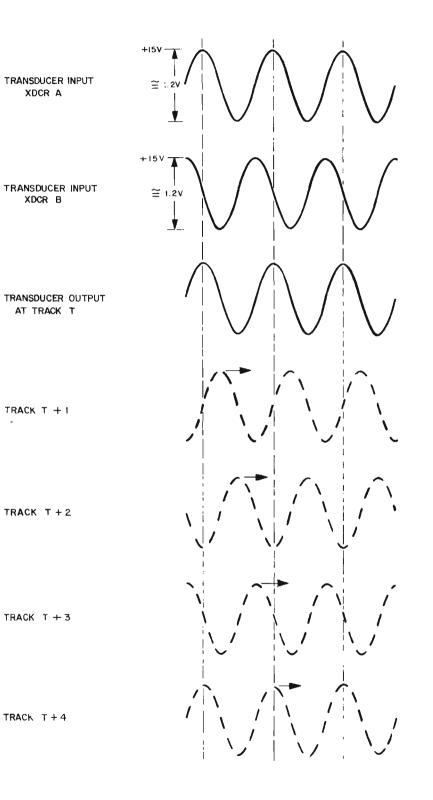

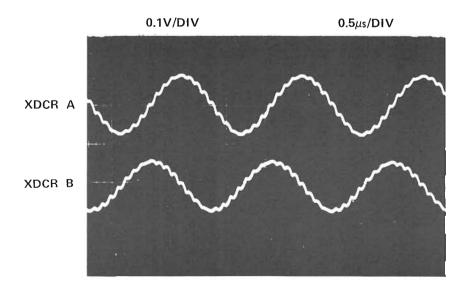

| 4.3.3.5           | Position Transducer Inputs                  | 4-4⊥<br>4-41 |

| 4.3.3.6           | Position Transducer Output                  | 4-41<br>4-41 |

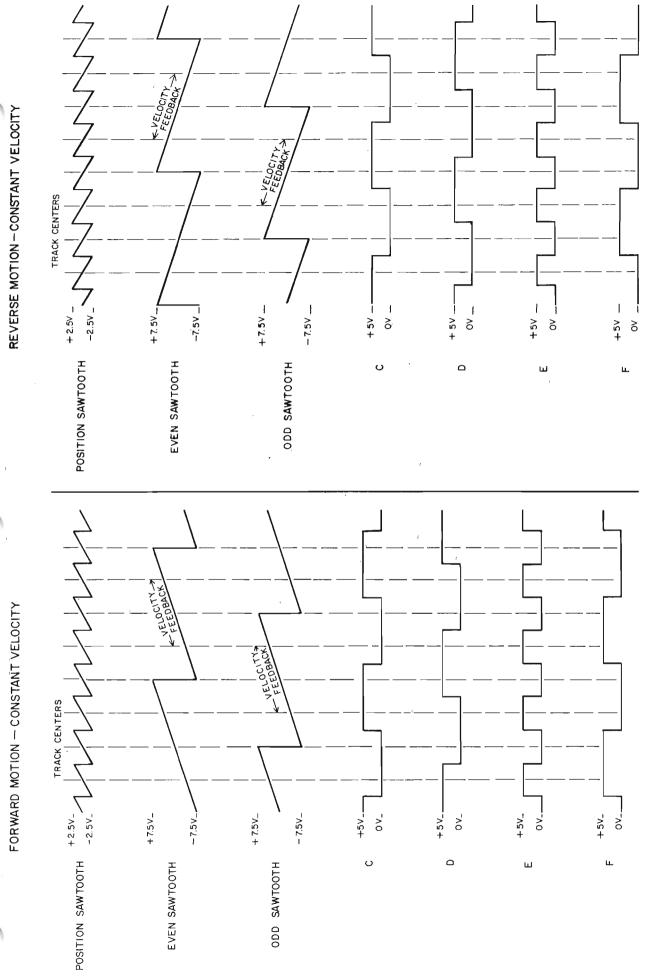

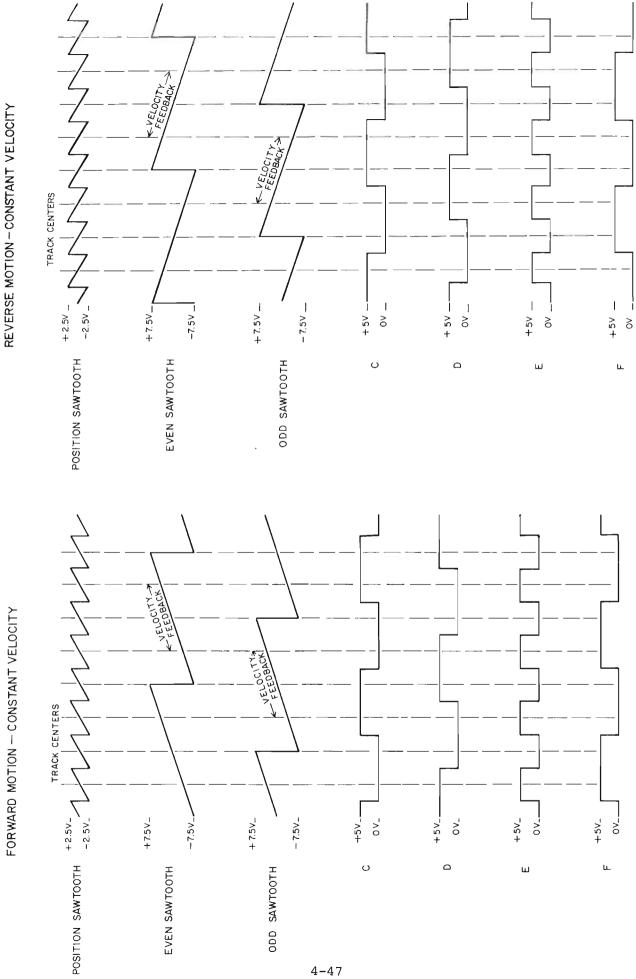

| 4.3.3.7           | Odd and Even Sawtooth Generators            |              |

| 4.3.3.8           | Velocity Feedback                           | 4-45         |

| 4.3.3.9           | C and D                                     | 4-45         |

|                   | E and $F$                                   | 4-45         |

|                   | Position Sawtooth Generator                 | 4-48         |

|                   | Detent Mode                                 | 4-48         |

| 4.3.3.13          | +4.5V                                       | 4-48         |

| 4.3.3.14          | -5V                                         | 4 - 48       |

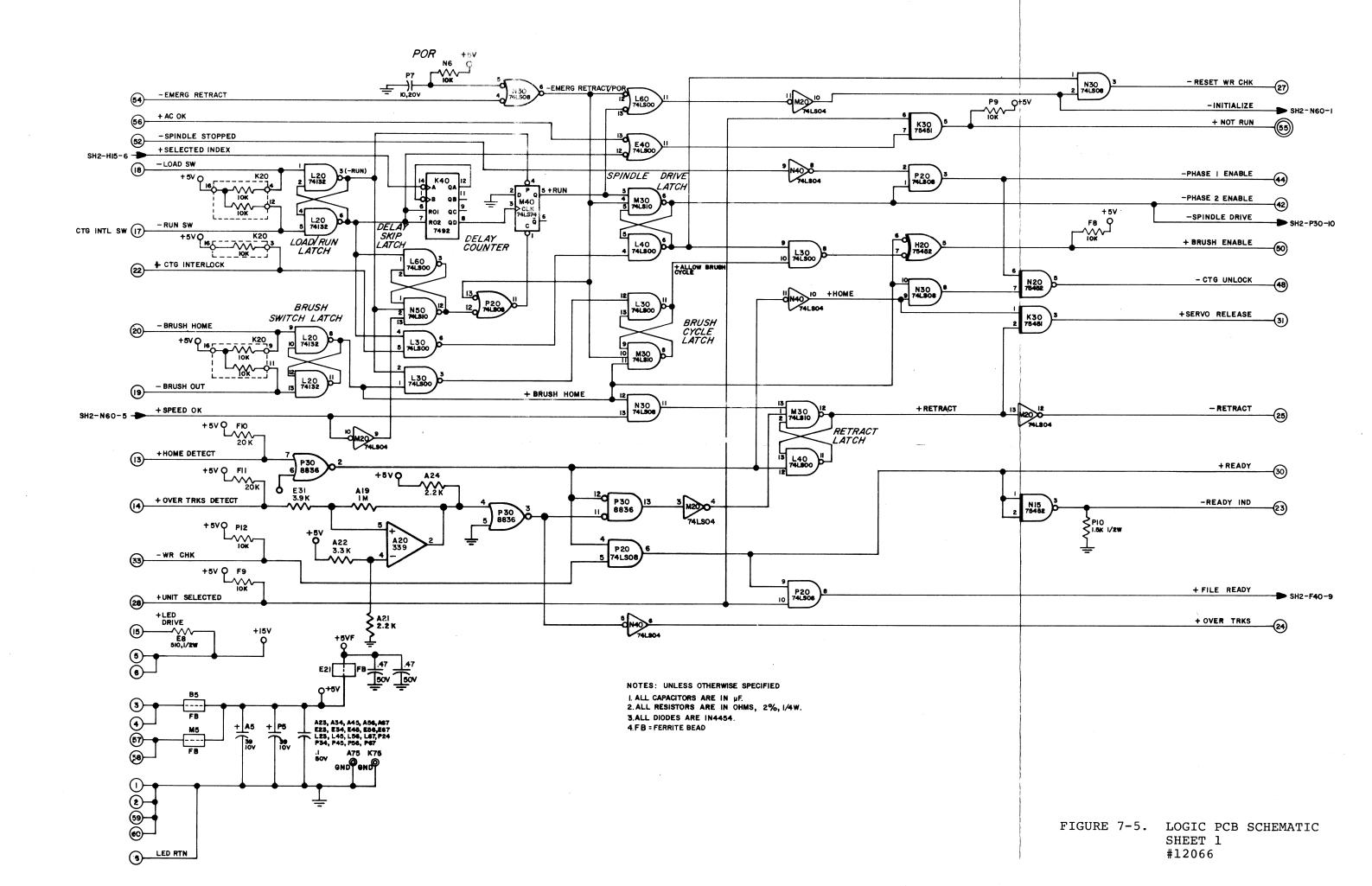

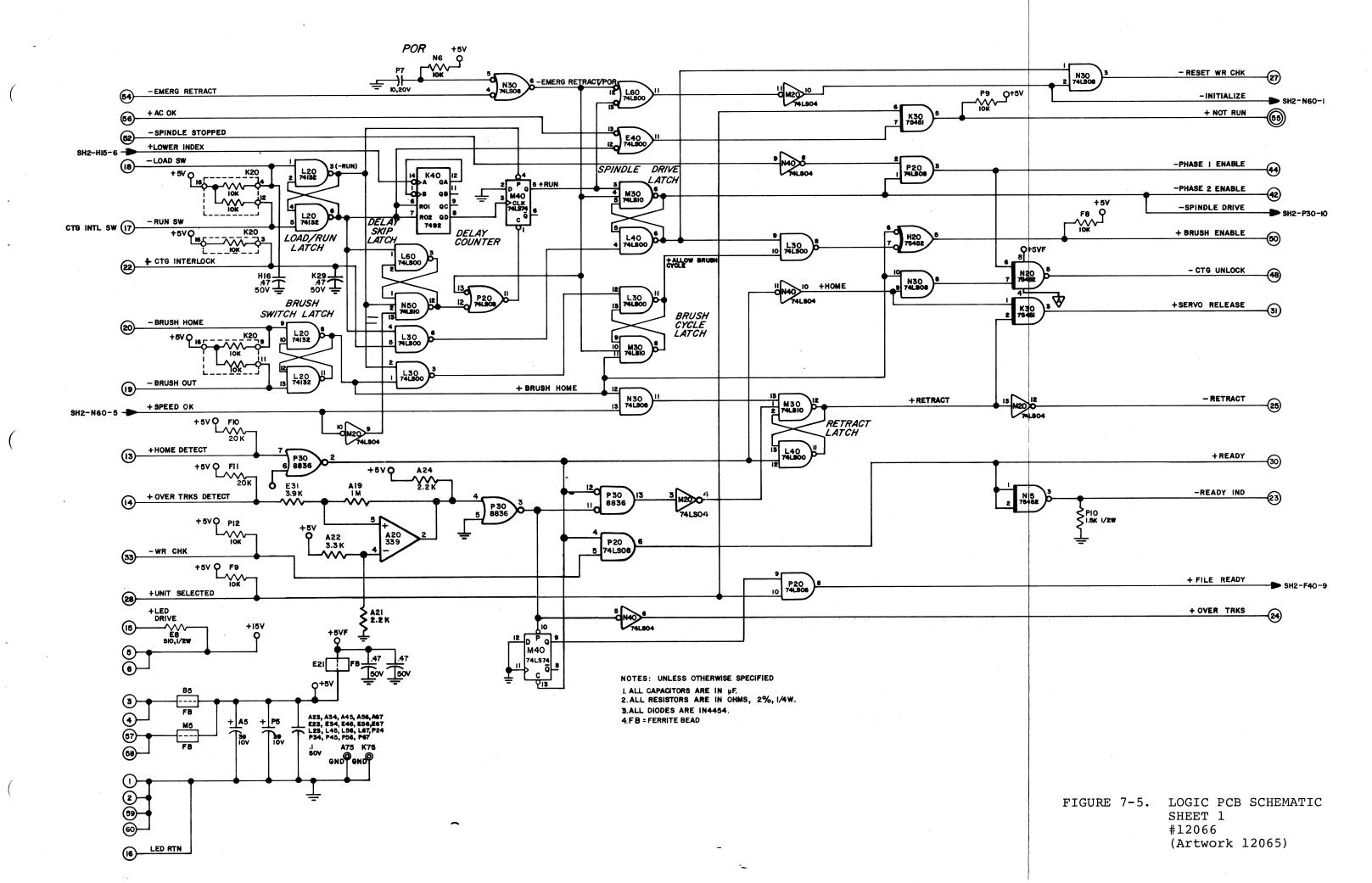

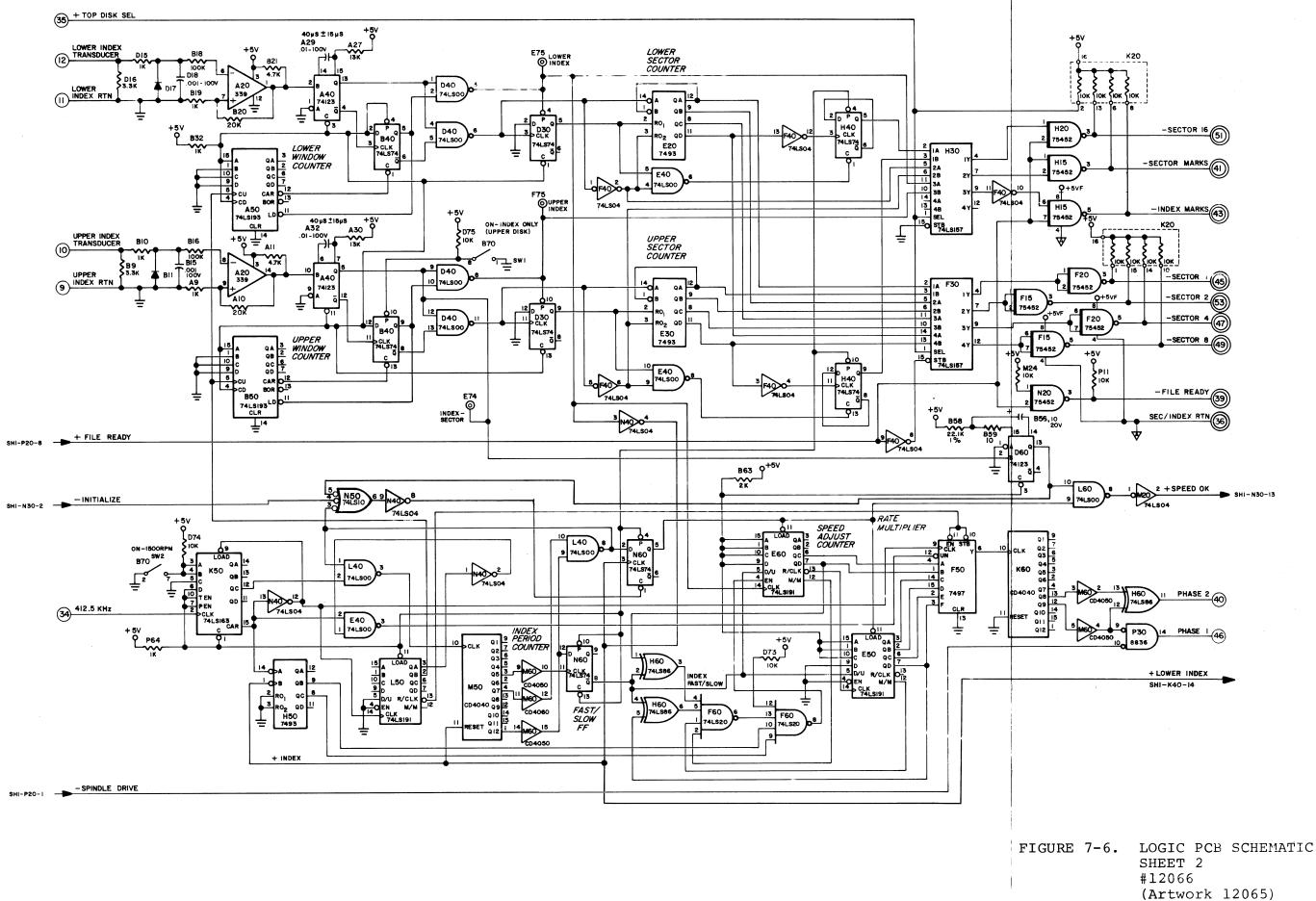

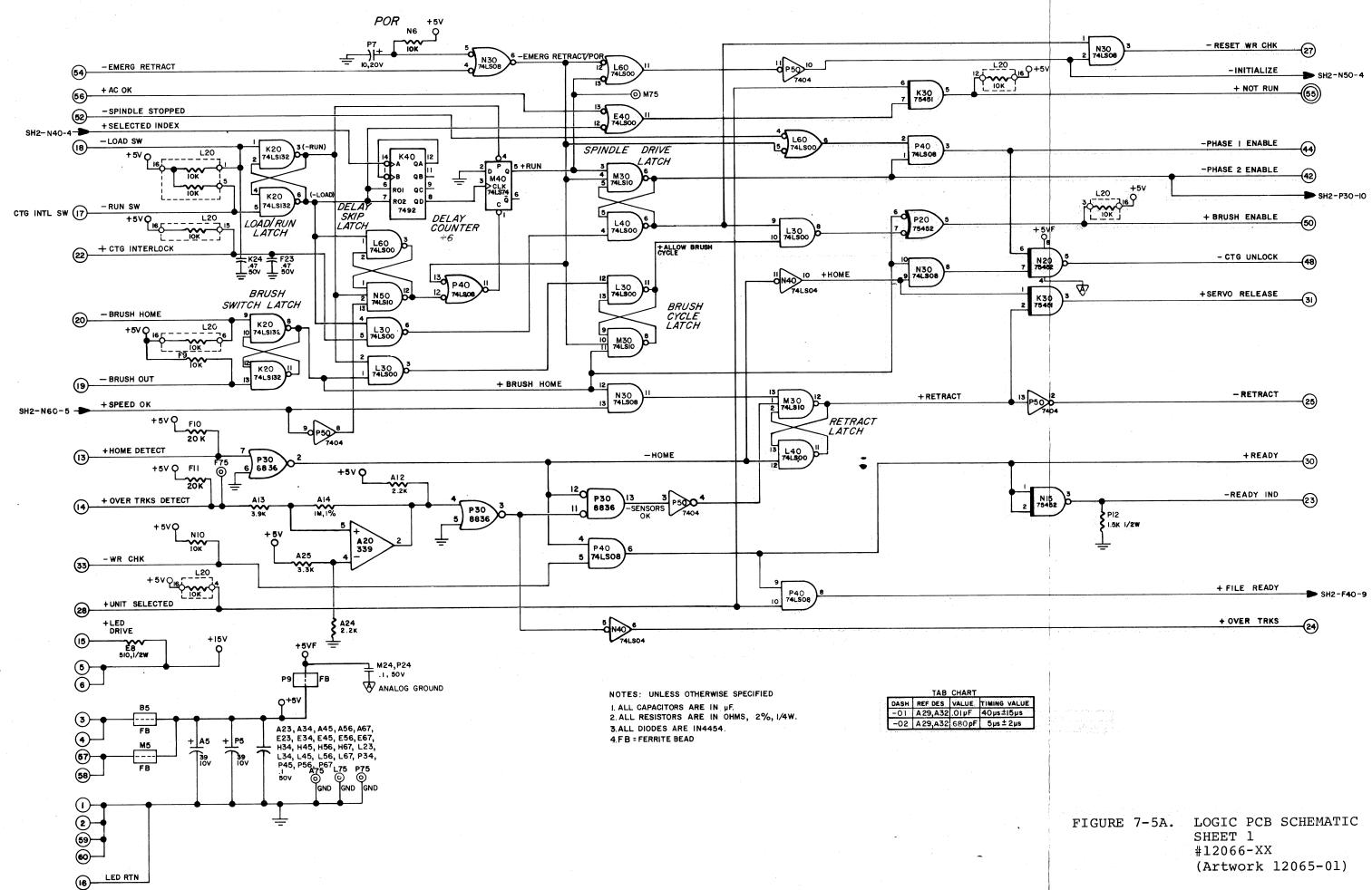

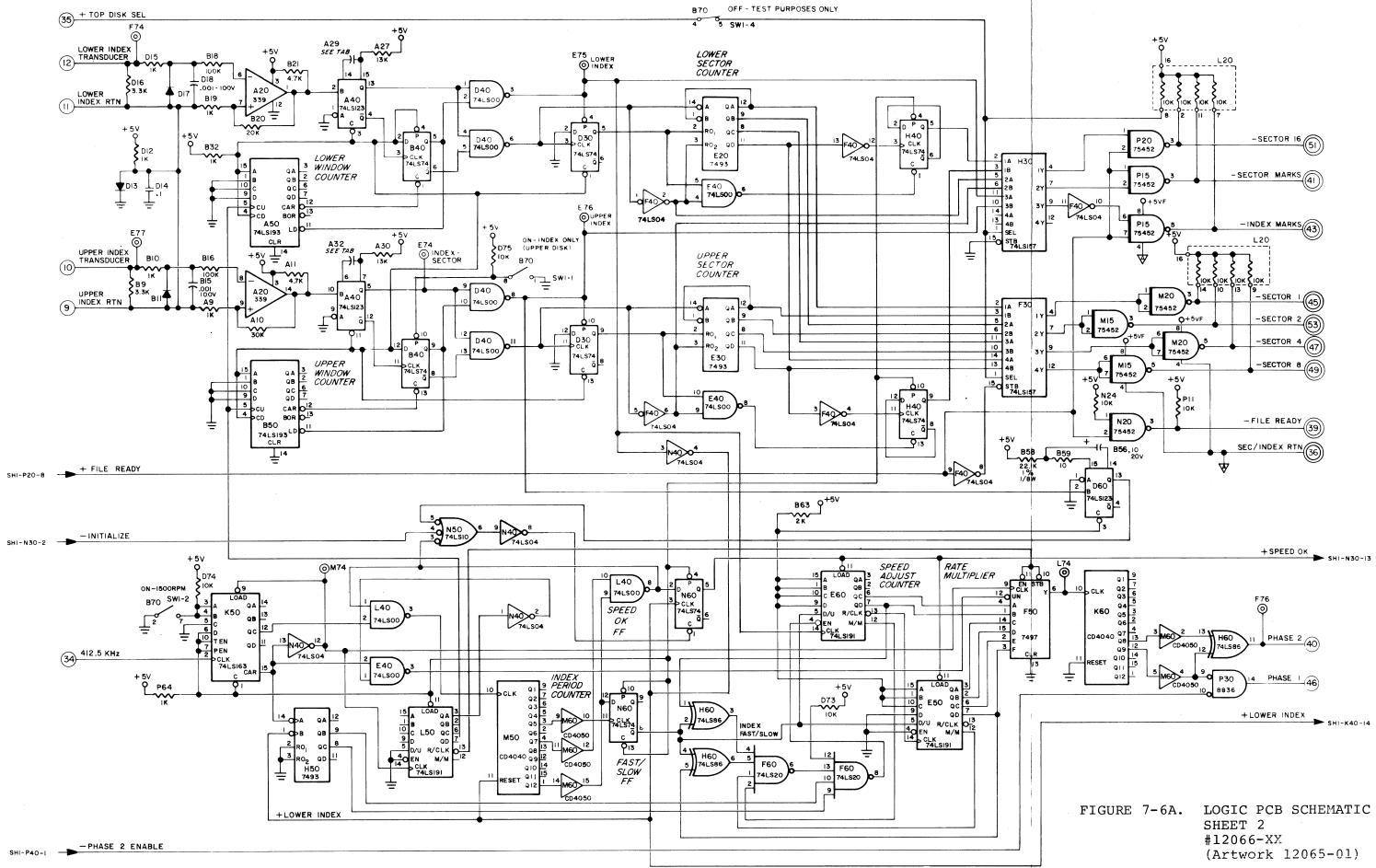

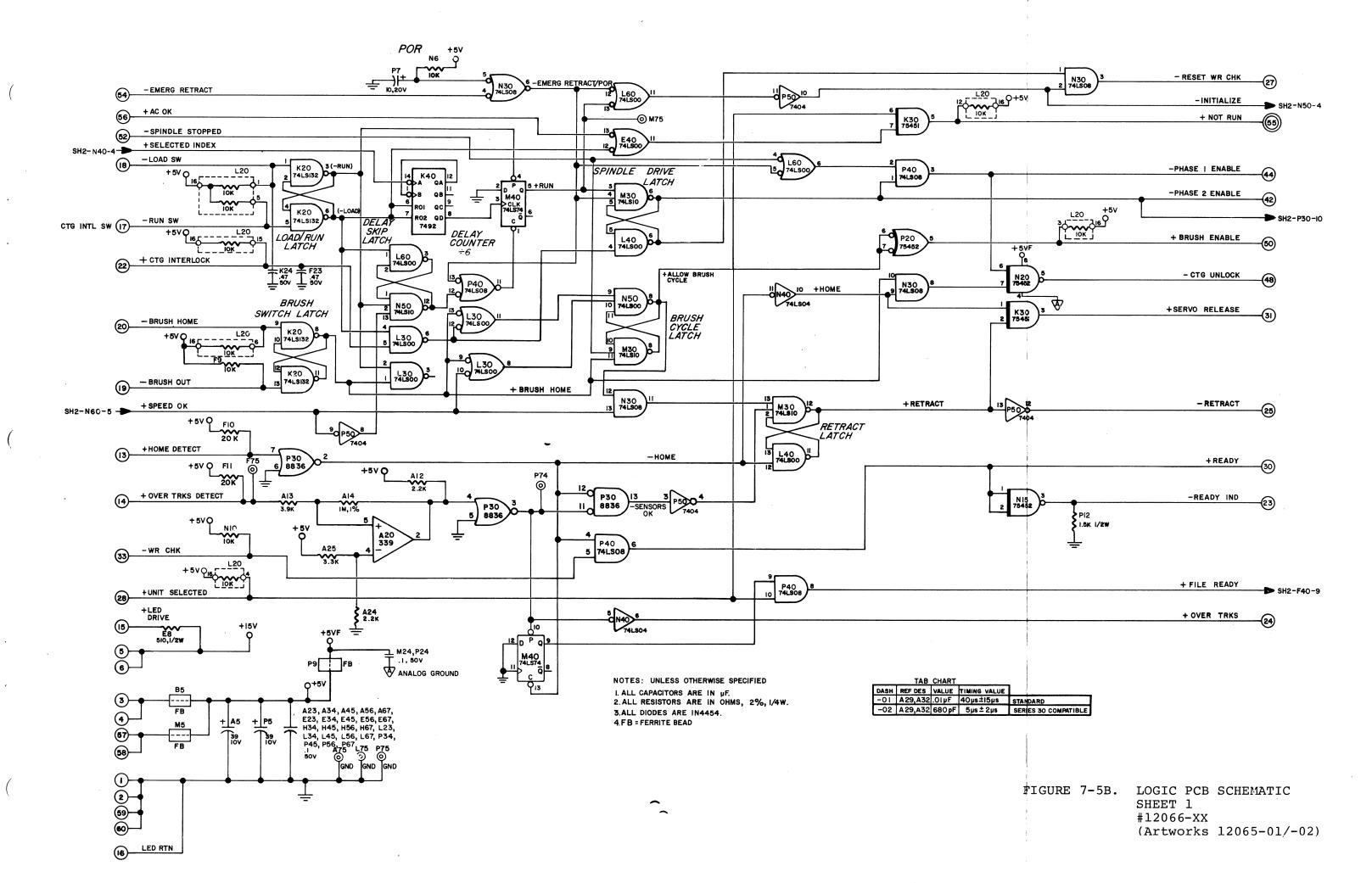

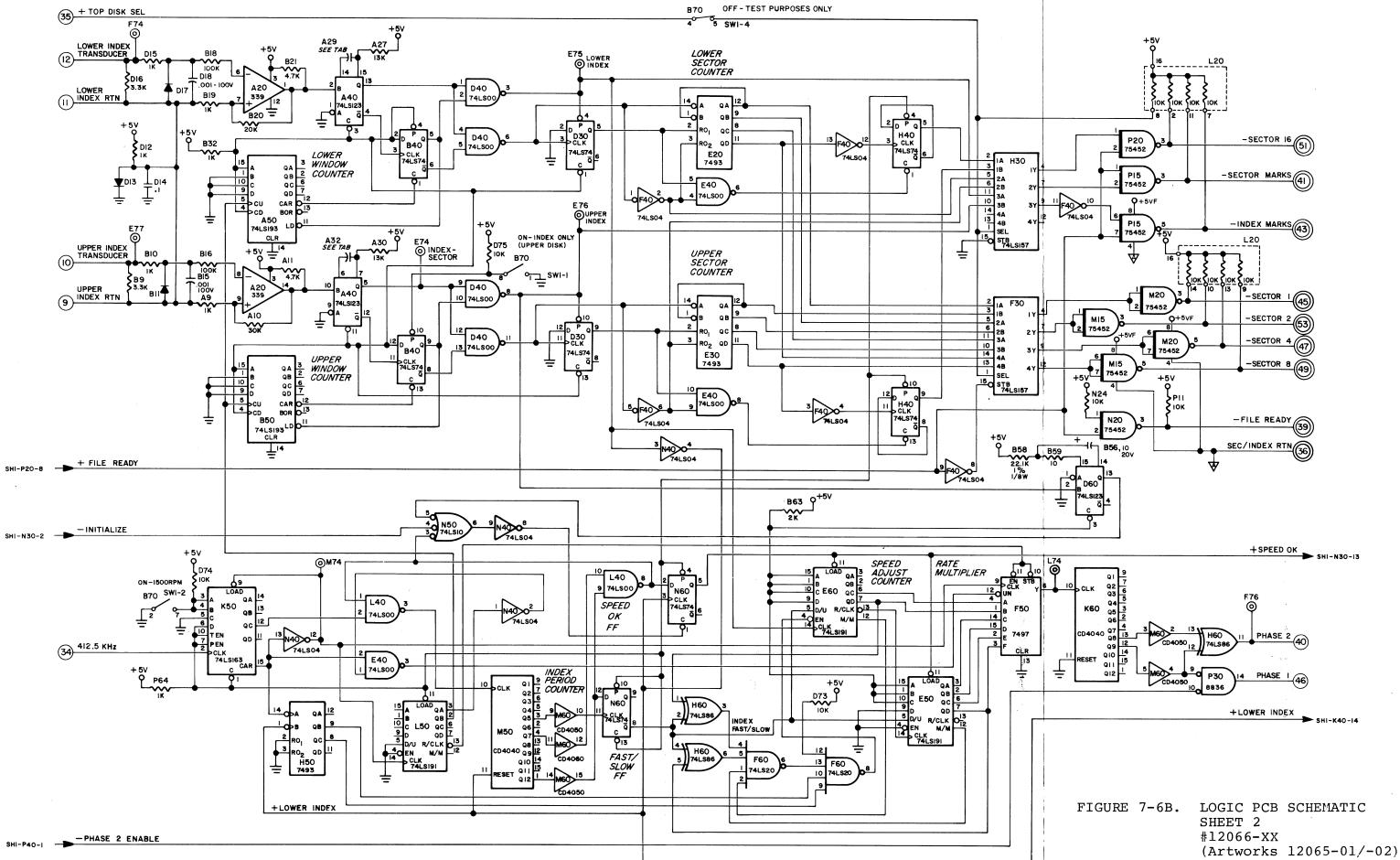

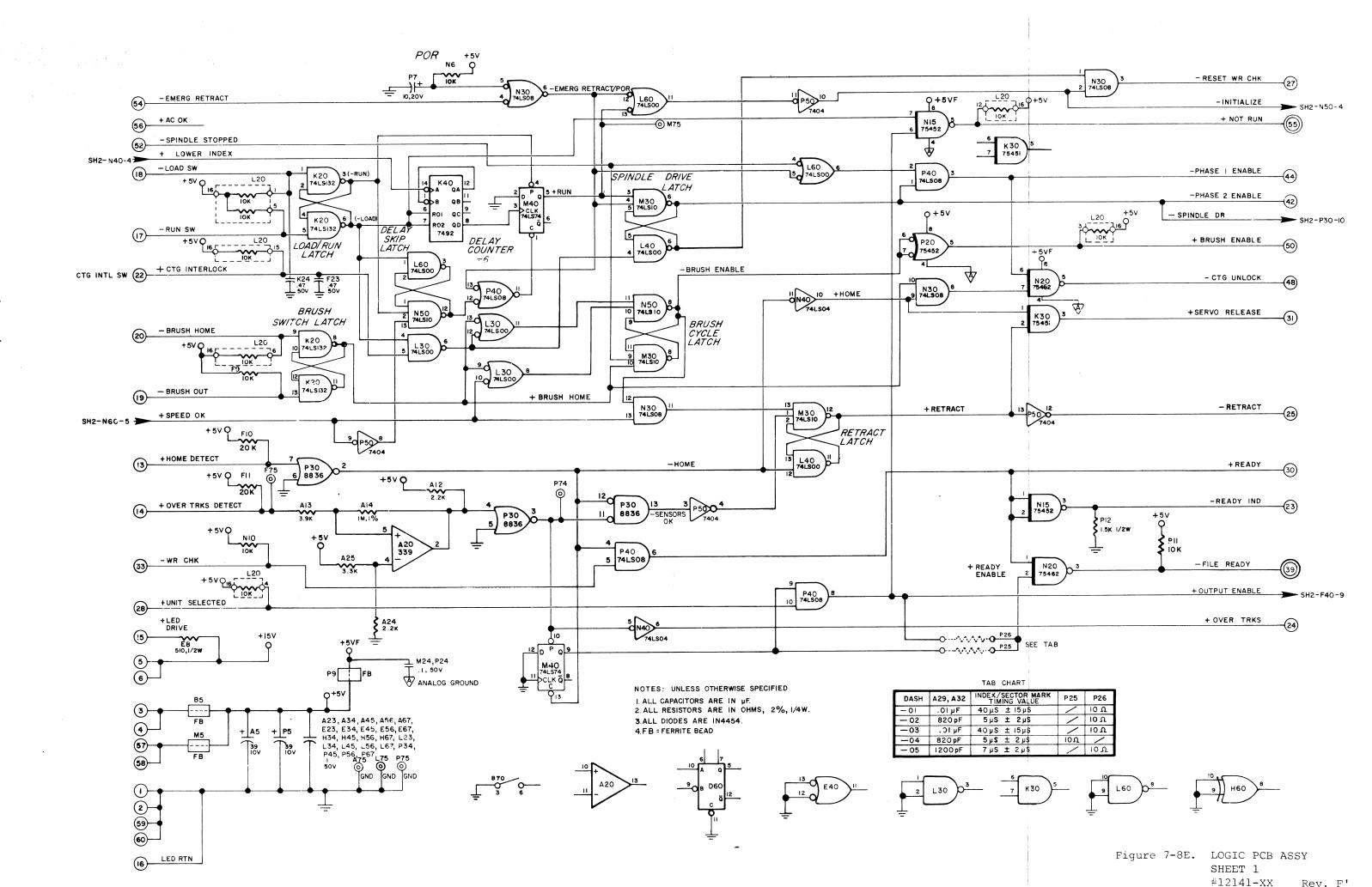

| 4.3.4 Logic (LO) PCB (#12066)                          | . 4-48 |

|--------------------------------------------------------|--------|

| 4.3.4.1 Spindle Drive Control Logic                    |        |

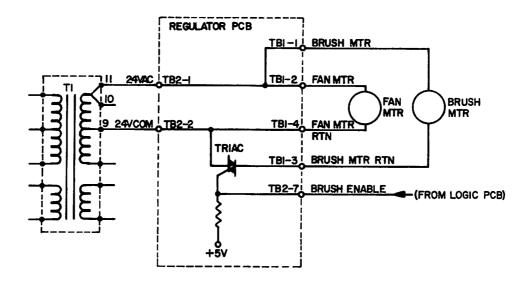

| 4.3.4.2 Brush Drive Control Logic                      |        |

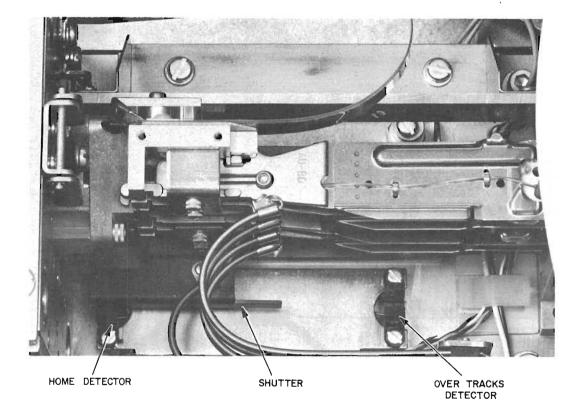

| 4.3.4.3 Home and Over Tracks Detectors                 |        |

| 4.3.4.4 Logic Control for -RETRACT, -CTG UNLOCK        | . 4-50 |

|                                                        | . 4-50 |

|                                                        |        |

|                                                        |        |

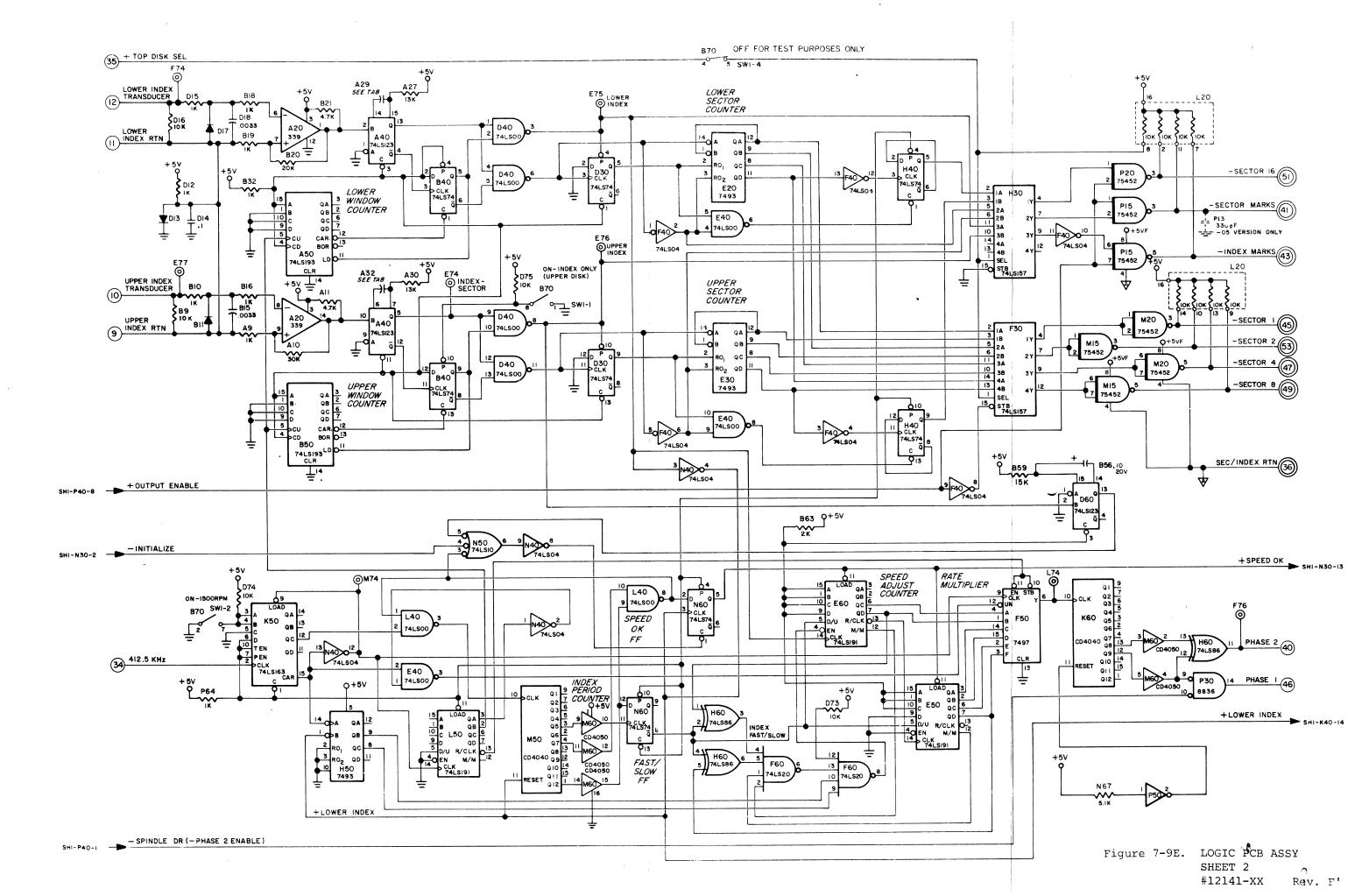

| 4.3.4.6 Index and Sector Mark Separation               |        |

| 4.3.4.7 Sector Counter                                 |        |

| 4.3.4.8 Spindle Drive Signal Generation                |        |

| 4.3.4.9 Spindle Speed Control                          |        |

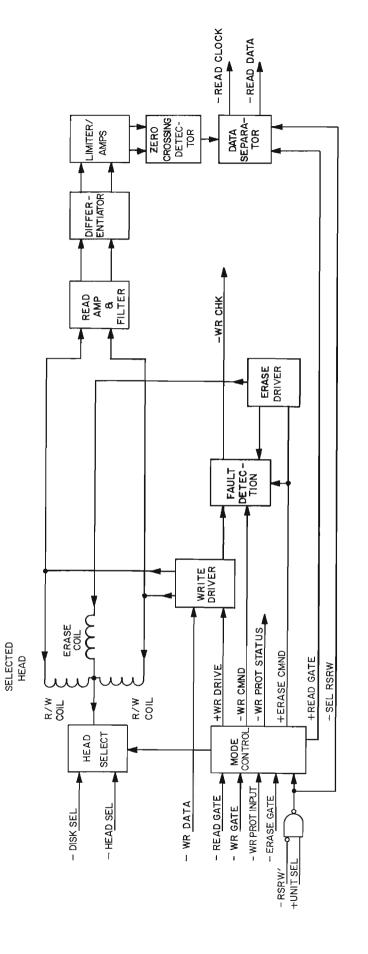

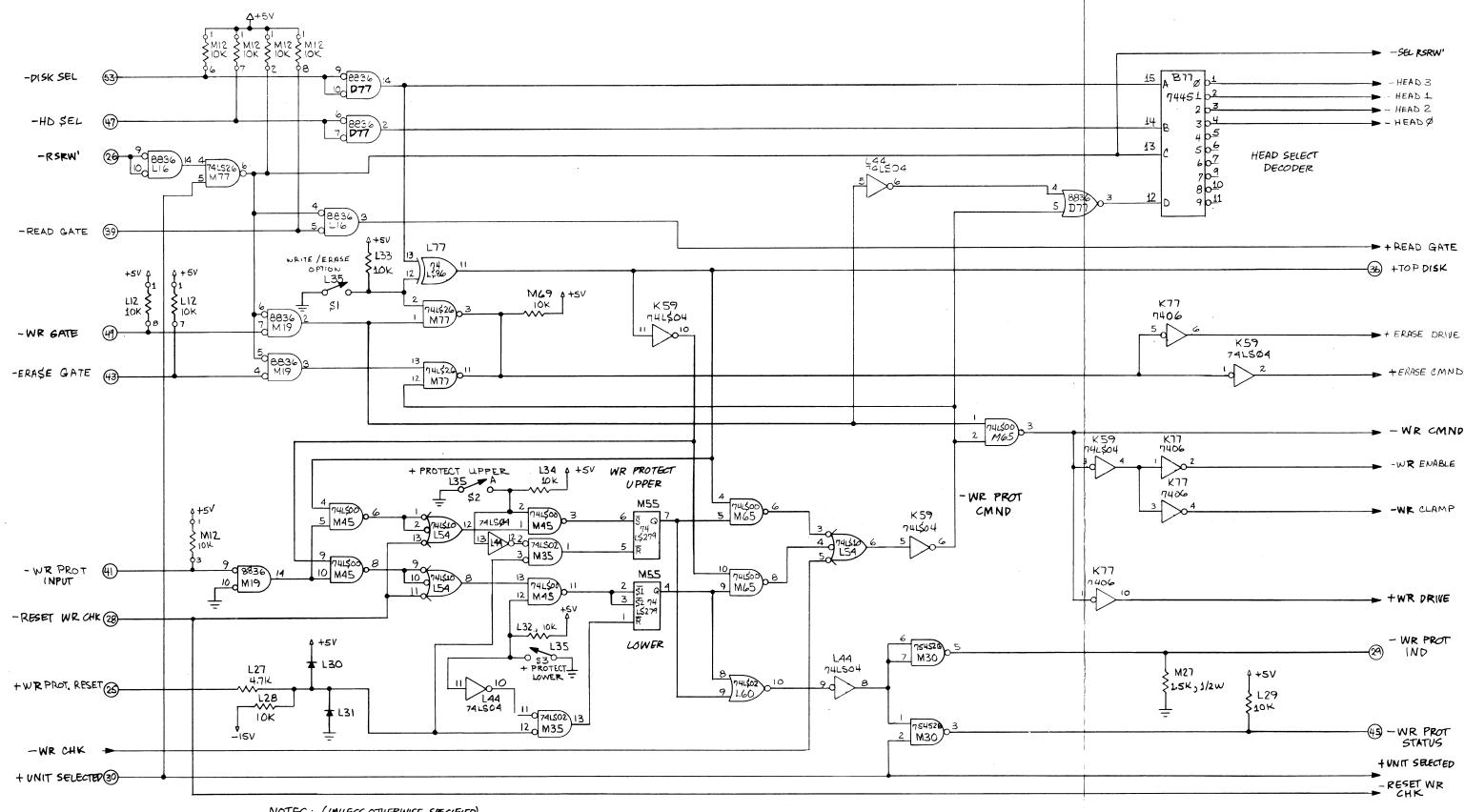

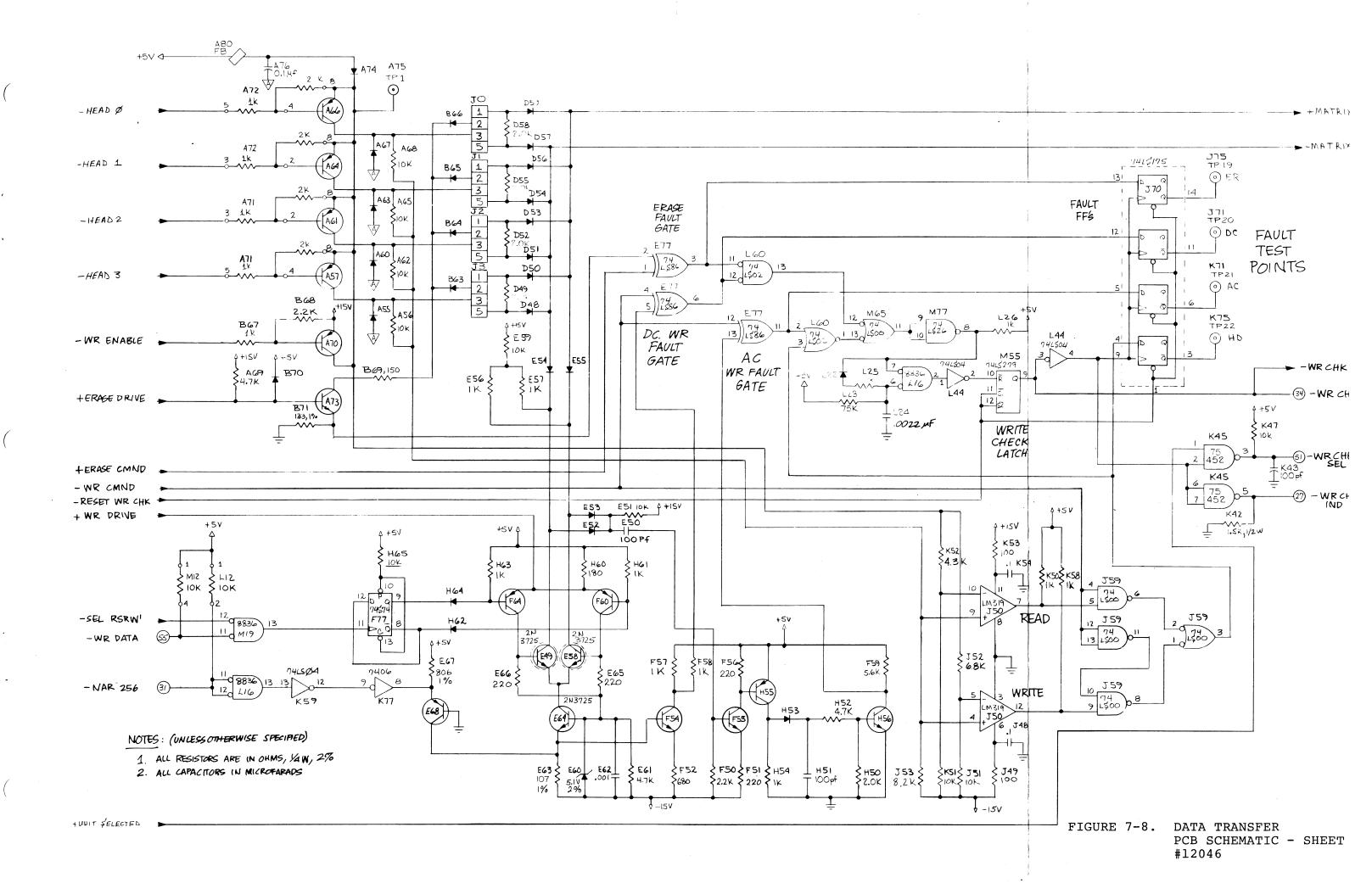

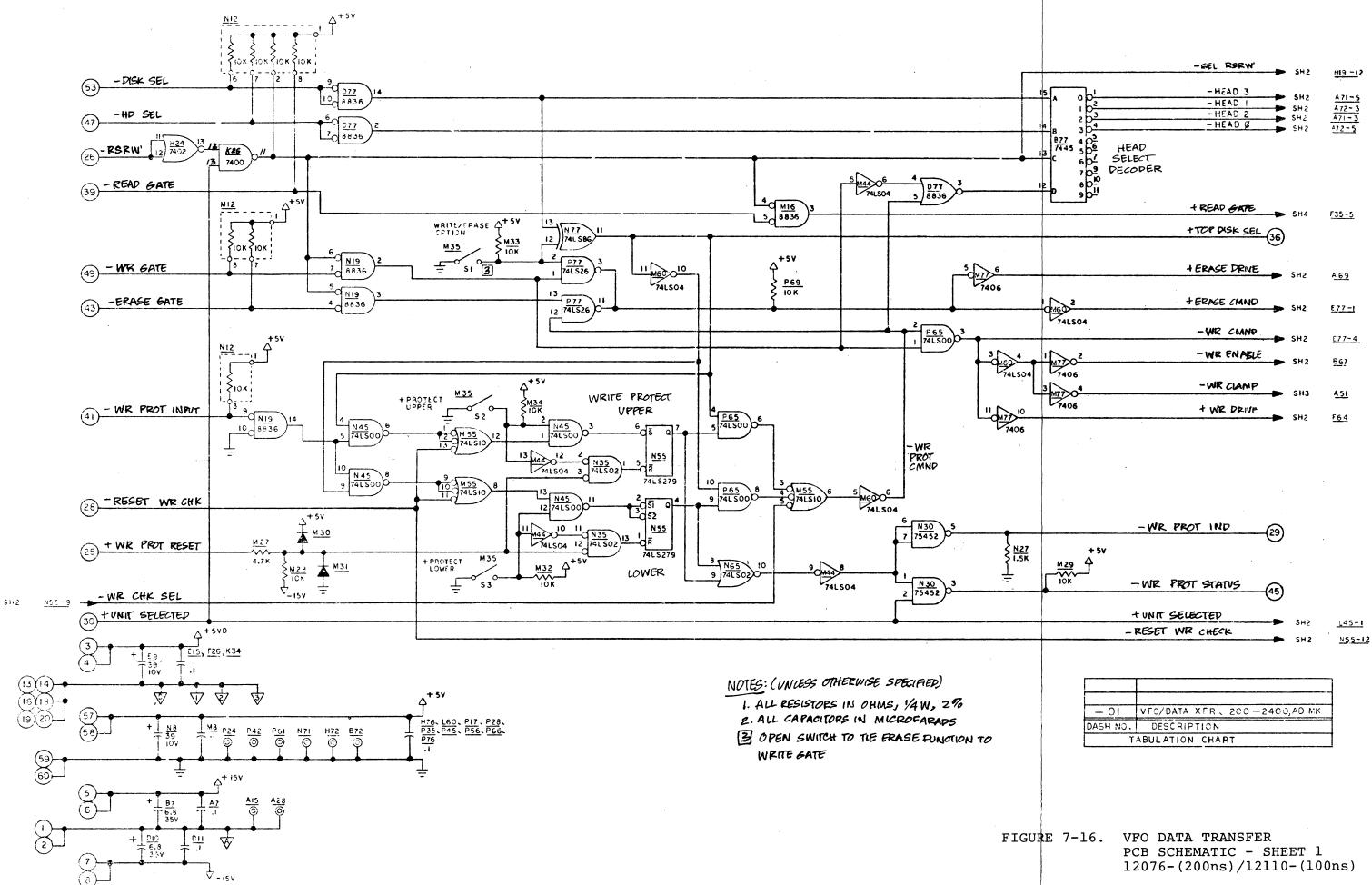

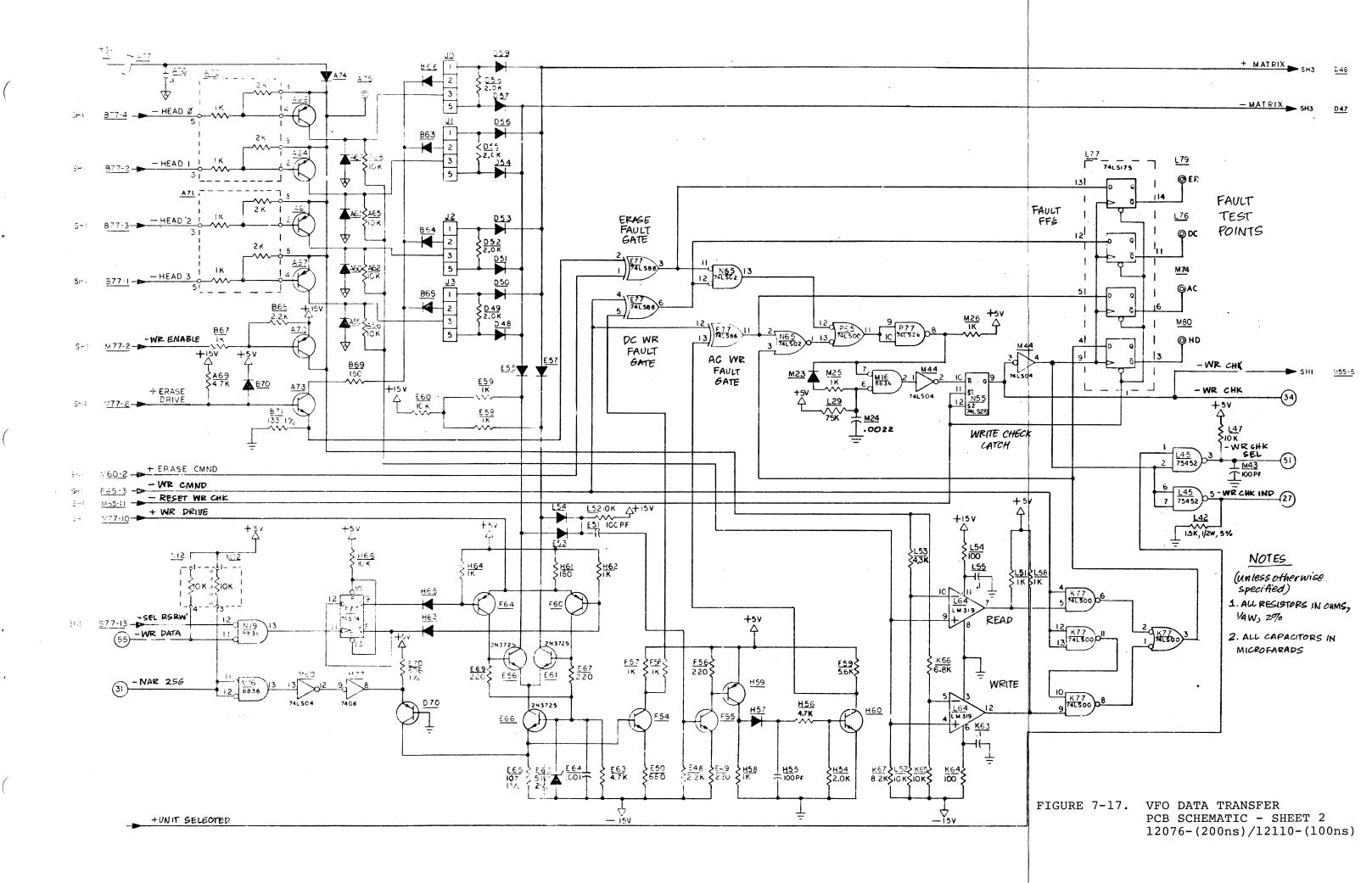

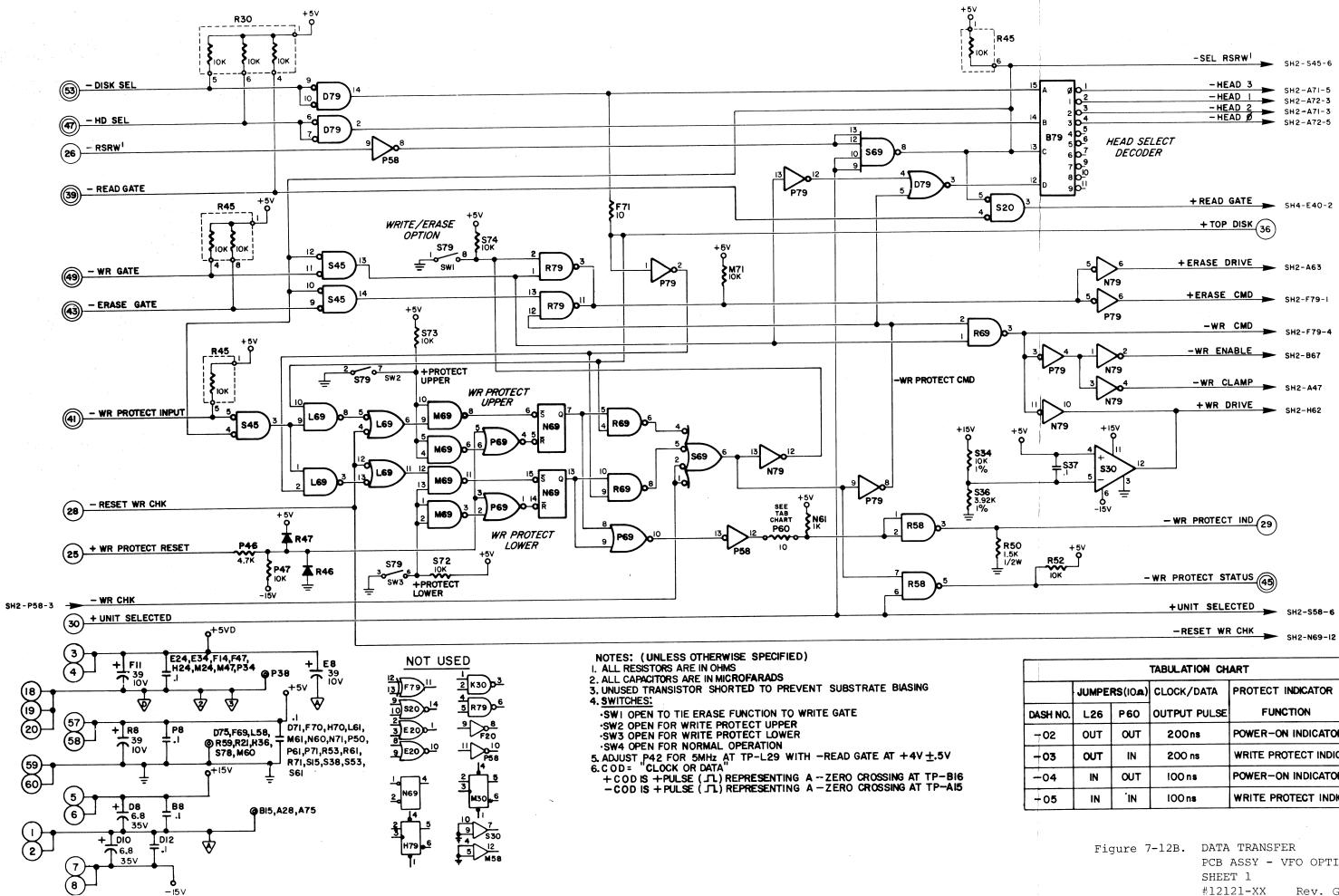

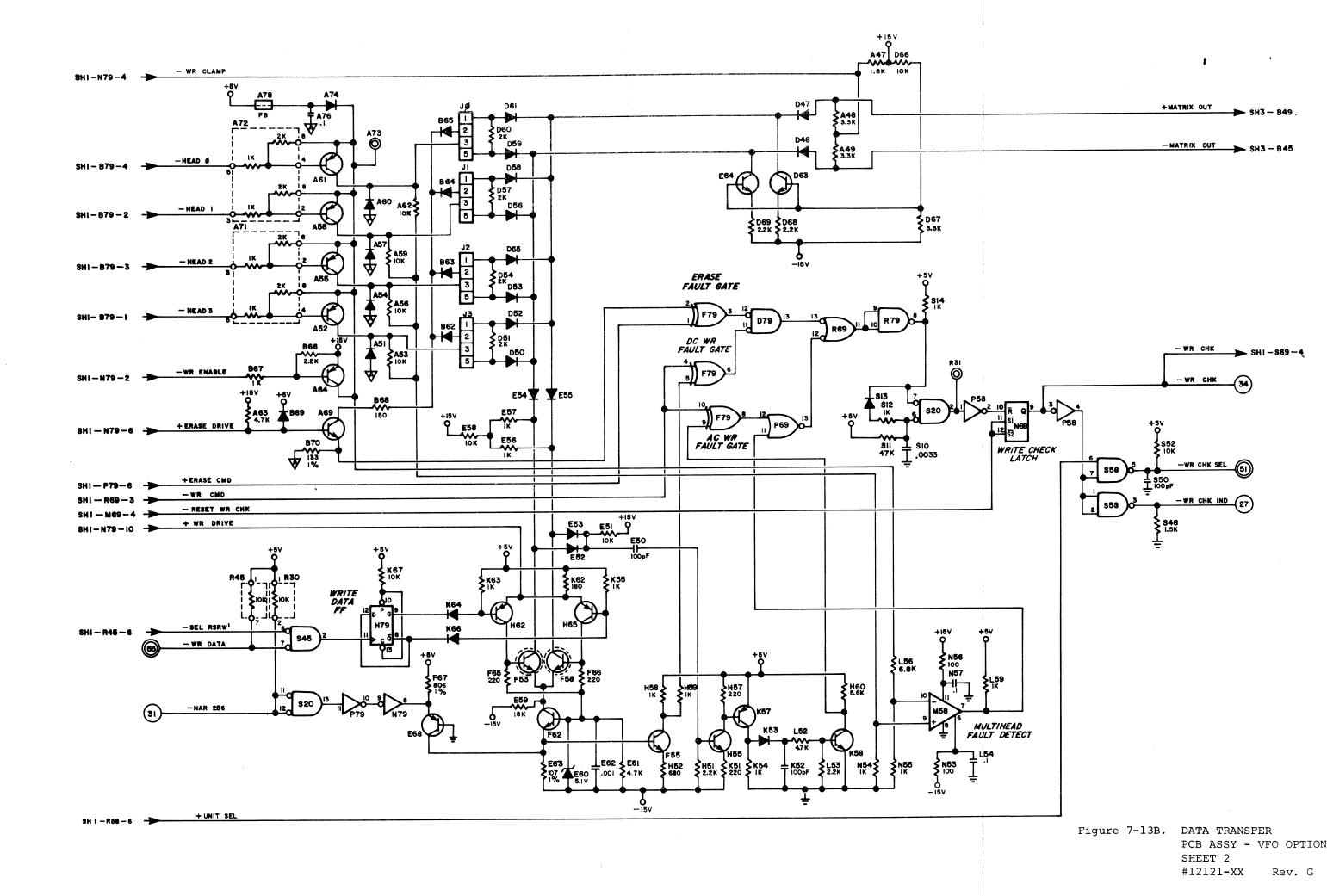

| 4.3.5 Data Transfer (D/T) PCB                          |        |

| 4.3.5.1 Head Selection                                 |        |

| 4.3.5.2 Mode Control                                   |        |

| 4.3.5.3 Write Protect                                  | . 4-64 |

| 4.3.5.4 Write Driver                                   | . 4-65 |

| 4.3.5.5 Fault Detection                                | . 4-65 |

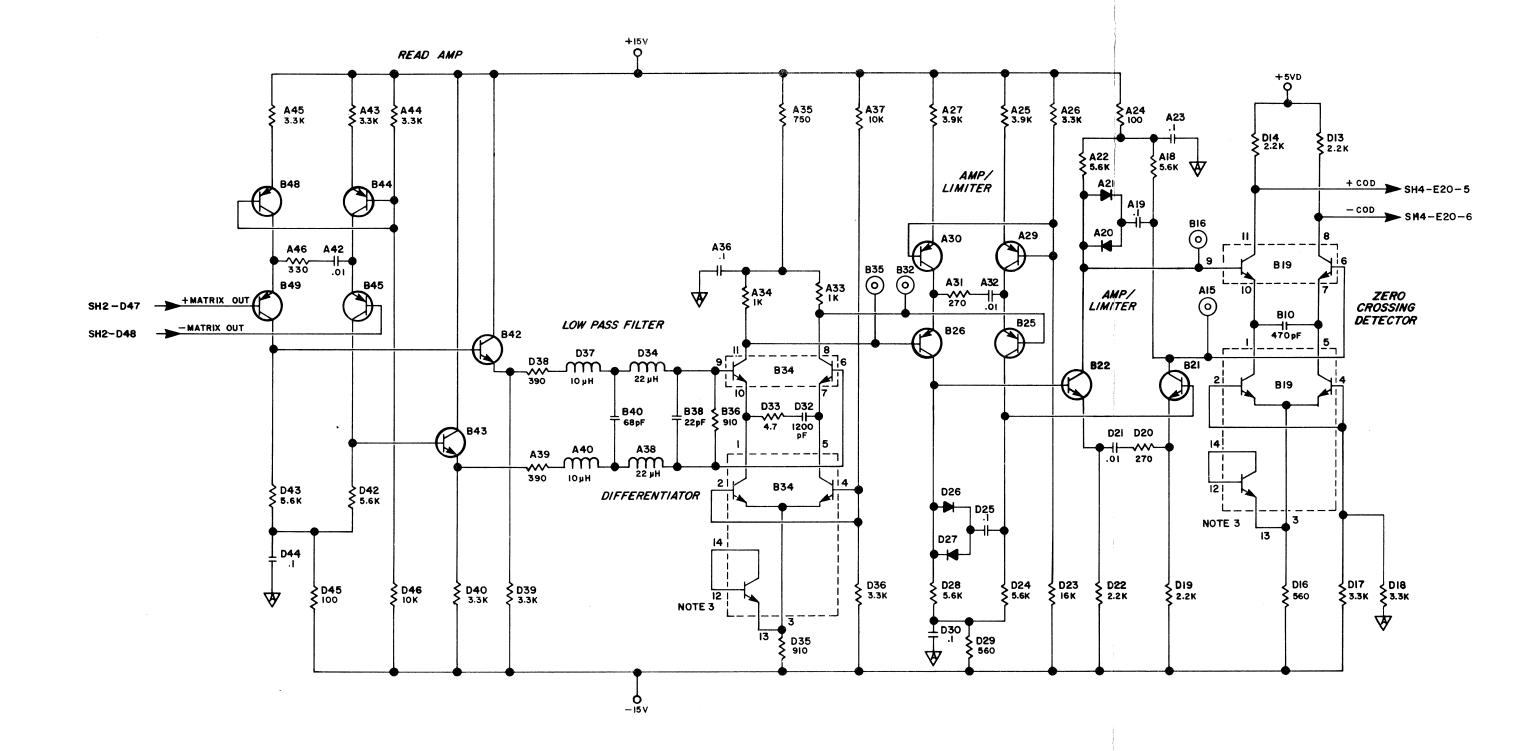

| 4.3.5.6 Read Channel                                   |        |

| 4.3.5.6.1 Head Biasing                                 | . 4-67 |

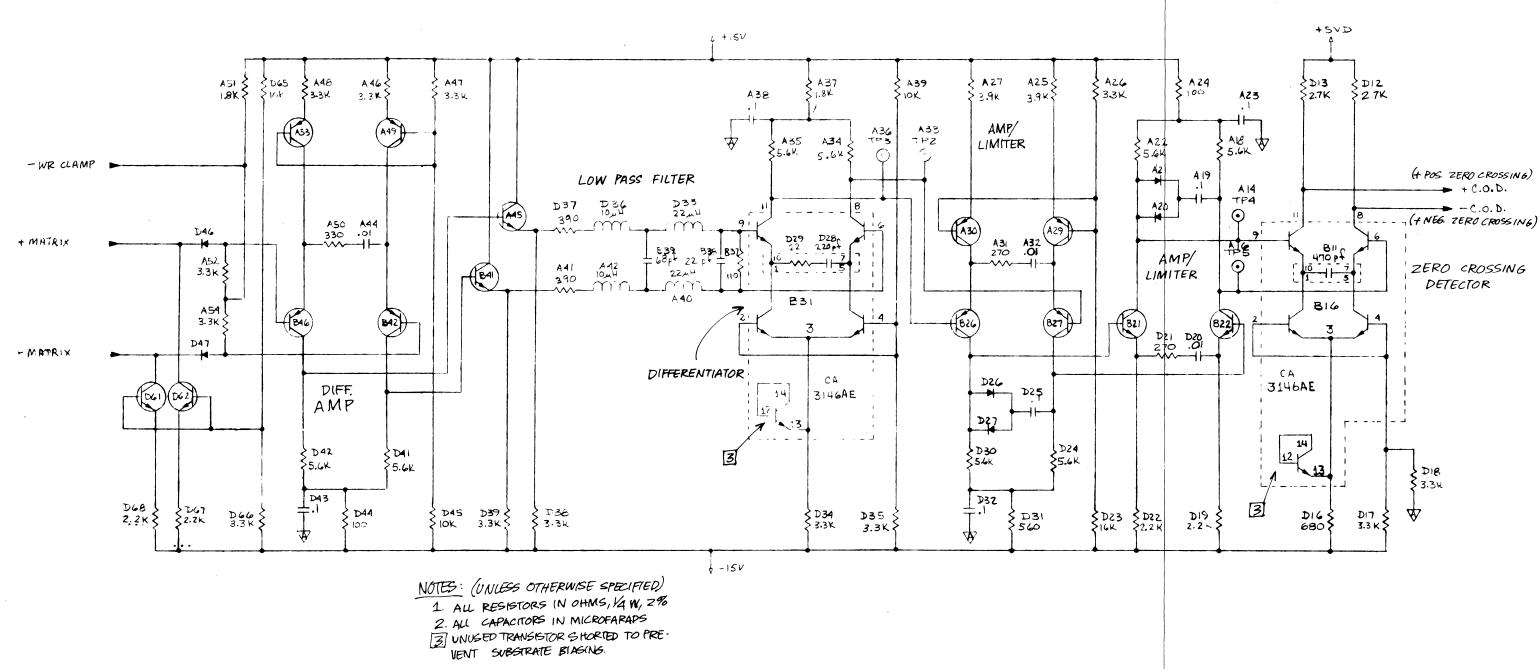

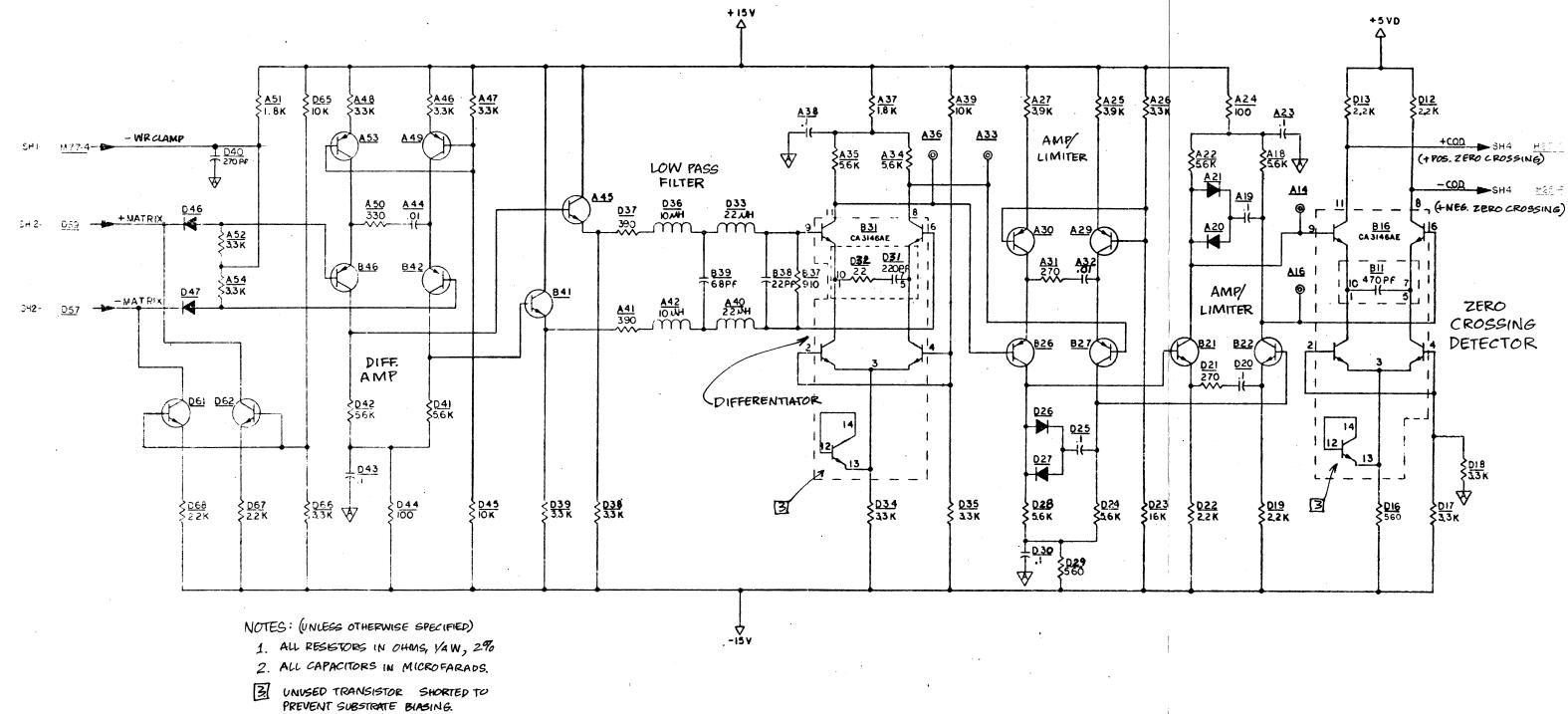

| 4.3.5.6.2 Read Amplifier and Filter                    |        |

| 4.3.5.6.3 Differentiator                               |        |

| 4.3.5.6.4 Limiter-Amplifiers                           |        |

| 4.3.5.6.5 Zero-Crossing Detector                       |        |

| 4.3.5.6.6A Single-Shot Data Separator - Standard .     |        |

| 4.3.5.6.6B VFO Data Separator - Optional (#12110)      |        |

|                                                        |        |

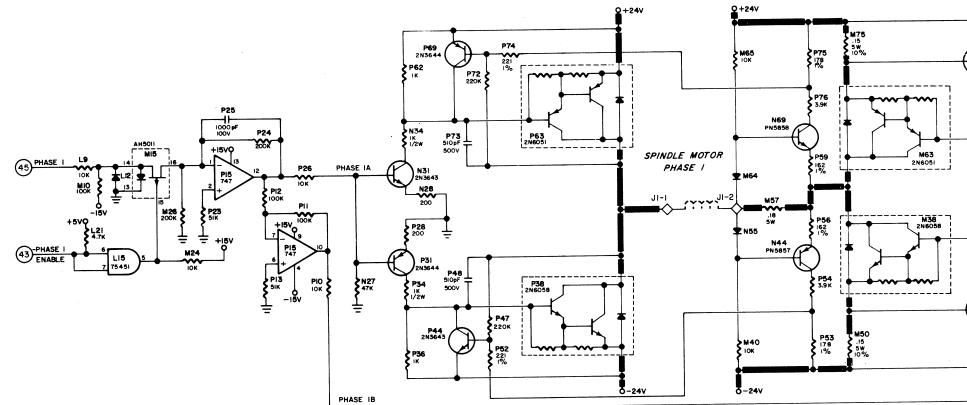

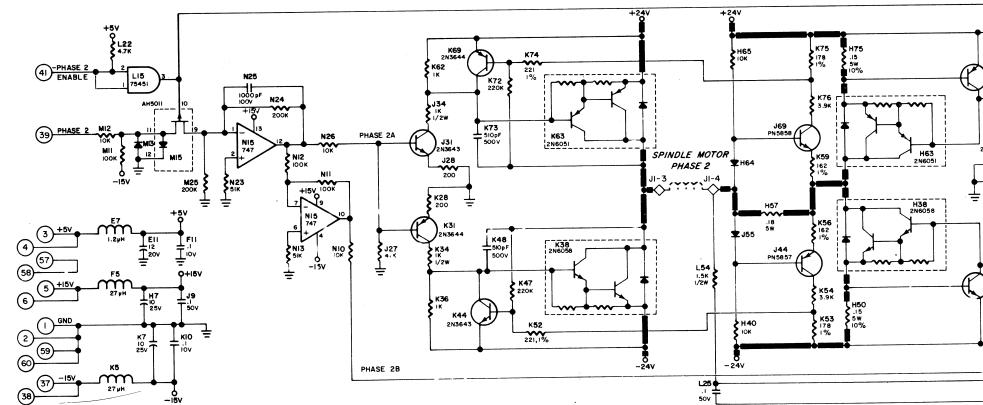

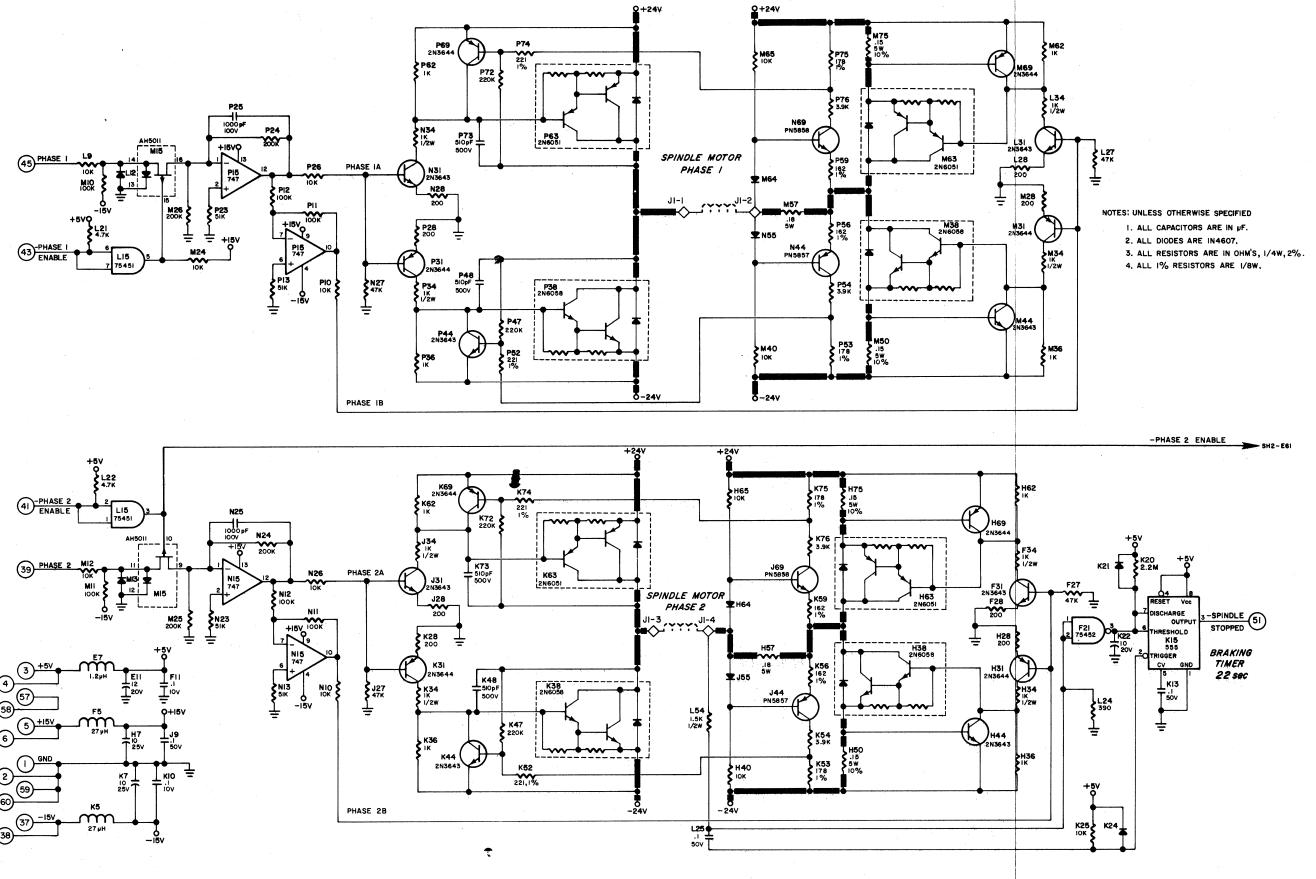

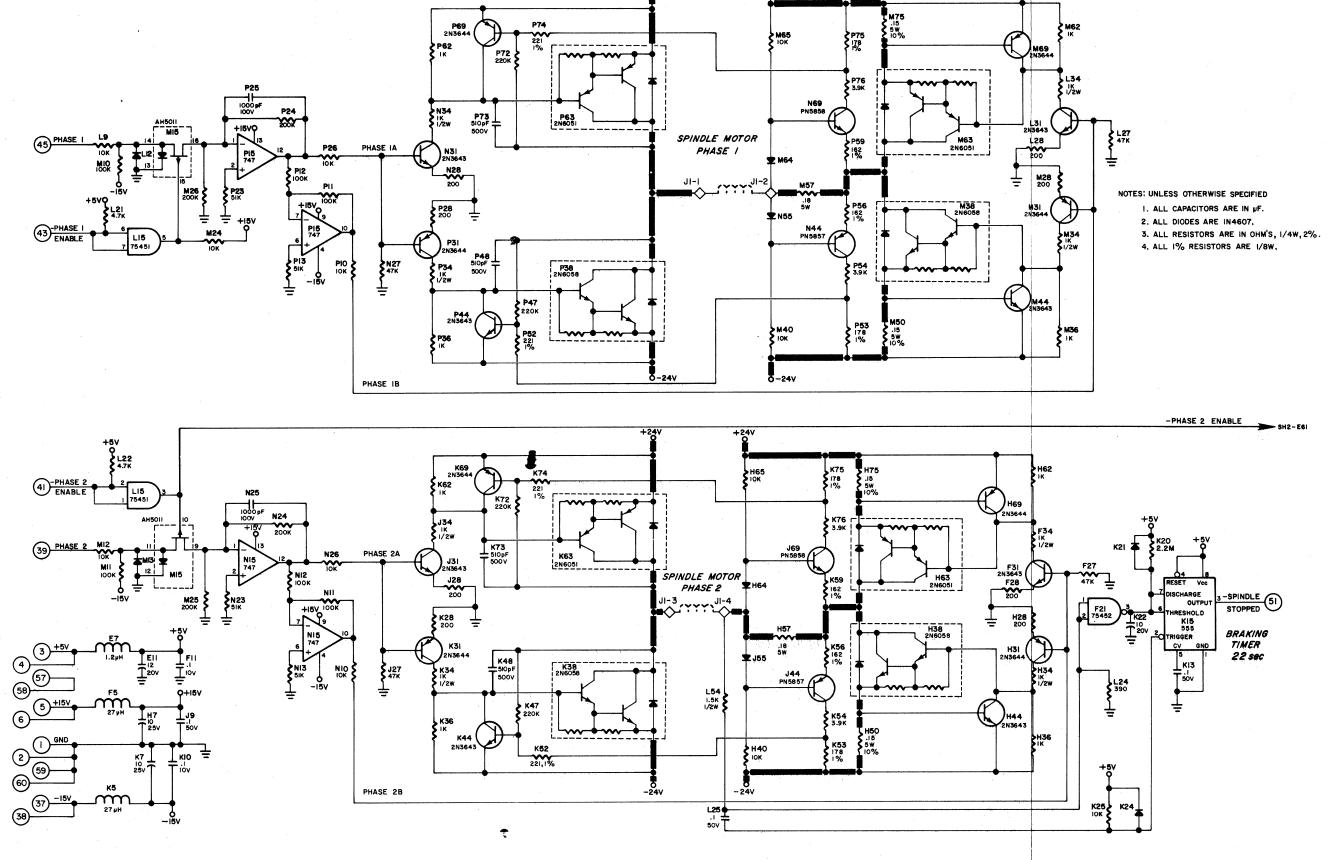

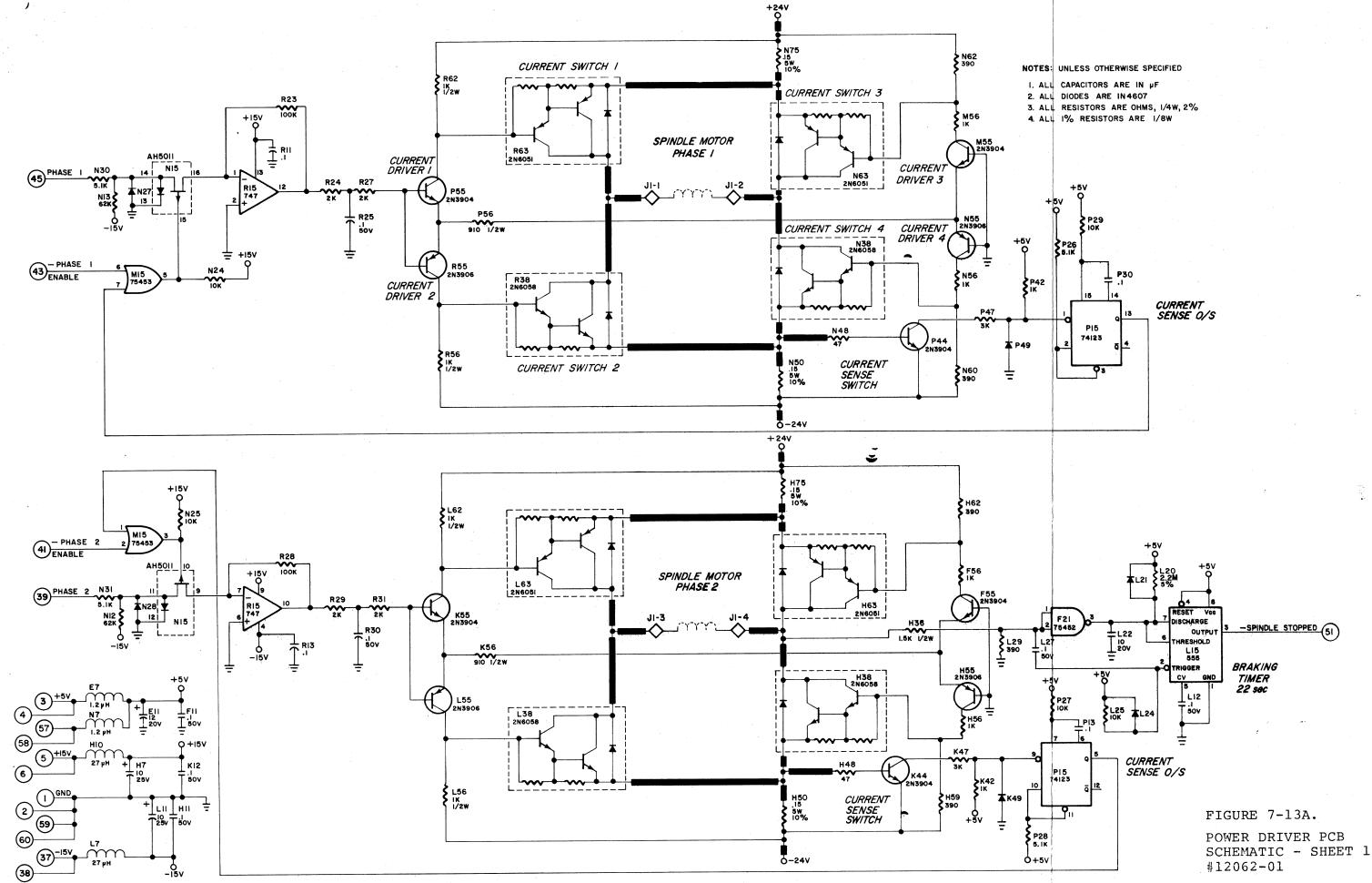

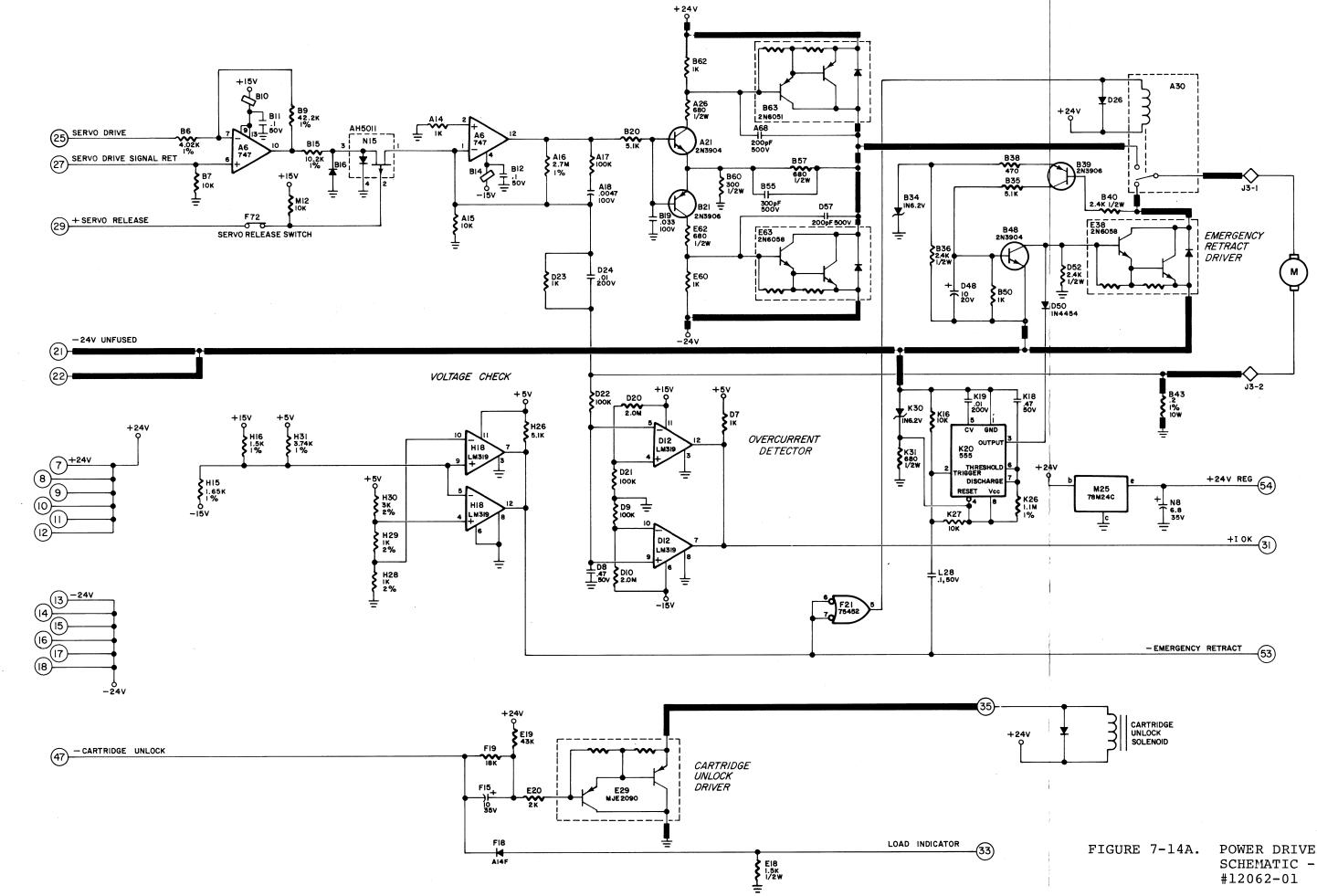

| 4.3.6 Power Driver (P/D) PCB (#12062)                  |        |

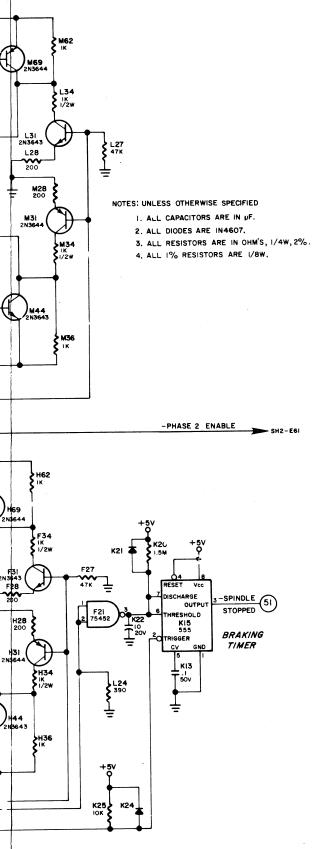

| 4.3.6.1 Spindle Motor Driver                           |        |

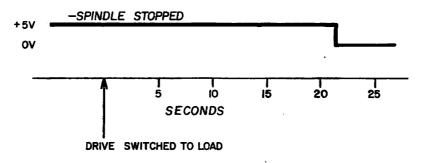

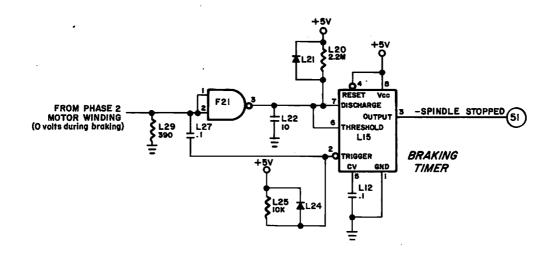

| 4.3.6.2 Braking Timer                                  |        |

| 4.3.6.3 Positioner Motor Driver                        |        |

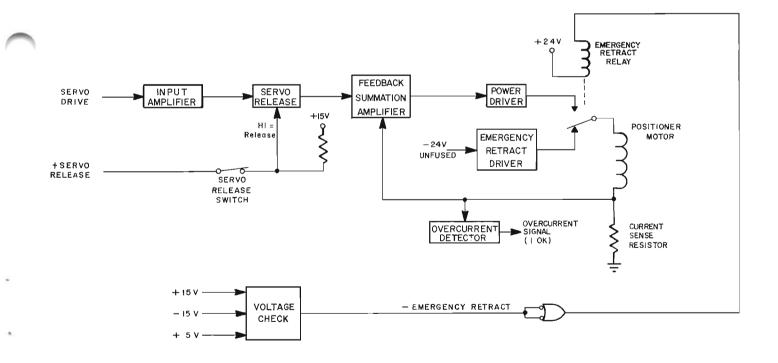

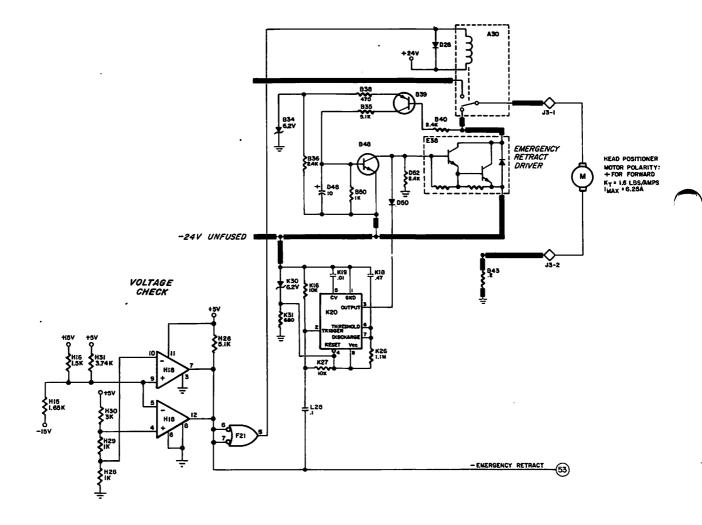

| 4.3.6.4 Voltage Check and Emergency Retract            |        |

| 4.3.6.5 Cartridge Unlock Driver                        |        |

| 4.3.6.6 +24V Regulator                                 | . 4-79 |

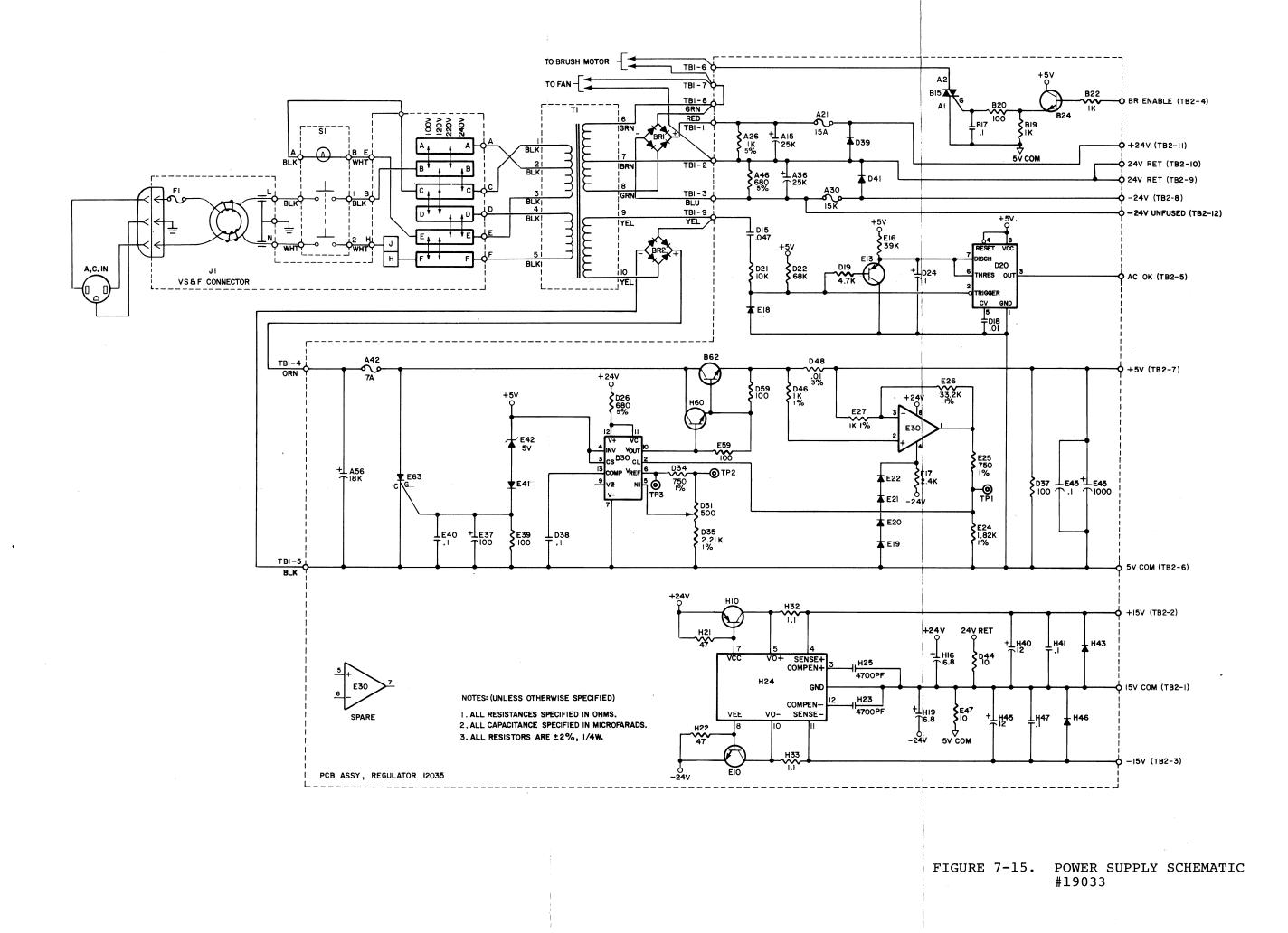

| 4.3.7 Power Supply Assembly (#19033)                   | . 4-79 |

| 4.3.7.1 General Characteristics                        | . 4-79 |

| 4.3.7.2 Theory of Operation                            | . 4-79 |

|                                                        |        |

| SECTION 5 - MAINTENANCE                                |        |

| 5.1 General Maintenance Information                    | . 5-1  |

| 5.1.1 Maintenance Requirements                         |        |

| 5.1.2 Maintenance Instructions                         |        |

| 5.1.3 Maintenance Precautions                          |        |

| 5.2 Required Tools, Test Equipment, and Spares         | . 5-2  |

| 5.2.1 Levels of Maintenance                            | . 5-2  |

| 5.2.2 Preventive Maintenance Items                     | . 5-2  |

| 5.2.3 Corrective Maintenance Items                     |        |

| 5.2.3.1 Level 1 Maintenance                            |        |

| 5.2.3.2 Level 2 Maintenance                            |        |

| 5.2.3.3 Level 3 Maintenance                            |        |

| 5.3 Location of Assemblies                             |        |

| 5.4 Preventive Maintenance                             |        |

|                                                        |        |

| 1 2                                                    |        |

| 5.4.2 Preventive Maintenance Procedures                |        |

| 5.4.2.1 Cleaning of R/W Heads                          |        |

| 5.4.2.2 Cleaning and Inspection of the Magnetic Ring . |        |

| 5.4.2.3 Replacing the Air Filter                       | . 5-7  |

|                                                                         | 5-7  |

|-------------------------------------------------------------------------|------|

| 5.5.1 Corrective Maintenance Philosophy                                 | 5-7  |

| 5.5.2 General Troubleshooting Techniques                                | 5-7  |

|                                                                         | 5-8  |

|                                                                         | 5~8  |

| 5.6.1 Adjustment Requirements                                           | 5-8  |

|                                                                         | 5-10 |

|                                                                         | 5-10 |

|                                                                         | 5-10 |

|                                                                         | 5-10 |

|                                                                         |      |

|                                                                         | 5-12 |

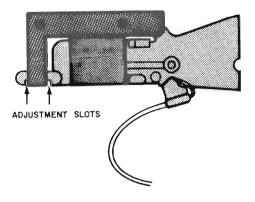

| 5.6.4.3 Adjustment of R/W Heads                                         |      |

| 5.6.4.3.1 Upper Heads                                                   |      |

| 5.6.4.3.2 Lower Heads                                                   |      |

| 5.6.4.4 Upper Index Transducer Adjustment                               |      |

| 5.6.4.5 Track Zero Adjustment                                           |      |

|                                                                         | 5-25 |

|                                                                         | 5-25 |

| 5.7 Removal/Replacement of Assemblies and Parts                         | 5-25 |

| 5.7.1 Level l Removal/Replacement                                       | 5-25 |

| 5.7.1.1 Top Cover                                                       | 5-25 |

|                                                                         | 5-25 |

|                                                                         | 5-26 |

|                                                                         | 5-26 |

|                                                                         | 5-26 |

|                                                                         | 5-26 |

|                                                                         | 5-26 |

|                                                                         | 5-28 |

| $5.7.1.9$ Brushes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 5-28 |

|                                                                         | 5-28 |

| 5.7.1.10 Slide Assemblies                                               | 5-28 |

| 5.7.2 Level 2 Removal/Replacement                                       |      |

| 5.7.2.1 R/W Heads                                                       | 5-28 |

| 5.7.2.1.1 Removal                                                       | 5-28 |

| 5.7.2.1.2 Installation                                                  | 5-29 |

| 5.7.2.2 Lower Disk                                                      | 5-29 |

|                                                                         | 5-29 |

| 5.7.2.2.2 Installation                                                  | 5-29 |

| 5.7.2.3 Brush Motor                                                     | 5-30 |

| 5.7.2.3.1 Removal                                                       | 5-30 |

| 5.7.2.3.2 Installation                                                  | 5-30 |

| 5.7.2.4 Index Transducers                                               | 5-31 |

| 5.7.2.4.1 Upper Index Transducer                                        | 5-31 |

| 5.7.2.4.2 Lower Index Transducer                                        | 5-31 |

| 5.7.3 Level 3 Removal/Replacement                                       | 5-31 |

| 5.7.3.1 Bowl Assembly                                                   | 5-31 |

| 5.7.3.1.1 Removal                                                       | 5-31 |

| 5.7.3.1.2 Installation                                                  | 5-32 |

| 5.7.3.2 Cartridge Retainer Assembly                                     | 5-32 |

| 5.7.3.3 Baseplate-Mounted Components                                    | 5-32 |

| 5.7.3.4 Spindle Assembly                                                | 5-32 |

| 5.7.3.5 Head Positioner                                                 | 5-33 |

| Strifts Head Fostblonds                                                 | 2 33 |

| SECTION 6 - APPENDICES                                                  |      |

| 6.1 Options                                                             | 6-1  |

| 6.2 Accessories                                                         |      |

| 0.2 ACCEDULTED                                                          | U 4  |

# SECTION 7 - CIRCUIT DIAGRAMS AND CONVENTIONS

¢

×.

| 7.1 Diab | olo Circuit Diagram Conventions | 7-1 |

|----------|---------------------------------|-----|

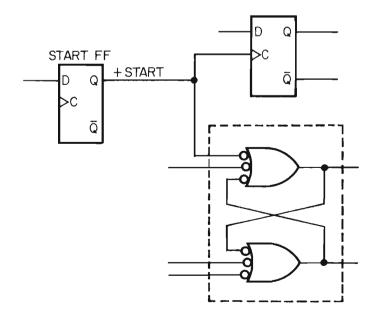

| 7.1.1    | Functional Logic                | 7-1 |

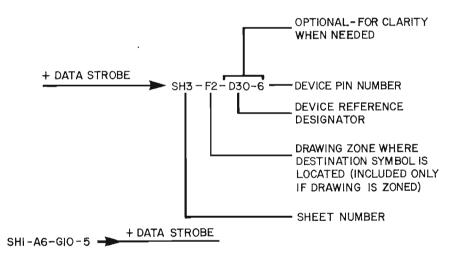

| 7.1.2    | Signal Nomenclature             | 7-2 |

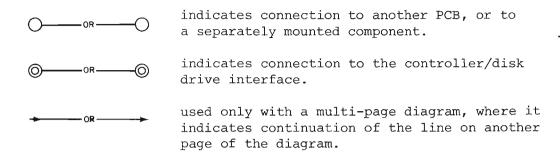

| 7.1.3    | Diagram Input/Output Symbol     | 7-3 |

| 7.1.4    | Interpage Referencing           | 7-3 |

|          | Logic Symbology                 |     |

|          | grated Circuit Reference        |     |

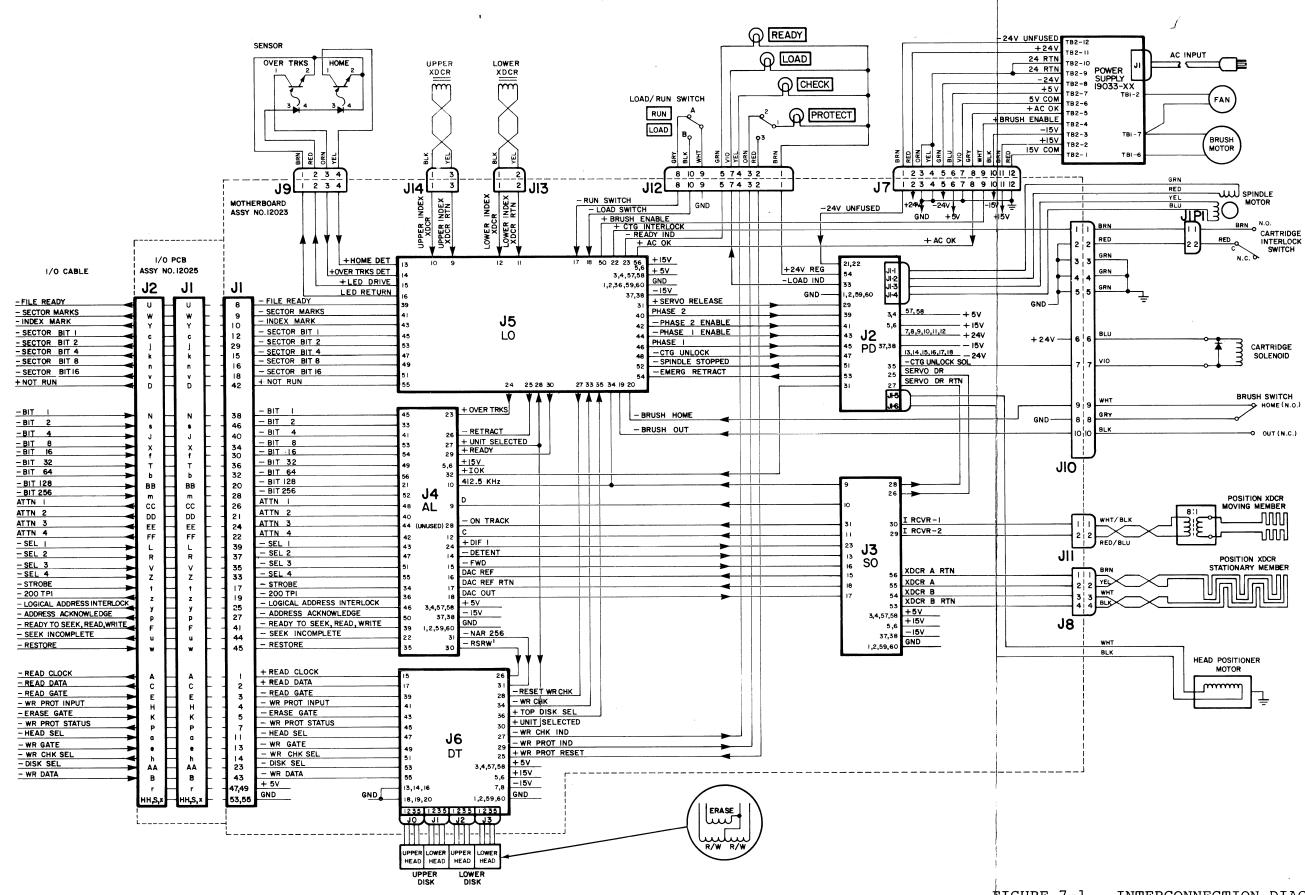

| 7.3 Circ | cuit Diagrams                   | 7-6 |

# LIST OF ILLUSTRATIONS

| Figure |                                           |      |

|--------|-------------------------------------------|------|

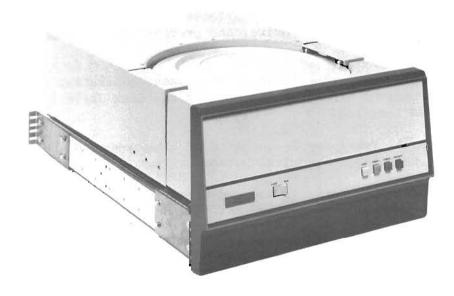

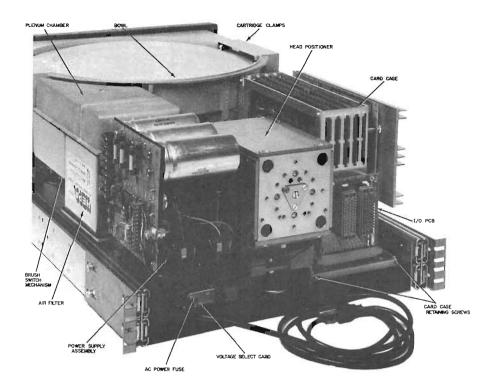

| 1-1    | Diablo Systems, Inc. Model 44B Disk Drive | 1-2  |

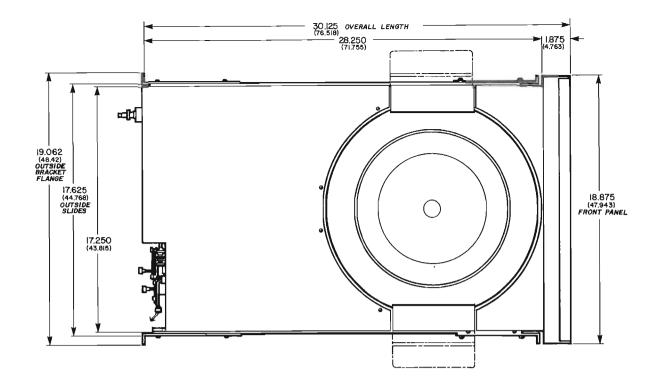

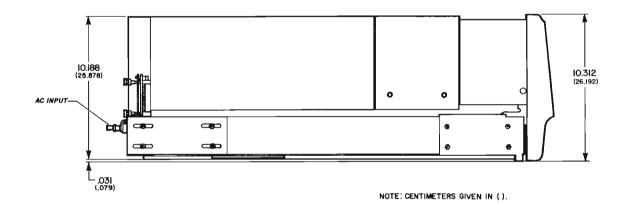

| 2-1    | Model 44B Basic Dimensions                | 2-2  |

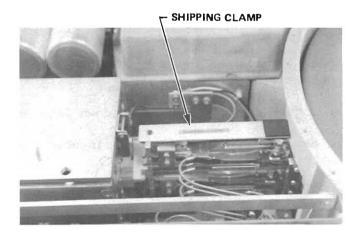

| 2-2    | Head Positioner Shipping Clamp            | 2-2  |

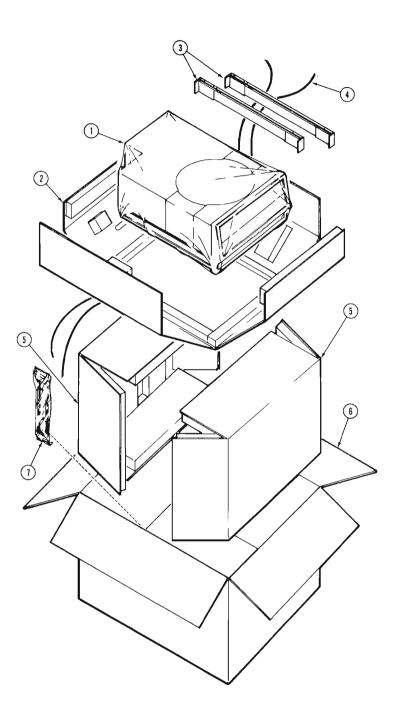

| 2-3    | Shipping Container Assembly               | 2-3  |

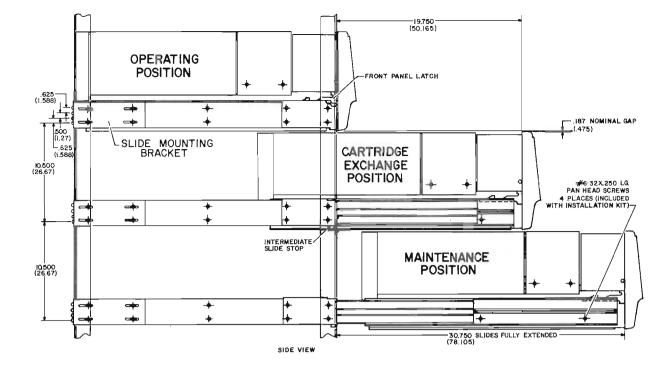

| 2-4    | Model 44B Rack Mount Positions            | 2-5  |

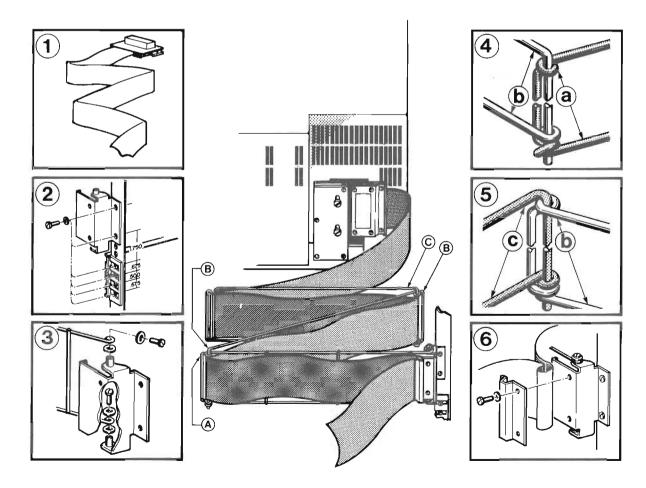

| 2-5    | I/O Cable Carrier Assembly                | 2-5  |

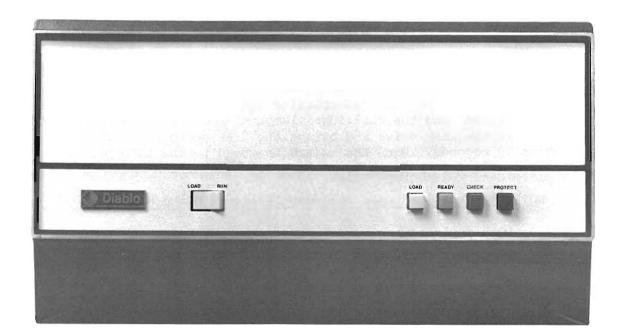

| 2-6    | Front Panel, Model 44B Disk Drive         | 2-8  |

| 2-7    | Opening the Equipment Drawer              | 2-11 |

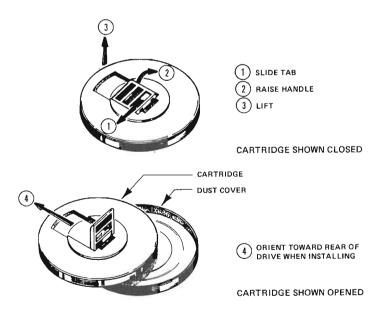

| 2-8    | Opening the Type 5440 Disk Cartridge      | 2-11 |

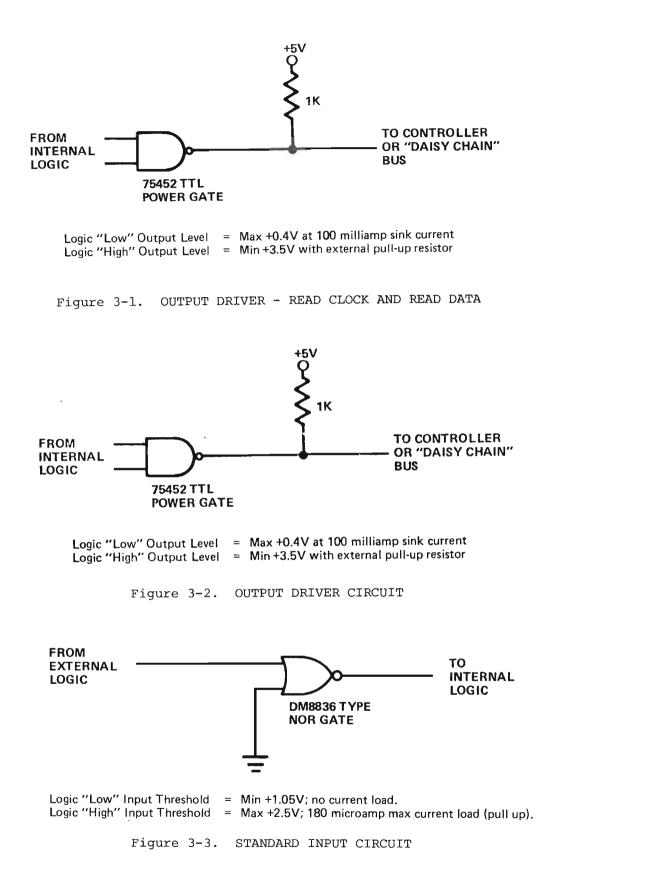

| 3-1    | Output Driver - Read Clock and Read Data  | 3-8  |

| 3-2    | Output Driver Circuit                     | 3-8  |

| 3-3    | Standard Input Circuit                    | 3-8  |

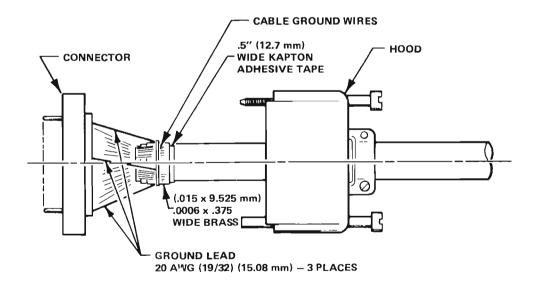

| 34     | Interface Connector Assembly              | 3-10 |

| 3-5    | Waveshapes                                | 3-12 |

| 3-6    | Daisy Chain and Terminator                | 3-12 |

| 3-7    | Double Frequency Recording                | 3-13 |

| 3-8    | Typical Sector Format                     | 3-15 |

| 3-9    | Address Mark Format                       | 3-21 |

| 3-10   | Address Marks                             | 3-21 |

| 3-11   | Typical System Timing                     |      |

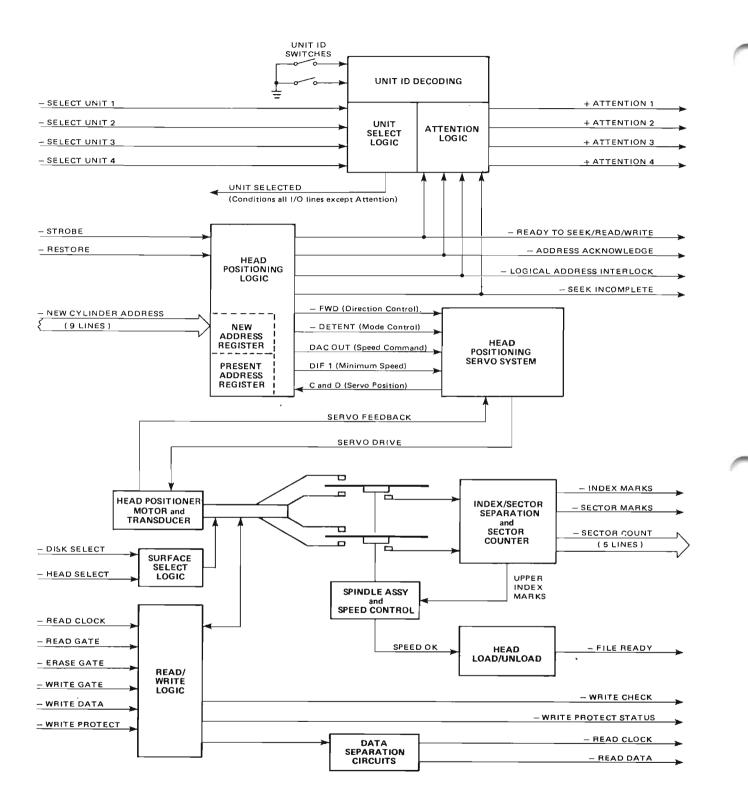

| 4-1    | Model 44B Functional Block Diagram        | 4-2  |

| 4-2    | Head Load/Unload Ramp                     | 4-5  |

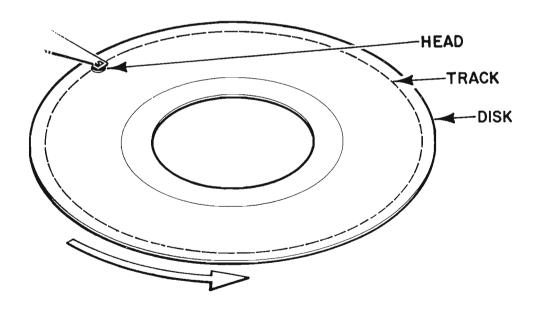

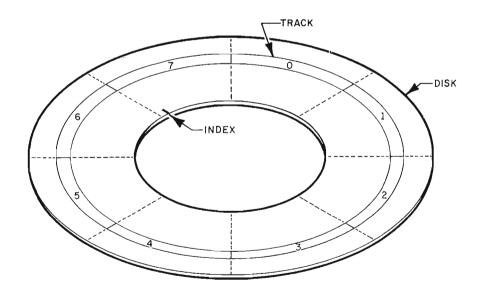

| 4-3    | Track Layout                              | 4-7  |

| 4 - 4  | Head Positioning Block Diagram            | 4-8  |

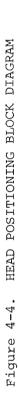

| 4-5    | Normal Seek Flow Chart                    | 49   |

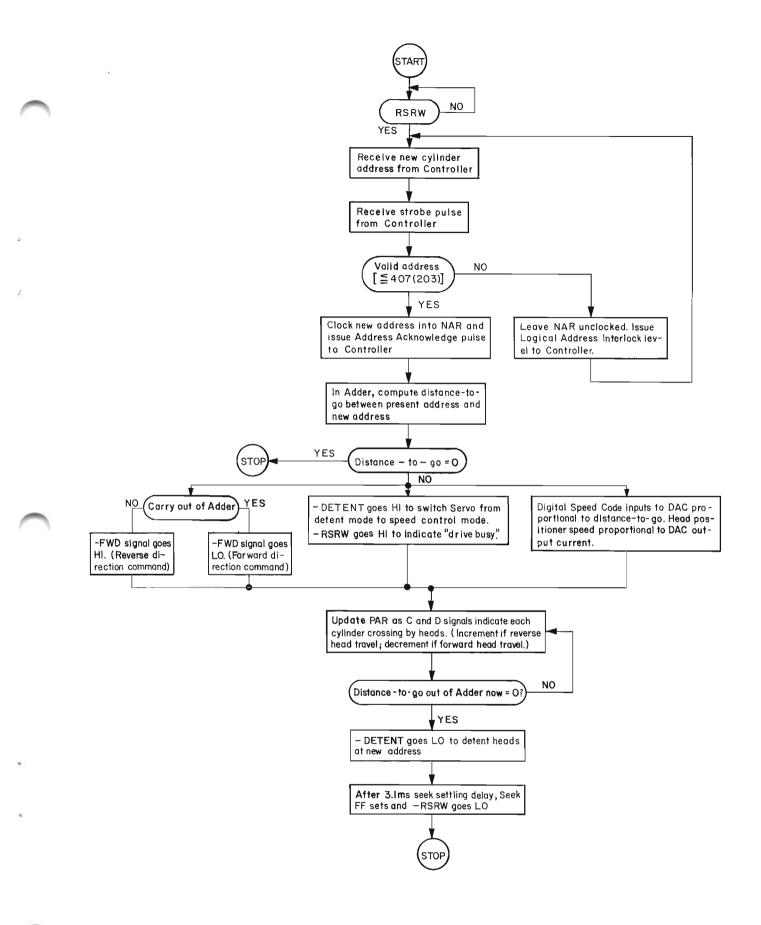

| 4-6    | Servo System Simplified Block Diagram     | 4-12 |

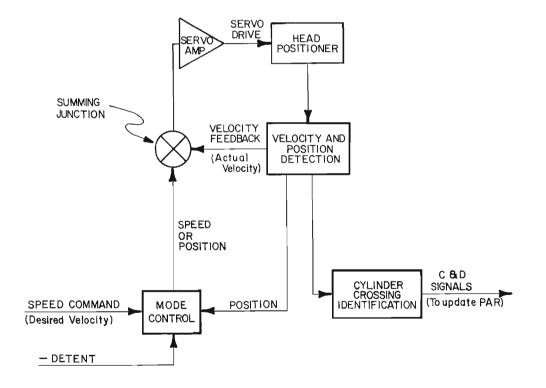

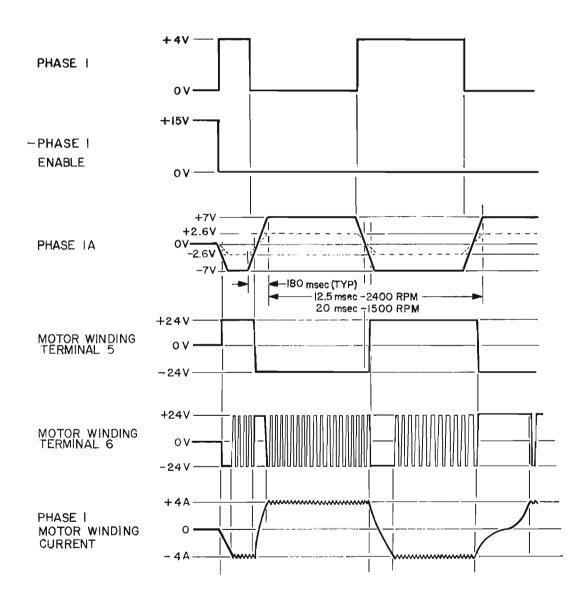

| 4-7    | Servo Waveforms                           | 4-13 |

| 4-8    | Servo System Expanded Block Diagram       | 4-14 |

| 4-9    | Position Transducer                       | 4-16 |

| 4-10   | Transducer Output Phase Shift             | 4-18 |

| 4-11   | Velocity and Position Waveforms           |      |

| 4-12   | Disk Sector Layout                        | 4-21 |

| 4-13   | Data Transfer Functional Block Diagram    |      |

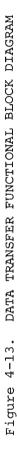

| 4-14   | Read/Write Heads                          |      |

| 4-15   | Count Control Waveforms                   |      |

| 4-16   | Distance-To-Go Examples                   |      |

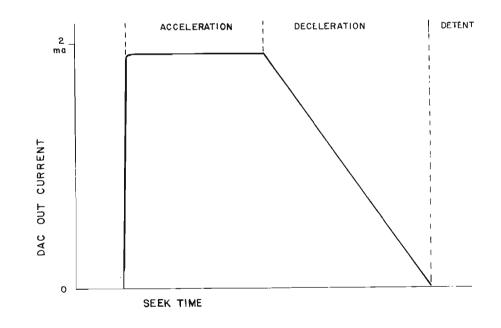

| 4-17   | DAC Output Current                        |      |

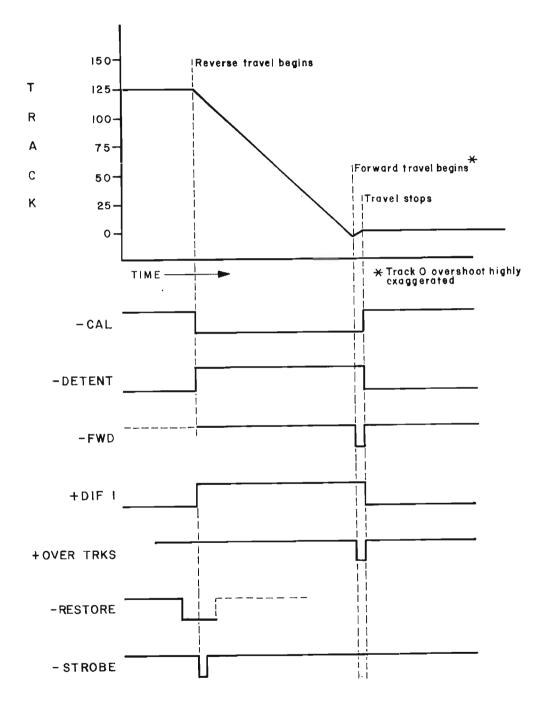

| 4-18   | Restore from Cylinder 125                 |      |

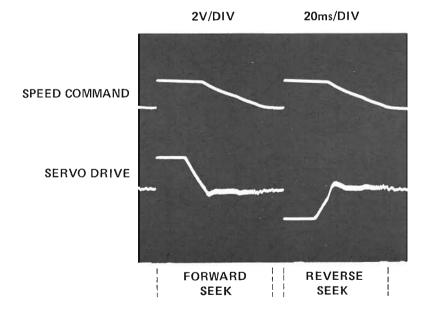

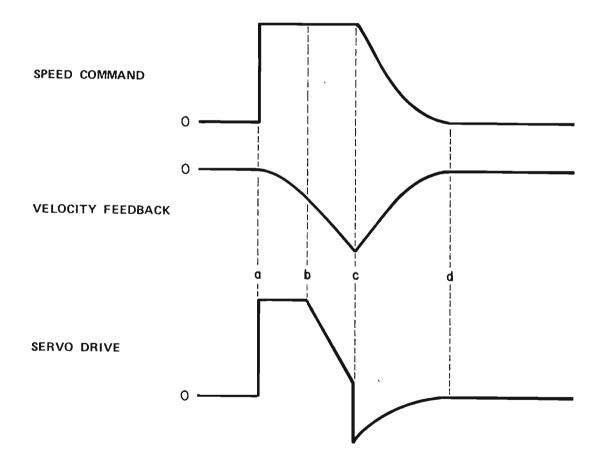

| 4-19   | Speed Command and Servo Drive             | 4-39 |

| Figure |                                                                      |     |

|--------|----------------------------------------------------------------------|-----|

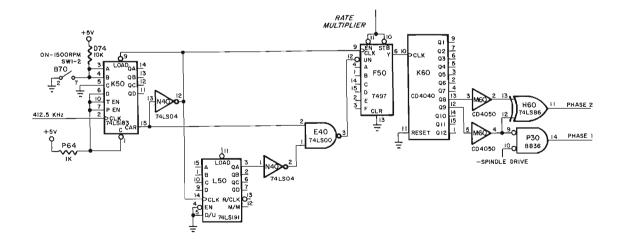

| 4-20   | Servo Waveforms                                                      | 40  |

| 4-21   | XDCR Signal Generation                                               | 42  |

| 4-22   | XDCR A and XDCR B                                                    | 42  |

| 4-23   | Odd Sawtooth Flip-Flop Switching 4-                                  |     |

| 4-24   | Sawtooth Generation                                                  | 44  |

| 4-25   | Feedback FET Switching Signals 4-                                    | 46  |

| 4-26   | Velocity and Position Waveforms 4-                                   | 47  |

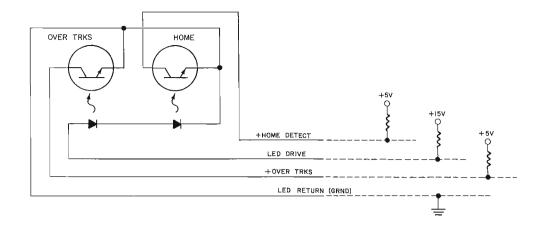

| 4-27   | Head Position Detectors                                              | 51  |

| 4-28   | Head Position Detector Circuits 4-                                   | 52  |

| 4-29   | Head Position Detector Signals 4-                                    | 52  |

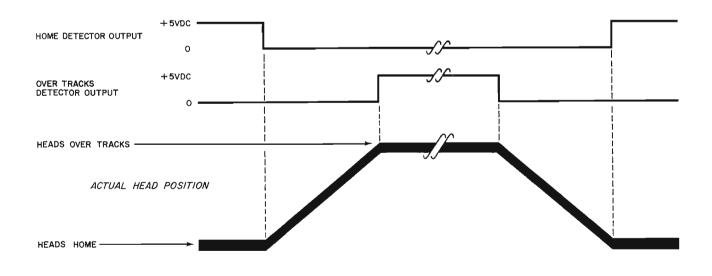

| 4-30   | Index/Sector Separation Waveforms (2400 RPM) 4-                      |     |

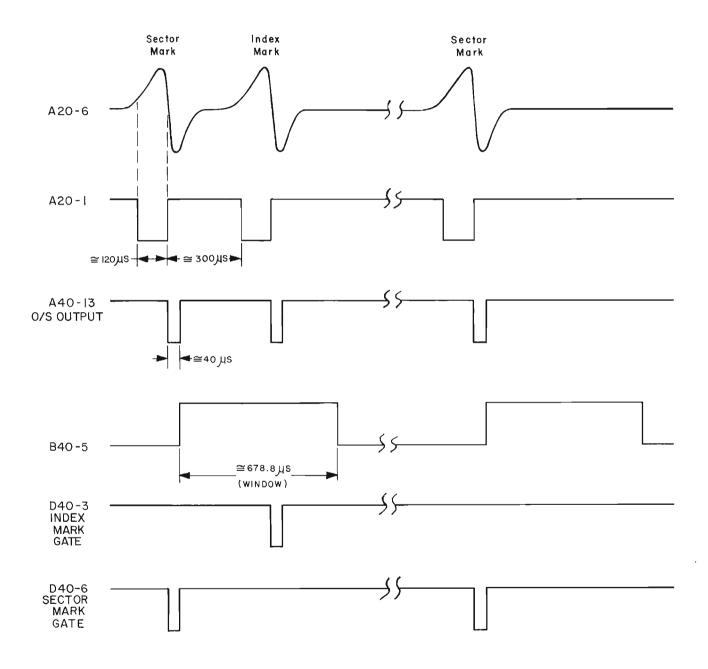

| 4-31   | Spindle Drive Generation                                             | 58  |

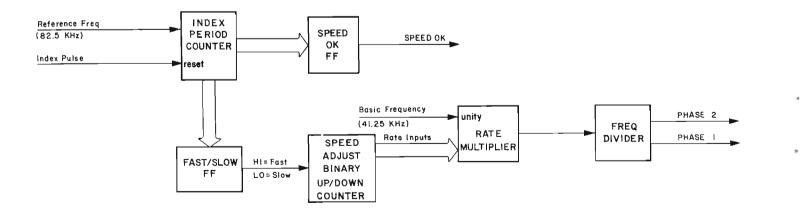

| 4-32   | Spindle Speed Control Block Diagram 4-                               | 60  |

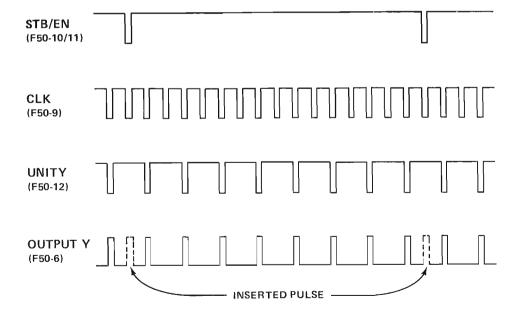

| 4-33   | Rate Multiplier Signals                                              |     |

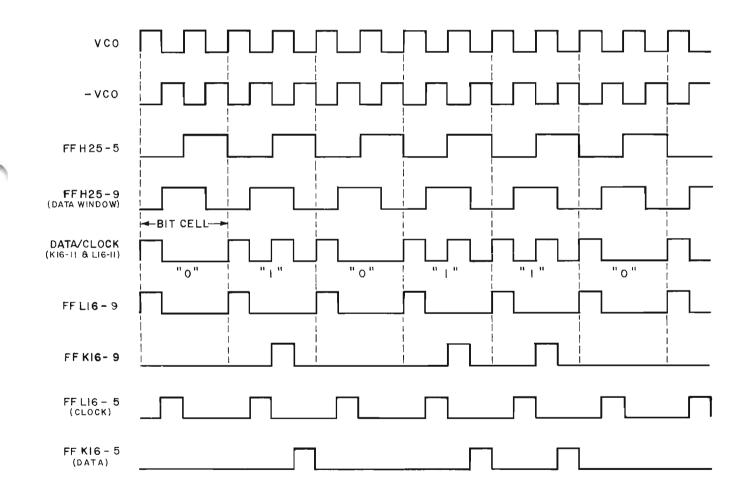

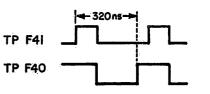

| 4-34   | VFO Data Separation                                                  | 71  |

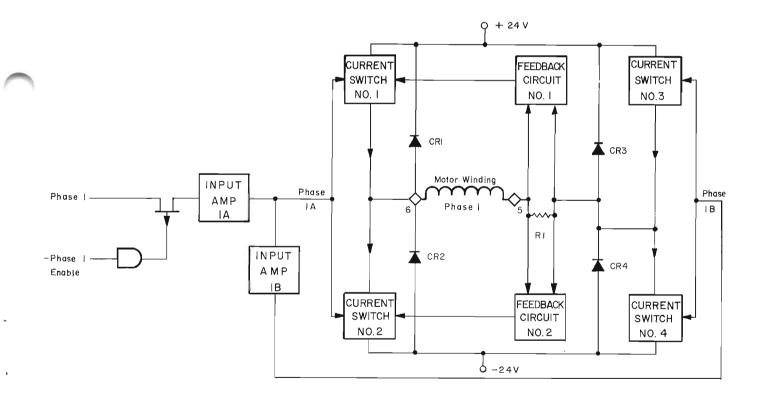

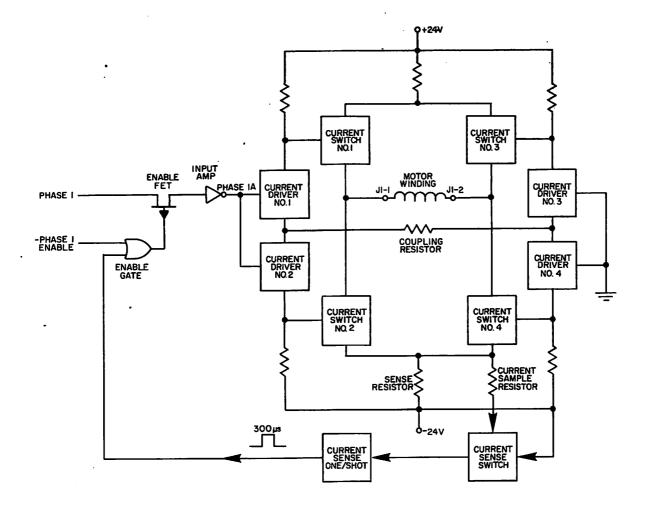

| 4-35   | Spindle Motor Phase I Driver 4-                                      | 73  |

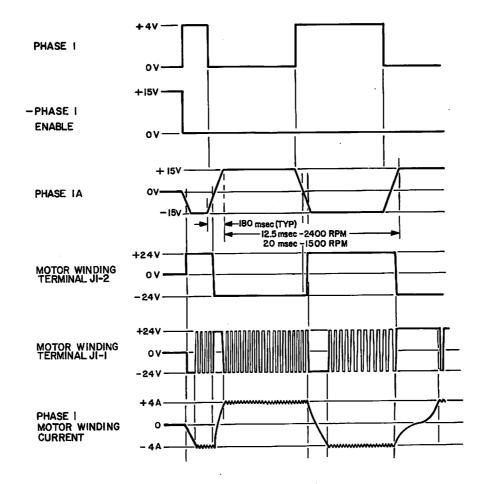

| 4-36   | Spindle Driver Waveforms                                             | 75  |

| 4-37   | Head Positioner Driver Block Diagram 4-                              | 77  |

| 5-1    | Location of Assemblies                                               | 4   |

| 5-2    | Card Cage PCB Locations                                              | 4   |

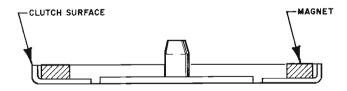

| 5-3    | Clutch Surface and Magnet                                            | 6   |

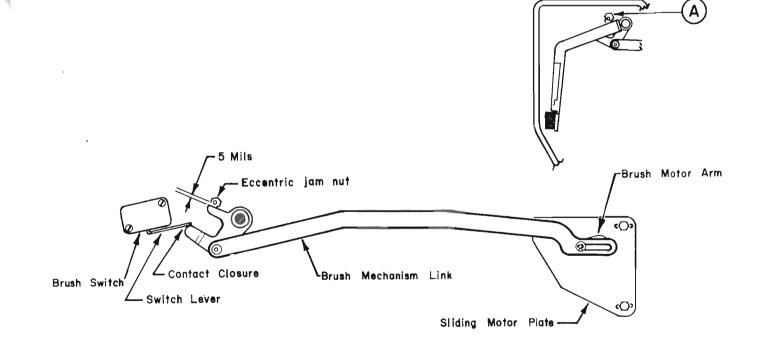

| 5-4    | Brush Mechanism Adjustments                                          | 11  |

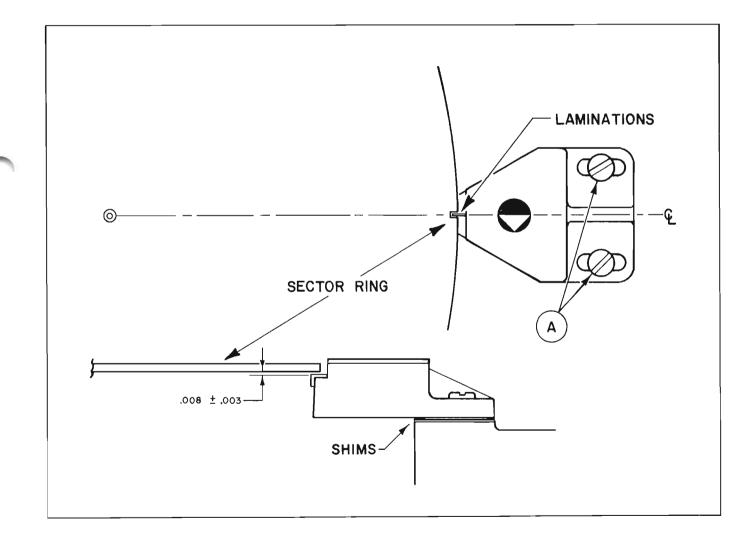

| 5-5    | Lower Index Transducer Adjustment 5-                                 | 13  |

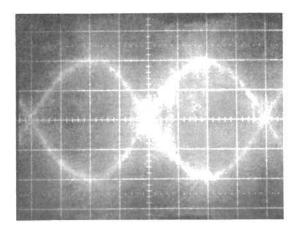

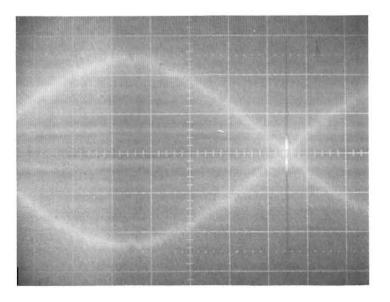

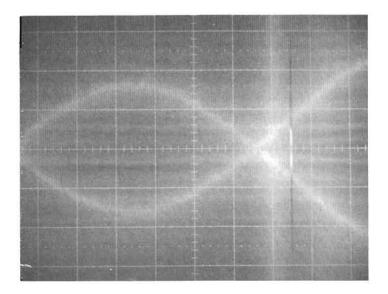

| 5-6    | 100 TPI Head Properly Aligned 5-                                     | 16  |

| 5-7    | 200 TPI Head Properly Aligned 5-                                     | 16  |

| 5-8    | 200 TPI Head Misaligned                                              | 16  |

| 5-9    | Head Adjustment                                                      | 18  |

| 5-10   | Head Adjustment - Lower Set:                                         | 18  |

| 5-11   | oppor indon reandators indonenti i i i i i i i i i i i i i i i i i i | 20  |

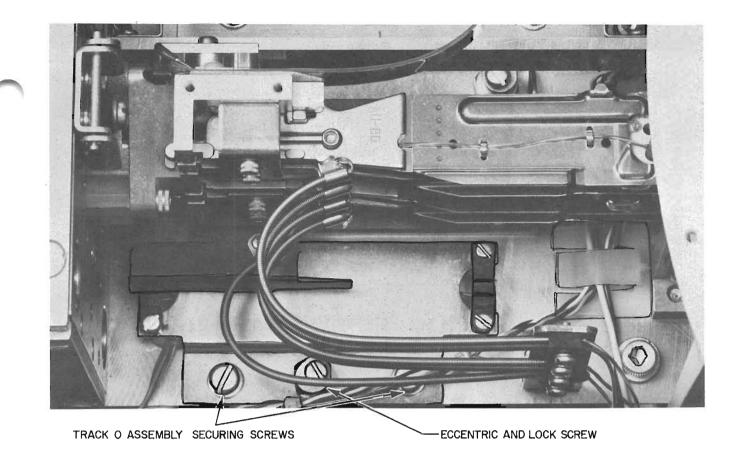

| 5-12   | Index to Data Burst Waveform 5-                                      | ·20 |

| 5-13   | fruch o bender hajubakene                                            | 23  |

| 5-14   |                                                                      | 23  |

| 5-15   |                                                                      | 24  |

| 5-16   |                                                                      | 24  |

| 5-17   | Front Panel Retaining Screw Access 5-                                | 27  |

×.

£

1

-

# LIST OF TABLES

| Table |                                   |       |

|-------|-----------------------------------|-------|

| 1-1   | Specifications                    | 1 - 4 |

| 31    | I/O Connector Part Numbers        | 3-2   |

| 3-2   | Interface Pin Assignments         | 3-3   |

| 3-3   | Format Requirements for Model 44B | 3-16  |

| 3-4   | Maximum System Tolerances         | 3-17  |

| 5-1   | Preventive Maintenance Action     | 5-5   |

| 5-2   | Adjustment Requirements           | 5-9   |

| 6-1   | Options                           | 6-1   |

| 6-2   | Accessories                       | 6-2   |

#### SECTION 1

#### GENERAL DESCRIPTION AND SPECIFICATIONS

## 1.1 OPERATIONAL CHARACTERISTICS

The Diablo Model 44B Disk Drive, shown in Figure 1-1, provides up to 100 megabits of on-line random access storage, and unlimited off-line storage for small, general purpose digital computers. Its design incorporates features which ensure a high degree of flexibility, reliability, speed of access, and data integrity. It uses both a fixed disk and a removable Type 5440 top loading disk cartridge. A capacity of up to 100 megabits is provided at a data transfer rate of 2.5 Mbits/second, a recording density of 2200 bitsper-inch (bpi), and a lateral track density of 200 tracks-per-inch (tpi).

Options and accessories which are available for the Model 44B are described in Section 6.

The Model 44B consists of six functional groups:

- The Spindle Assembly rotates the recording disks, and provides ventilation for the drive.

- Four Read/Write Head Assemblies "write" data onto, or "read" data from, the two disks.

- The Head Positioner Assembly moves the read/write heads to the disk track locations commanded by the using system.

- Controls, Indicators, and Interlocks provide the means for front panel operation of the drive, and prevent improper operating sequences.

- The Electronics group accepts, processes, generates, and/or supplies the electrical signals necessary for the disk drive to perform its intended function.

- An Internal Power Supply converts AC line power to the several DC operating voltages required by the drive.

The spindle drive motor is mounted directly on the spindle shaft. Spindle speed is controlled electronically, and is independent of normal fluctuations in line voltage or frequency. An air blower for the ventilation system is also mounted on the spindle shaft. Disk contamination from outside sources is virtually eliminated by passing all air drawn into the unit through an absolute nobypass air filter. This filter retains 99.97% of all particles 0.3 microns or larger. Filtered air is then directed into both disk areas and through them to cool the electronics areas before exhausting at the rear of the machine. In addition, each disk surface is swept with a cleaning brush each time the drive is switched from the Load mode to the Run mode.

The head positioning system's case is designed to contain the strong magnetic field of its ceramic magnets and drive coil. This reduces stray magnetic flux at the read/write heads to a negligible level, eliminating a common cause of disk

.

Figure 1-1. DIABLO SYSTEMS, INC. MODEL 44B DISK DRIVE

system data error. The thermal characteristics of the drive are designed to minimize head-to-track error due to ambient temperature, rate of change of ambient temperature, start-up transients, cold packs placed on warm drives, etc. By minimizing head-to-track alignment error, highly reliable data transfer is achieved.

Head loading is accomplished gently, with no head-to-disk contact, by a ramp load mechanism. The heads load automatically as they arrive over the disk from the retract position. In the event of power failure, the heads immediately retract and unload, providing protection for heads, disks, and data. A system of interlocks guards against operator error which could otherwise damage the heads and disk surfaces.

## 1.2 GENERAL SPECIFICATIONS

General specifications for the Model 44B Disk Drive are listed in Table 1-1.

1.3 RELATED DOCUMENTS

Several documents which pertain to maintenance of the Model 44B Disk Drive are listed below. Those marked with an asterisk (\*) are not available at the time of this writing but will be released in the near future. In addition to these publications, Field Service Aid bulletins are published as necessary to inform the user of design changes, new service procedures, etc.

Model 44B Disk Drive Maintenance Manual Publication No. 81903

\* Model 44B Disk Drive Parts Catalog Publication No. 81904

Model 44B Disk Drive Parts Price List Publication No. CS503-08

Maintenance and Special Items Pricing Publication No. CS500-04

Alignment Cartridges User's Manual Publications No. 81619

# TABLE 1-1

# SPECIFICATIONS

Specifications for 100 TPI are the same as for 200 TPI except where noted.

| PARAMETER                      | 200 TPI                                                                                                 | 100 TPI (Optional)                                                        |

|--------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Storage Medium:                |                                                                                                         |                                                                           |

| Туре                           | Type 5440 cartridge and a fixed disk.                                                                   |                                                                           |

| Diameter                       | 14 inches (35.56 cm)<br>200 tracks per inch (25.4 mm)<br>Double frequency<br>1632 (400 plus 8 spares on | 100 tracks per inch (25.4 mm)<br>                                         |

| Cylinders                      | each surface on each disk.)<br>408 (4 tracks per cylinder,                                              | each surface on each disk.)<br>204 (4 tracks per cylinder,<br>2 per disk) |

| Conscitu Dita. *               | 2 per disk)                                                                                             | z per arsk)                                                               |

| Capacity, Bits: * Per Drive    | 100,000,000<br>50,000,000<br>2200<br>250,000                                                            | 50,000,000<br>25,000,000<br>                                              |

| Per Track                      | 62,500                                                                                                  |                                                                           |

| Access Time:<br>Track-to-Track | 8 ms<br>38 ms                                                                                           | 10 ms                                                                     |

| Full Stroke                    | 70 ms                                                                                                   | **                                                                        |

| Disk Rotation:                 | 2400 rpm <u>+</u> 0.2%<br>12.5 ms                                                                       | **                                                                        |

| Bit Transfer Rate              | 2500 kHz                                                                                                | **                                                                        |

| Power Requirement              | 100, 120, 220 or<br>240 VAC, 50 or 60 Hz                                                                |                                                                           |

| Environment (operating):       |                                                                                                         |                                                                           |

| Temperature                    |                                                                                                         |                                                                           |

| Temp Change Rate               | -                                                                                                       |                                                                           |

| Relative Humidity              | 20% to 80%                                                                                              |                                                                           |

| Maximum Altitude               | 10,000 ft (3048 m)                                                                                      |                                                                           |

| Temperature                    | -40 <sup>0</sup> F (C) to 140 <sup>0</sup> F (60 <sup>0</sup> C)                                        |                                                                           |

| Relative Humidity              |                                                                                                         |                                                                           |

| Physical:                      |                                                                                                         | £                                                                         |

| Width                          | 17-1/4 inches (43.815 cm)                                                                               |                                                                           |

| Height                         | 10-5/16 inches (26.19 cm)                                                                               |                                                                           |

| Depth                          | (See Figure 2-1)                                                                                        |                                                                           |

| Disk Drive                     | 113 lbs (51.36 kg)                                                                                      |                                                                           |

| Rack Mounting Hardware         | 12 lbs (5.45 kg)                                                                                        |                                                                           |

- \* The capacity figures shown are nominal. Actual capacity will depend on formatting and data check methods used.

- \*\* See 1500 RPM option in Section 6 for variations.

#### SECTION 2

#### INSTALLATION AND OPERATION

# 2.1 INSTALLATION

# 2.1.1 Dimensions

Figure 2-1 shows the basic dimensions of the Model 44B Disk Drive, including its rack slides for mounting in a standard 19-inch (48.26 cm) rack. The standard Model 44B Disk Drive is furnished with rack slides and a cable carrier kit to properly position the I/O cable. Dimensions pertinent to rack mounting the drive are shown in Figure 2-4 and Figure 2-5.

A desk top version of the Model 44B is available also.

2.1.2 Unpacking/Packing

2.1.2.1 Unpacking Procedure

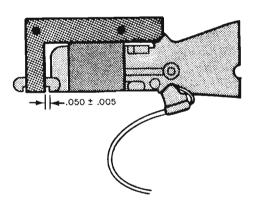

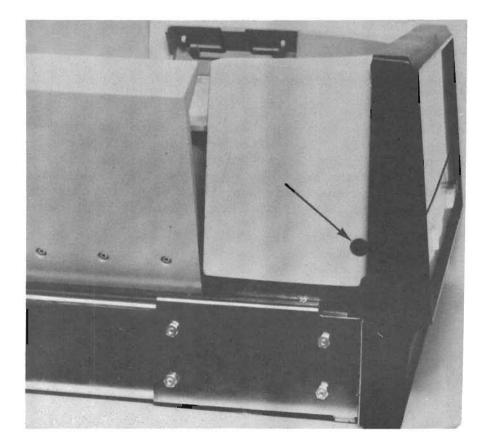

The unpacking procedure for the disk drive is readily apparent by referring to the shipping container assembly drawing shown in Figure 2-3. When unpacking the disk drive, the packing materials should be retained for possible later use. Before initial operation of the disk drive, the head positioner shipping clamp, shown in Figure 2-2, must be removed.

2.1.2.2 Packing Procedure

1. Install head positioner shipping clamp inside disk drive, as shown in Figure 2-2.

Refer to Figure 2-3, in the following sequence:

- 2. Cover disk drive with plastic bag (Item 1).

- 3. Set disk drive in opened inner container (Item 2).

- Fold inner container around disk drive, place rack slides\* (Item 3) on top of inner container, and secure with banding straps (Item 4).

- 5. Place end pads (Item 5) in outer container (Item 6) and fold top flaps outward.

- 6. Slide inner container with disk drive down into end caps.

- 7. Place cable carrier assembly\* (Item 7) in open space between inner and outer containers.

- 8. Fold end cap flaps and outer container flaps inward, and seal outer container securely with tape.

- \* When disk drive is being shipped for repair, <u>do not</u> include rack slides or cable carrier.

Figure 2-1. MODEL 44B BASIC DIMENSIONS

Figure 2-2. HEAD POSITIONER SHIPPING CLAMP

Figure 2-3. SHIPPING CONTAINER ASSEMBLY

# 2.1.3 Rack Mount Installation

The Model 44B may be installed in a standard 19-inch (48.26 cm) rack with 27-1/2 to 28-5/8 inch (69.85 to 72.71 cm) rail spacing as follows:

- 1. Install the two slides in the rack, with hole alignment as shown in Figure 2-4. Adjust the rear mounting bracket on each slide as necessary to fit the rack rails. Secure each mounting bracket to the rail with four(4) screws.

- 2. Install the I/O Cable Carrier Kit on the left rear rail as described in Section 2.1.4.

- 3. Extend each slide out until it stops. Locate the intermediate stop under the slide center, press it in and continue to extend the slide to its maximum extension.

- 4. Position the unit on the fully extended slides.

## CAUTION

The Model 44B weighs approximately 113 pounds (51.36 kg). Make sure the rack, if free standing, has enough counterweight to prevent it from tipping forward when the unit is placed on the slides.

- 5. Secure the unit to the slides with two screws on each side, as shown on the bottom unit in Figure 2-4.

- 6. Adjust the I/O cable in the cable carrier to provide the necessary length of cable from the end of the carrier to the I/O connector on the drive. Connect the I/O cable to the drive.

- Slide the unit fully into the rack, while checking for proper operation of the I/O cable carrier. Adjust the latch plate on each slide as necessary for proper operation of the drawer latches.

2.1.4 Cable Carrier Installation

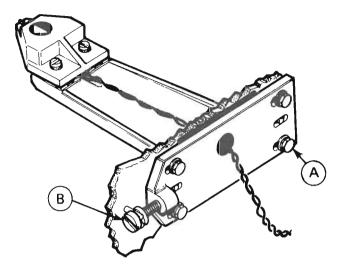

Refer to Figure 2-5.

- Beginning at the disk drive end of the I/O cable, fold the cable as shown in Figure 2-5(1), using one section of the cable carrier as a guide for the distance between folds. Mark a line on the cable at each fold, for later reference.

- 2. Install the Cable Carrier Mounting Bracket on the left rear rail of the rack, as shown in Figure 2-5(2).

- Install section A of the cable carrier on the mounting bracket, as shown in Figure 2-5(3). Use two #10 flat washers and one #6-32 screw on each pivot stud, as shown.

NOTE: CENTIMETERS GIVEN IN ( ).

Figure 2-4. MODEL 44B RACK MOUNT POSITIONS

Figure 2-5. I/O CABLE CARRIER ASSEMBLY

- Using the fold marks for reference, position the I/O cable on Section A of the carrier while installing Section B as shown in Figure 2-5(4).

- Position the cable on section B and install Section C as shown in Figure 2-5(5).

- 6. Slide the cable down into the slot at the end of Section C as shown in the complete view of the carrier assembly.

- 7. Adjust the position of the cable in the carrier to ensure that an adequate length of cable will be available to reach from the end of Section C to the I/O connector on the drive.

- 8. Clamp the I/O cable to the carrier mounting bracket, using the metal cable clamp, as shown in Figure 2-5(6).

- 9. Fold and extend the cable carrier assembly several times to verify proper operation.

- 2.2 OPERATING INSTRUCTIONS

- 2.2.1 Operating Precautions

- 2.2.1.1 Disk Drive Operation

To obtain the best performance and reliability from the Model 44B, and to prevent equipment damage, the following precautions should be observed:

- Do not connect or disconnect the I/O cables while power is turned on.

- 2. Keep the equipment drawer closed to prevent airborne contamination. Either a disk cartridge or the dust cover should be in place in the bowl at all times.

- 3. The drive should be left in the RUN mode whenever possible so that clean filtered air will be supplied to the interior of the machine.

- 4. A sustained audible tinging or scratching sound may be caused by head-to-disk contact. If it persists, discontinue machine operation and investigate the cause.

- 5. Do not force or attempt to override any interlock. Interlocks are safety devices, included to prevent injury, equipment damage, and loss of data.

- 2.2.1.2 Cartridge Handling and Storage

The following precautions should be observed when handling or storing disk cartridges:

1. Cartridges are magnetically recorded records. They MUST be kept away from strong magnetic fields, such as large rotating electrical machines, high-current bus bars or cables, welding equipment, etc.

- 2. The cartridge dust cover should be in good condition and kept on the cartridge while it is out of the disk drive. This ensures a positive dust seal and immobilizes the disk inside.

- 3. Cartridges may be stored on edge or flat. When stored flat, avoid stacking more than five(5) high. Cartridges should never be stored in direct sunlight, or in very dusty or dirty areas.

- 4. Any Disk Cartridge that has been dropped should be inspected by the disk cartridge manufacturer before attempting to use it.

- 5. Refer to cartridge manufacturer's instructions for maintenance and cleaning procedures.

# 2.2.1.3 Head Crash

Head Crash, in most cases, is easily preventable by observing the foregoing precautions. A head crash occurs when a R/W head contacts the disk. This is usually audible. The vast majority of head crashes are due to contamination caused by careless handling and careless operation of the disk drive and disk cartridges, and <u>failure to change the air filter at the</u> <u>recommended intervals</u>. If a head crash occurs, the crashed head and the disk must both be replaced, and the cause of the head crash must be eliminated.

# 2.2.2 Controls and Indicators

The Model 44B Disk Drive has two front panel controls and four front panel indicators. These are shown in Figure 2-6 and described in the paragraphs which follow. For service convenience, an AC Power ON-OFF switch is located at the rear of the disk drive.

# 2.2.2.1 LOAD/RUN Switch

The LOAD/RUN Switch is a two-position rocker switch that provides a means for starting and stopping the spindle. Cartridges may be removed and inserted when the switch is in the LOAD position and the LOAD light is on. With a cartridge inserted, and the cartridge clamps closed, switching to the RUN position starts the disk drive and brings the disk up to its normal operating speed in about 60 seconds. When the switch is moved to the LOAD position, the disk decelerates to a stop in about 15 seconds, after which the LOAD light turns on.

# NOTE: This switch does not control power to the drive.

# 2.2.2.2 LOAD Indicator

The LOAD Indicator is a white indicator light which shows that cartridges can be loaded or unloaded. The light is on only when the LOAD/RUN switch is in the LOAD position, the disk is not rotating, the brushes are retracted, and power is on.

# 2.2.2.3 READY Indicator

The READY Indicator is a yellow indicator light which shows that the drive has completed its start-up sequence. The light comes on when the disk is rotating at its correct speed, heads are in position and no other conditions are present which would prevent a Seek, Read, or Write command from being executed.

5

Figure 2-6. FRONT PANEL, MODEL 44B DISK DRIVE

The light remains on through a Seek, Read, or Write operation. The light extinguishes when the LOAD/RUN switch is set in the LOAD position.

# 2.2.2.4 CHECK Indicator

The CHECK Indicator is an orange indicator light which shows that due to some abnormal condition the disk drive may be incapable of writing. When the abnormal condition no longer exists, the disk drive is reset by moving the LOAD/RUN switch to LOAD position and then back to RUN.

# 2.2.2.5 PROTECT Switch/Indicator

The PROTECT Switch/Indicator is a red back-lighted momentary-contact push-button switch. In units with the internal Write Protect option switches set to activate the Write Protect feature, the PROTECT switch glows and writing is inhibited whenever one of the following steps is performed.

- 1. Initial turn-on of drive.

- 2. LOAD/RUN switch changed from RUN to LOAD. (Condition remains when switch is returned from LOAD to RUN.)

- 3. Using system sends Write Protect command to drive.

To allow writing, Write Protect is turned off by the operator depressing the PROTECT switch.

In units where the Write Protect feature has been deactivated for one or both disks by the internal Write Protect option switches, the PROTECT indicator continues to function as described above; however, disks with Write Protect so deactivated are NOT write protected.

#### 2.2.3 Interlocks

The cartridge clamps cannot be operated while the disks are rotating, the heads or brushes are over the disk surface, or equipment power is off. When all of these conditions are satisfied, the LOAD indicator is illuminated to indicate that the cartridge clamps can be opened.

The spindle motor will not rotate if the cartridge dust cover is not installed, or if the cartridge clamps are open. Although the drive will operate with the equipment drawer open, for safety and other reasons it is recommended that the drawer be kept closed whenever practical to do so.

# 2.2.4 Typical Operating Procedures

Initial Checkout

NOTE: Prior to initial checkout, and alignment if needed, completely unpack the Model 44B, and remove the shipping clamp shown in Figure 2-2. If not installed in a rack or cabinet, place the unit on a stable flat surface. Connect the power cord and I/O cables. Set the drive's front panel LOAD/RUN switch to the LOAD position. Apply AC power. Verify that the PROTECT indicator is on. Verify that the LOAD indicator comes on within 60 seconds after applying power.

- 1. If rack mounted, open the equipment drawer by pulling out on the door handle as shown in Figure 2-7.

- 2. Open the two cartridge clamps located on each side of the spindle bowl.

- 3. Refer to Figure 2-8. Slide the tab on the cartridge handle to the left, raise the handle, and lift the cartridge clear of its dust cover lower half.

- 4. Place the opened cartridge over the spindle hub oriented so that its handle will fold toward the rear. Lower the cartridge into place with a gentle back and forth rotary motion to ensure that its lower notches engage the alignment tabs inside the bowl. Lower the cartridge as far as it will go, then lower its handle to lock it in place.

- 5. Place the cartridge dust cover upside down inside the drive's cartridge bowl on top of the cartridge just installed, and close the two cartridge clamps.

- 6. Slide the drive back into its compartment until the latches engage the slides.

- 7. Set the LOAD/RUN switch to RUN. Verify that the front panel LOAD light goes out.

- 8. Allow the equipment about 60 seconds to complete its start-up cycle. Verify that the READY light comes on at the completion of this cycle.

- NOTE: With the Write Protect feature active for one or both disks, the PROTECT light must be depressed to extinguish the light and allow 'writing' on the protected disk or disks.

Further checkout or operation as appropriate to the using system may now be performed.

NOTE: After installation of the disk drive, verify alignment of the R/W heads as described in Section 5 of the Maintenance Manual.

<u>н</u>

When disk operation is complete, or when it is desired to exchange cartridges, the following steps are to be followed:

- 1. Set the LOAD/RUN switch to LOAD. Wait for the LOAD light to come on (about 15 seconds).

- 2. For rack mounted drives, open the equipment drawer (Figure 2-7), and slide the drive out to its first stop.

Figure 2-7. OPENING THE EQUIPMENT DRAWER

Ð

Figure 2-8. OPENING THE TYPE 5440 DISK CARTRIDGE

- 3. Open the cartridge clamps and lift off the cartridge dust cover.

- 4. Slide the tab on the cartridge handle to the left, raise the handle to disengage the cartridge from the spindle, and lift the cartridge clear of the drive.

- 5. Invert the dust cover, lower the cartridge into it, and fold the handle down all the way to engage the cover magnets and release the tab. The cartridge is now ready for storage.

- 6. Install another cartridge and dust cover, close the equipment drawer, and place the drive in the RUN mode or completely deenergize the system.

- NOTE: If no cartridge is to be installed at this time, cover the spindle bowl area with a plastic sheet or other lint-free cover.

#### SECTION 3

#### INTERFACE INFORMATION

#### 3.1 AC POWER REQUIREMENTS

The Model 44B Disk Drive is designed to operate over an AC frequency range of 49 to 61 Hertz, single phase.

A tap changing PCB, located in the AC power socket assembly can be positioned for nominal line voltages of 100, 120, 220 or 240 VAC. Line voltage should remain within +10% of the nominal value selected.

The AC power socket is a recessed three-pin socket with power, return and ground pins.

#### 3.2 SIGNAL INTERFACE

# 3.2.1 Interface Connector

The Model 44B Disk Drive has two interface connectors. Viewed from the rear of the drive, the right-most connector is considered to be the input connector, receiving input information from a controller or from another disk drive preceding it in a daisy chain system. The left-most connector is considered to be the output connector, providing circuit connection facilities for a succeeding disk drive in a daisy chain system. If this is the last drive in a daisy chain system, or the only drive in the system, the left-most connector receives the required terminator. Table 3-1 shows the part numbers for the I/O connectors and mating cable connectors.

## 3.2.2 Interface Pin Assignment Summary

Interface connector pin assignments are summarized in Table 3-2, and are defined in the following paragraphs.

#### 3.2.2.1 Input Lines

The following input lines are found on the standard Model 44B Disk Drive. Unless otherwise stated, the signals on control input lines must be held for the duration of the function controlled. Signal Levels are 0 volts for low (LO), and +3.5 volts for high (HI). As shown in Table 3-2, a signal title prefixed with a negative (-) symbol represents a signal that is active when in its LO state. A signal title prefixed with a positive (+) symbol represents a signal that is active when in its HI state.

#### Select Lines

The interface has four lines assigned to unit-select function, in order for the using system to select one particular drive in a system where more than one drive is used. Two switches on the Address Logic PCB are used to identify the drive as unit 1,2,3, or 4. The drive will then respond only to a unit select signal that appears on the corresponding unit select line. For example, if the switch settings identify a drive as unit #2, it will respond only to a select signal on the SELECT UNIT 2 input line. A LO signal selects the drive. All interface lines, except the Attention line, are inactive until a SELECT signal is applied to the proper select line. When LO, this line qualifies all of the drive's other interface lines.

|                             | Supplier   | Shell       | Pins      |

|-----------------------------|------------|-------------|-----------|

| Right I/O Box Connector -   | Diablo     | 10667-01    | 10583-01  |

|                             | Winchester | MRAC50PJ6   | 1024P     |

| Right I/O Cable Connector - | Diablo     | 10670-02    | 10525-13  |

|                             | Winchester | MRAC50SJTDH | 100-0927s |

| Left I/O Box Connector -    | Diablo     | 10667–02    | 10583-02  |

|                             | Winchester | MRAC50SJ6   | 1024s     |

| Left I/O Cable Connector -  | Diablo     | 10670-01    | 10525-12  |

|                             | Winchester | MRAC50PJTDH | 100-0917P |

Table 3-1. I/O Connector Part Numbers

# Table 3-2

# Interface Pin Assignments

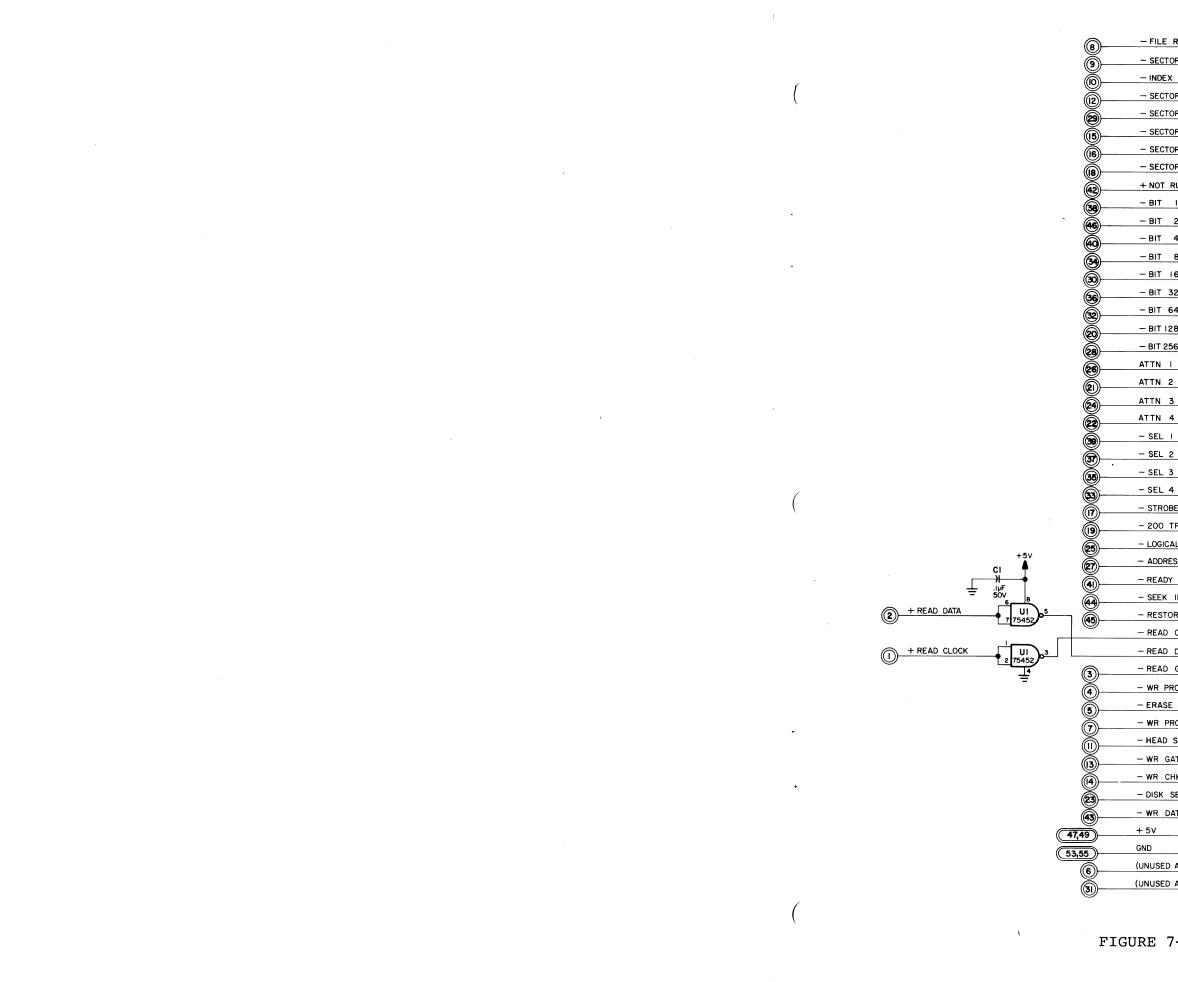

| Input Signal            | Pin | Output Signal              | Pin |

|-------------------------|-----|----------------------------|-----|

| -Select Unit 1          | L   | -File Ready                | U   |

| Unit 2                  | R   | -Ready to S/R/W            | F   |

| Unit 3                  | V   | -Address Acknowledge       | p   |

| Unit 4                  | Z   | -Logical Address Interlock | У   |

| Disk Select             | AA  | -Seek Incomplete           | u   |

| Head Select             | а   | -Index Mark                | Y   |

| -Cylinder Address Bit l | N   | -Write Check               | h   |

| Bit 2                   | S   | -Read Clock                | А   |

| Bit 4                   | J   | -Read Data                 | С   |

| Bit 8                   | х   | +Attention 1 **            | CC  |

| Bit 16                  | f   | +Attention 2 **            | DD  |

| Bit 32                  | Т   | +Attention 3 **            | EE  |

| Bit 64                  | . p | +Attention 4 **            | FF  |

| Bit 128                 | BB  | -200 TPI Line              | z   |

| Bit 256*                | m   | Write Protect Status       | Р   |

| -Strobe                 | t   | -Sector Mark               | W   |

| -Restore                | w   | -Sector Bit 1              | С   |

| -Write Gate             | e   | -Sector Bit 2              | j   |

| -Erase Gate             | K   | -Sector Bit 4              | k   |

| -Write Data & Clock     | В   | -Sector Bit 8              | n   |

| -Read Gate              | E   | -Sector Bit 16             | v   |

| -Write Protect Input    | Н   | +Not Run                   | D   |

|                         |     |                            |     |

|                         |     | Other Lines                |     |

|                         |     | +5V for terminator         | r   |

|                         |     | Ground                     | S   |

|                         |     | Ground                     | x   |

|                         |     | Ground                     | нн  |

|                         |     | Unused                     | м   |

|                         |     | Unused                     | d   |

\* Hold Cylinder Address Bit 256 at 0 volts on 100 tpi units.

\*\* -Attention option available (Option No. 490)

#### Disk Select

This line selects the disk to be used in a forthcoming operation. LO selects the removable cartridge disk; HI selects the fixed disk.

#### Head Select

This line selects the upper or lower head for use with the selected disk. LO selects the upper surface head; HI selects the lower surface head.

# Cylinder Address

These lines accept a 9-bit (8-bit for 100 tpi) binary absolute cylinder address. When strobed, their content is supplied to an internal address register to control head movement. These lines must be settled prior to application of the strobe signal, and should be held until the trailing edge of the strobe signal.

#### Strobe

This line is used to enable the track address and restore lines. Strobe should be applied only after the appropriate signal lines have settled, and must be held until at least the leading edge of the -ADDRESS ACKNOWLEDGE signal. Rise and fall times are to be compatible with commercially available DTL and TTL integrated circuits. The strobe pulse is LO.

## Restore

This line carries the "head positioner restore to 0" command. When this command has been completed, the heads are located over cylinder 0, the address registers have been set to address 0, and the Seek Incomplete condition is reset. The RESTORE line must have settled to +10% of its steady value prior to the application of the strobe signal. The restore pulse is LO.

# Write Gate

This line turns on write current in the selected head. The signal must be applied not more than 2 microseconds prior to writing the first flux transition, and held for the duration of the write operation. The write gate is LO for current on.

#### Erase Gate

This line, when LO, turns on erase current to the selected head. There is no built-in delay of erase current.

#### Write Data & Clock

This line accepts multiplexed data and clock pulses for double frequency or phase encoding type recording; one complete pulse for each recorded flux reversal. Pulses must have a minimum width of 100 nanoseconds. Leading edge must have a transition time of not more than 50 nanoseconds. This line is held at +3.5 volts when not writing. Write pulses swing from +3.5 volts to 0 volts. When LO, this line enables the READ CLOCK and READ DATA output lines. Write Protect Input

A LO signal on this line restores the write protect condition for either or both disks, depending on the settings of the write protect option switches. If both of the write protect option switches are set to ON, both disks will be restored to write protect simultaneously by a single pulse from the controller. The pulse to restore write protect must be at least 1 microsecond in duration.

3.2.2.2 Output Lines

File Ready

This line supplies a maintained LO level when all the following conditions are met:

Power on Cartridge loaded LOAD/RUN switch in RUN position Start-up cycle complete WRITE CHECK line HI FILE SELECT line LO

Ready to Seek, Read or Write (Ready to S/R/W)

A LO level on this line indicates that the disk drive is in the File Ready condition and is not in the process of executing a seek operation. Following a seek command to a valid address (other than the present address), or a restore command, the READY TO S/R/W line goes HI within 1 microsecond after detecting the leading edge of the -STROBE signal. The return of the READY TO S/R/W line to the LO state indicates that seek (or restore) operation has been completed, the heads are fully settled and the machine is ready to Seek, Read or Write to another address. This line does not change when the present cylinder is readdressed.

#### Address Acknowledge

A LO level on this line indicates that a valid command to move the heads (seek command) has been accepted, and the heads have begun to move. An -ADDRESS ACKNOWLEDGE signal (1.2 microsecond LO) is issued 500 nanoseconds after the leading edge of the Strobe, even if there is no change from the previous address. This signal will not be issued if a command to move to a track position greater than 407 (203 for 100 tpi drives) is received. In this case, execution of the command is supressed, and a -LOGICAL ADDRESS INTERLOCK signal is issued on another line.

Logical Address Interlock

A LO level on this line indicates that a track address greater than 407 (203 for 100 tpi drives) has been received, and that the command cannot be

executed. The seek command is suppressed. This signal, from a latch circuit in the output, resets with the next -ADDRESS ACKNOWLEDGE signal or RESTORE command.

# Seek Incomplete

A LO level on this line indicates that a malfunction has caused an incomplete seek operation. This signal level will be maintained until a RESTORE command is received and executed by the disk drive or until the Load/Run Switch is switched to LOAD and then back to RUN.

# Index Mark

This line supplies one LO, 40 microsecond pulse per disk revolution, as a mechanical index mark on the hub of the selected disk passes its transducer.

# Write Check

When the drive is selected, a LO level on this line indicates that one or more of the following conditions exist:

- 1. Write current without LO WRITE GATE.

- 2. WRITE GATE LO without write current.

- 3. Write and select of multiple heads, or an open R/W coil.

- 4. Erase current without LO ERASE GATE.

- 5. ERASE GATE LO without erase current.

When WRITE CHECK is LO, execution of all external commands is suppressed. The operator may reset Write Check by moving the LOAD/RUN switch to LOAD and then back to RUN.

# Read Clock

This line supplies clock pulses which have been separated from the data signals during reading. Pulse width is nominally 100 nanoseconds, +50 nanoseconds. The leading negative-going edge must be used for reference.

# Read Data

This is the output line for data signals which have been separated from clock signals during reading. Pulse width is nominally 100 nanoseconds, +50 nanoseconds. The leading negative-going edge must be used for reference.

# Attention Lines

A logical combination of output lines that informs the using system, by means of a LO signal, when the disk drive is ready, completes seek, fails to complete seek, accepts a seek command to the present address, or receives an invalid address. The ATTENTION line number and the SELECT line number correspond. 200 tpi Line

This line notifies the controller that the drive is a 200 tpi machine. The output is HI until the drive is selected and the heads are loaded, at which time it goes LO.

Write Protect Status

The signal level on this line provides an indication of the Write Protect Status. A LO level indicates that the disk drive's write capability is inhibited. The operator can change the status manually by depressing the momentary action PROTECT switch on the front panel, thereby enabling the disk drive's write capability.

#### Sector Mark

This line supplies one LO 40 microsecond pulse for each sector slot on the disk hub as it passes its transducer. The leading edge of the pulse must be used as reference.

## Sector Address

These five lines continuously define, in binary form, the sector address under the heads. This address is derived from one of two counters, determined by the DISK SELECT input line. Each counter is reset to zero by the leading edge of the SECTOR MARK following the index mark, and is advanced by the leading edge of subsequent SECTOR MARKS. The status of the sector address counter is valid if the read-out occurs at the trailing edge of the SECTOR MARK signal, or 3 to 5 microseconds after the leading edge of SECTOR MARK.

#### Not Run

This line informs the controller whether the drive is in the Run mode or the Load mode. NOT RUN is HI when the drive is in the Load mode, and LO when it is in the Run mode.

#### +5V for Terminator

This line supplies +5 volts to the terminator circuits. A terminator must be connected to the I/O output connector of a single drive or the last drive in a daisy chain configuration.

## 3.2.2.3 Output Line Drive Capability

An output driver circuit for the READ CLOCK and READ DATA lines is shown in Figure 3-1, for the standard configuration. All other lines are driven as shown in Figure 3-2.

#### 3.2.2.4 Input Gates

The Model 44B Disk Drives use an 8836 type NOR gate as the input circuit. This device has a higher input threshold in the low logic state than most commercially available DTL or TTL circuits, assuring a higher noise margin on all input lines. Input hysteresis of the 8836 gates further increases noise immunity. Low input current, even with no Vcc, prevents a Model 44B with power down from affecting other drives in a daisy chain system. In addition, the 8836 input circuit loads the signal transmission lines with

significantly less input current under operating conditions, causing less local reflections on the line.

The input of the 8836 circuit has to be pulled up in the high logic state. For this reason, it cannot be driven by an open collector driver stage without collector resistance. This collector resistance is in the terminator which must be installed on the last disk drive in a daisy chain, or on any drive used alone. Figure 3-3 shows the input circuit used in the Model 44B.

#### 3.3 INPUT/OUTPUT CABLES

Two types of cable may be considered for use with the Model 44B. One type is the conventional round cable consisting of twisted pairs for each signal, with a PVC jacket. The other type is a PVC flat cable with a flexible ground plane.

3.3.1 Flat Cable

Because of the uniform transfer characteristics and production efficiency, a flat cable type is recommended. The flat cable, ordered by option number from Diablo, has the following physical characteristics:

Number of conductors 50 Wire size 30 AWG solid Shield Flexible ground plane Insulation PVC

The characteristic wave impedance is 80 ohms, with the shield plane grounded on both ends.

3.3.2 Round Cable Twisted Pair

For those applications where, in spite of the drawbacks, a round cable is preferred, the type recommended is made of twisted pairs insulated with heat sealed overlapping MILENE tapes. Physical characteristics of round cables are:

Number of twisted pairs 50 Wire size 28 (7/36) AWG (4.94mm) Nominal OD of .023" (.584mm) insulated wire Nominal OD of .370" (9.398mm) PVC jacket UL rating Style No. 2384

The characteristic wave impedance of one single twisted pair is approximately 85 Ohms. If all ground leads of the twisted pairs are grounded on both ends, the wave impedance drops to approximately 45 Ohms, which results in excessive current from the drive circuits. Individually shielded twisted pairs cable is not recommended.

Figure 3-4 shows one practical method of dressing the twisted pair wires at the cable end.

• -

Figure 3-4. INTERFACE CONNECTOR ASSEMBLY

#### 3.3.3 Cable Lengths

Maximum recommended cable length between the controller and the first disk drive is 15 feet (4.57m). Cables between disk drives in a daisy chain configuration should not normally exceed 12 feet (3.65m) in length, although one 15-foot (4.57m) cable between the second and third drive would be permitted if necessary to use more than one cabinet. The total cable run in a daisy chain configuration should not exceed 50 feet (15.24m).

# 3.4 TERMINATING RESISTORS

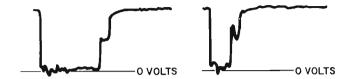

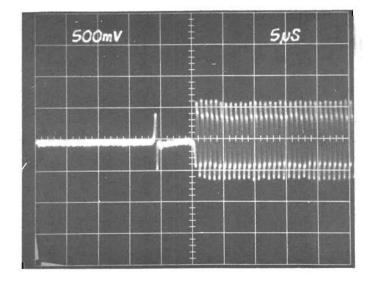

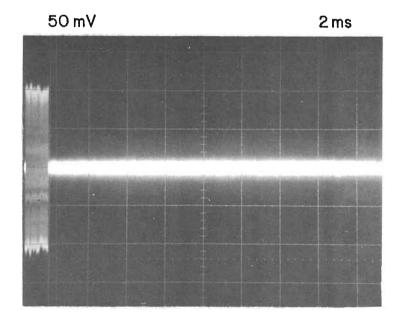

The signal lines carrying pulses transmitted by any disk drive will cause reflection on both ends of the cable if the cable is not properly terminated. Figure 3-5 shows two waveshapes taken on the terminated end of a cable when the other end was left unterminated. The negative-going leading edge is not affected significantly, and can be used as an input to logic circuits if properly handled. The trailing edge, however, is determined by the time duration of the pulse, and the length of the cable. Those lines carrying signals of short duration should always be terminated on both ends. Satisfactory system performance cannot be achieved, even with relatively short cable lengths, if the signal lines are not properly terminated on both ends.

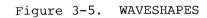

A typical circuit for termination of the cables is shown in Figure 3-6. Cable terminators matched to Diablo-supplied flat cable are available.

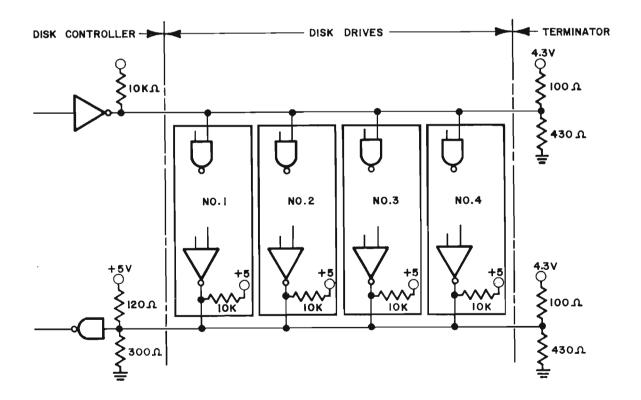

# 3.5 DOUBLE FREQUENCY RECORDING

In double frequency recording, a clock bit is recorded at the beginning of each bit cell time. Recording a clock bit in each bit cell time results in the read-back data being self-clocking.

To write a series of logical zeros, only the clock bit is recorded at the beginning of each bit cell time. To record a one bit, a flux reversal, or bit, is inserted in the center of a bit cell time. To write a series of ones, a clock bit and a data bit will be recorded in each bit cell time. It then can be seen that the frequency of bits for a series of ones is twice the frequency for a series of zeros. Hence the method is called Double Frequency Recording.

Figure 3-7 shows the bit and time relationship for recording and reading back a data bit series of 0-0-0-1-0-1-1-1. Nominal pulse width for the system is 100 nanoseconds.

Multiplexed data and clock pulses are sent to the drive on one line; each pulse received on the line results in one current and flux reversal. The data and clock pulses read from the disk are sent to the controller on separate interface lines.

# 3.6 DISK FORMAT

Prior to consideration of the disk format information in this paragraph, the reader should become familiar with the basic functioning of the disk drive, as described in Section 4.

Figure 3-6. DAISY CHAIN AND TERMINATOR

Figure 3-7. DOUBLE FREQUENCY RECORDING

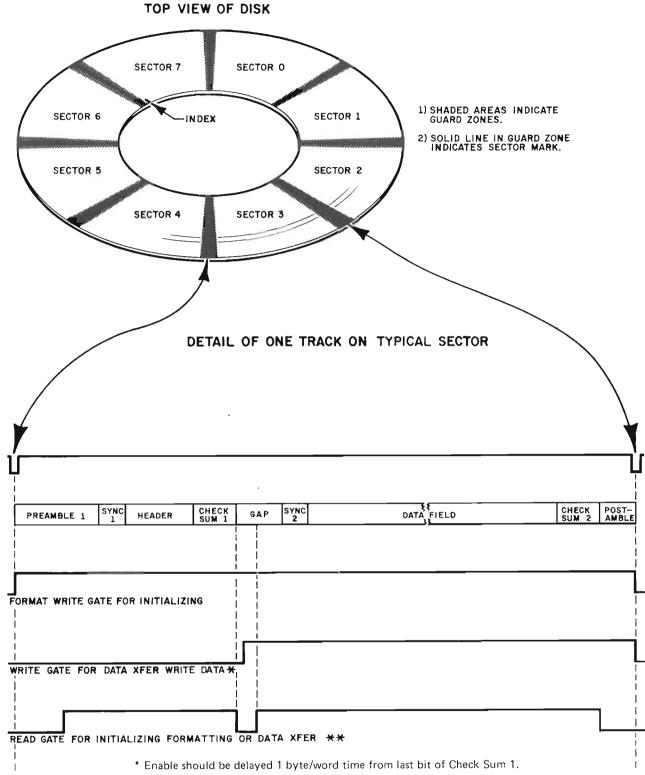

Each track on the disk is divided into a number of sectors of equal length, as shown in Figure 3-8. This is accomplished by means of slots on the disk hub, or electronically in the using system. The time between index marks is equal to the time of one disk revolution. This is nominally 25ms (40ms for 1500 rpm units). The time duration of each sector is the time between index marks divided by the number of sectors. If the disk rotation speed varies, the sector time varies by the same percentage. The spindle motor speed tolerance is +.2%; consequently, it can cause the sector time to vary by this amount. Other tolerance factors for which allowances must be made in disk formatting include physical separation of the erase and write coils, variation in the spacing of sector slots, alignment of the index transducers, sector jitter, alignment cartridge variation, write clock frequency, read amplifier recovery time, and variations in the transducers and their associated circuitry.

Formatting of the disk is the organized placement of data zones and guard zones in each sector, and the placement of clock pulses and/or data pulses within these zones. The data zones are those areas within each sector where data is to be recorded or read. To provide disk interchangeability and reliable read recovery of data, these data zones must contain a constant number of data cells, even in the presence of disk speed variation and other tolerances described above. The guard zones are variable in length, and ensure a constant number of data cells in each data zone by absorbing variations in sector time.

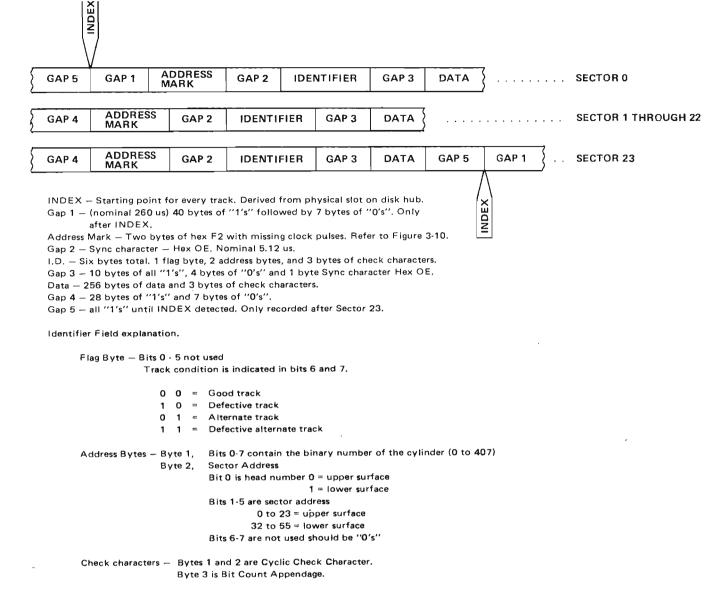

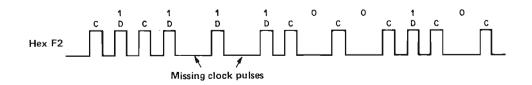

Each guard zone is a series of recorded clock pulses. The guard zone is recorded at the beginning and ending of each data zone, and is normally defined as a preamble (when located at the beginning of the data zone) and as a postamble (when located at the end of the data zone). The length of each guard zone must be adequate to allow for a reliable reading of each data zone even under worst case conditions of tolerances. Each data zone typically contains sychronizing, header, data, and check information. A guard zone and a data zone are defined as a sector, and typically are recorded by a combination of hardware and software control. When sector slots on the disk hub are used, a sector mark format method is commonly employed. Sector mark formatting is explained in paragraph 3.6.1. When only the index slot is on the disk hub, it is common to use address mark format. The address mark is a unique recorded pattern on the disk which is detected by the R/W heads. It serves the same function as the sector slots. Address mark format is explained in paragraph 3.6.2.

#### 3.6.1 Sector Mark Format

A typical sector format is shown in Figure 3-8 for an eight-sector disk. For any number of sectors, the amount of available data field in each sector can be determined by reference to Table 3-3.

Table 3-4 shows nominal values of typical system tolerances. The format shown in Figure 3-8, using the time per field shown in Table 3-3, provides a reasonable margin of allowance for these variations.

The fields shown in Figure 3-8 are described as follows:

PREAMBLE - allows for differences in index transducers, alignment cartridge differences, and read amplifier recovery time. There is an overlap of these tolerances within system considerations. The Preamble is generally filled with hexadecimal 00 characters.

\*\* Read gate should be enabled ½ way through the Preamble area. This insures reading a zero field for data separator synchronization.

Figure 3-8. TYPICAL SECTOR FORMAT

#### TABLE 3-3.

# FORMAT REQUIREMENTS FOR MODEL 44B

| [                     | 2400 RPM                   |                     | 1500 RPM                      |                      |

|-----------------------|----------------------------|---------------------|-------------------------------|----------------------|

|                       | usec                       | Bytes               | usec                          | Bytes                |

| Preamble (Note 1 & 4) | 19.2                       | 6                   | 30.72                         | 6                    |

| -(Note 2 & 4)         | 51.2                       | 16                  | 81.92                         | 16                   |

| Sync                  | 6.4                        | 2                   | 10.24                         | 2                    |

| Header                | 6.4                        | 2                   | 10.24                         | 2                    |

| Header Check Sum      | 6.4                        | 2                   | 10.24                         | 2                    |

| Gap (Note 3)          | 3.2                        | 1                   | 5.12                          | 1                    |

| Sync                  | 6.4                        | 2                   | 10.24                         | 2                    |

| Data Field (Note 4)   | $\mathtt{T}_{\mathrm{DF}}$ | <sup>T</sup> DF/3.2 | $^{\mathrm{T}}_{\mathrm{DF}}$ | <sup>T</sup> DF/5.12 |

| Data Check Sum        | 6.4                        | 2                   | 10.24                         | 2                    |

| Postamble (Note 4)    | . 6.4                      | 2                   | 10.24                         | 2                    |

| Sector Time           | Tsector                    |                     | <sup>T</sup> sector           |                      |

$$T_{\text{sector}} = \left[ \frac{.998 \star (6) (10^7)}{R \cdot N} - S \right] \text{ usec}$$

S = Sector slot placement error from Table 3-4

R = RPM option

- N = Number of sectors per revolution

- \* See Note 1, Table 3-4

Maximum time available for the Data Field is:  $T_{DF} = \begin{bmatrix} T_{sector} & -\sum Time For Tolerances \end{bmatrix} usec$

NOTES:

- (1) Assuming that read channel is settled before sector mark

- (2) Assuming that read channel is turned on at sector mark