# This PDF contains the contents of a folder from the Wang 2200 development group, labeled

# 2600 DEVELOPMENT TOOLS

It is an assortment of specifications and some handwritten notes.

BASBOL

MICROPROGRAMMING

Revised March 24, 1981

Bruce Patterson

2200 MVP COMPUTER ARCHITECTURE

Author: Bruce M. Patterson

November 30, 1979

# System Architecture

Wang 2200 computer systems employ a direction execution high-level-language (HLL) architecture. With direct execution HLL systems the HLL is effectively the machine language of the computer. Unlike more conventional architectures where the source code is transformed into a distinct object code before processing, the direct execution system processes the source code directly.

The direct execution system provides a number of advantages over more traditional architectures, not the least of which is its conceptual simplicity. The more conventional layers of software including assemblers, linkage editors, compilers, and loaders are eliminated. The inherent conversational nature of the system facilitates programming and debugging. The debug run and execution run are identical. Error messages can easily include a listing of the actual source code. Program execution can be halted, single stepped, and restarted. Since there is no compilation phase, the system responds immediately to program entries and modifications. Programmers can understand the language semantics by observing the direct response of the system.

The 2200 provides the user with a single HLL, BASIC-2, which is used for all programming. Proficiency in system use is easily achieved since there is only one language to learn. A fundamental design criterion in the development of BASIC-2 was to provide a self-sufficient language that would be as flexible as conventional general purpose computer instruction sets. I/O and data handling language extensions provide the user with flexibility not usually found in a high-level-language.

The 2200 is not a pure direct execution machine since the source code is preprocessed into a form more memory conservative and more efficiently interpreted. However, source and object differences are such that the preprocessor transformation is nearly completely reversible. As a result, only the condensed code is stored in the machine. The preprocessing function eliminates gross inefficiencies in memory, timing, and logic requirements.

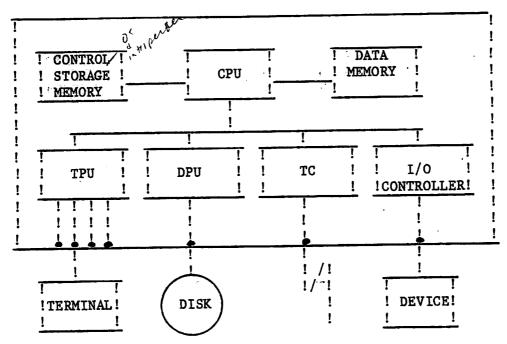

### 2200 Hardware

2200 computers consist of a microprogrammed MSI processor coupled with a number of special purpose LSI I/O processors and controllers. The OS and language interpreter reside in a large control storage memory which is independent from user data memory; this microprogram directs the execution of the CPU and coordinates communication with the I/O processors. The independent I/O processors permit the overlap of the CPU and I/O processing. The CPU is relieved of the responsibility for controlling peripherals that would otherwise require frequent or dedicated CPU attention.

0.5. + (anguage interpreter = control 2 Storage memory.

Figure 1 2200 System Block Diagram

The 2200 CPU is a pseudo 16-bit processor using a 3-bus architecture for interconnecting a bank of general purpose, status, and I/O 8-bit registers and the ALU. A microinstruction can address these registers as double, single, or half registers for performing 16, 8 or 4-bit operations. In addition, a bank of 16-bit registers that can be exchanged with the data memory address pointer provides quick access to major system pointers. The extensive microinstruction set consisting of 24-bit words provides decimal and binary arithematic, logical operations, and a wide variety of conditional branching instructions.

In a single CPU cycle, a 24-bit microinstruction can be fetched, 16-bits of data memory can be fetched, and a 16-bit operation can be performed. The wide memory path, 600 nsec. cycle time, and rich microinstruction set provides a highly effective processor for implementing direct execution languages.

User programs and system controllers are kept in data memory, of which 256K can be installed. Since the CPU's address space is limited to 64K, however, data memory is divided into 64K banks. In order to provide the microprogram with access to control tables without switching memory banks, the lower 8K of the address space always refers to bank 1. The lower 8K of banks 2, 3, and 4 is not used.

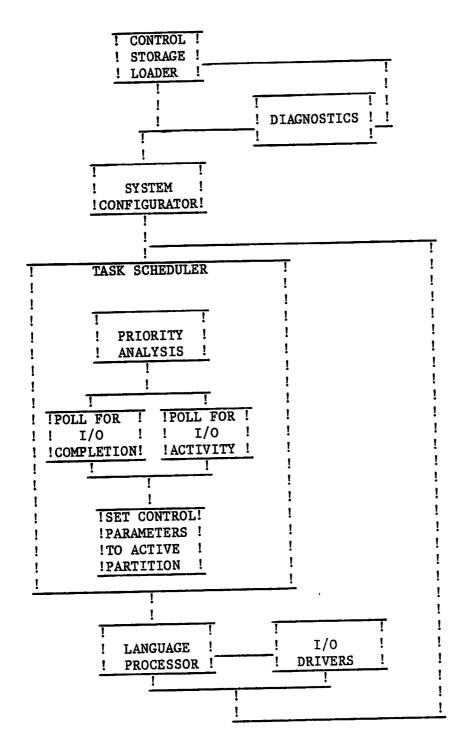

## MVP Operating System

The 2200 MVP multiprogramming operating system allows several users to share a single computer effectively. To accomplish this, the operating system divides the resources of the computer — memory, peripherals, and CPU time, — among the users. Once each user has been allocated a share of the computer resources, the operating system acts as a monitor, allowing each user to utilize the system in turn while preventing the various users from interfering with each other's computations.

The MVP employs a fixed partition memory scheme. User memory is divided into a number of sections or "partitions", each of which can store a separate program. From the user's point of view, each partition functions independently from the other partitions in the system. Each user may LOAD and RUN BASIC software, compose a program, or perform Immediate Mode operations. As in a single-user environment, the user has complete control over his or her partition. No user on the system may halt execution in, or change the program text of, a partition controlled by another user.

Each terminal may control several partitions executing independent jobs. At any given time, however, only one of these partitions is in control of the terminal and thus capable of interacting with the operator. The partition in control of the terminal is said to be in the "foreground." Other partitions assigned to the terminal may continue to execute in the "background" until operator intervention becomes necessary.

Although partitions in general function independently of one another, there are situations in which it is useful for two or more partitions to cooperate. Cooperating partitions may share program text and/or data. The sharing of commonly used programs and data by several partitions eliminates needless duplication and produces more efficient use of available memory. The integrity and independence of a partition which contains shared programs or data are maintained by requiring the partition to explicitly declare itself to be global (sharable) before it can be accessed by other partitions. Correspondingly, a partition wishing to access shared text or data in a global partition must identify the desired global partition.

Figure 2 Block Diagram of 2200 MVP OS

To the programmer who regards the MVP system as a whole, it appears that all partitions are executing simultaneously. Because all partitions share a single CPU, however, only one partition can be executing at any given moment. The operating system creates the illusion of simultaneous execution of several programs by rapidly switching from one to the other in turn.

Partitions in the 2200 MVP are serviced by the CPU in a "round-robin" fashion, with priority given to I/O operations. Each partition in turn is given a "timeslice" 30 milliseconds (ms) in duration. The CPU has a completion of each BASIC statement (and at various points in the middle of long statements and I/O operations), the clock is checked to see whether the 30 ms timeslice has been exhausted. When a partition's partition so that it may be restored later when that partition's turn comes around again. The operating system saves the status of the next partition in line and begins its 30 ms timeslice. The process of halting execution of a partition at the end of its timeslice is called a "breakpoint".

Timeslices do not always last exactly 30 ms. Unlike many operating systems, the MVP switches users (breakpoints) whenever it is convenient rather than strictly by the clock. This technique reduces the amount of status information that must be saved, giving the MVP low operating system overhead when compared with most other multiuser systems. More importantly, breakpoints may occur in the middle of BASIC statements. If, for instance, the current partition attempts a disk access and the disk is hogged by another partition, this condition is quickly detected and a breakpoint occurs. I/O breakpoints differ from program breakpoints in that the partition is specifically marked as "waiting for I/O". When the partition's turn comes around again, the system takes only a few microseconds to decide whether processing may proceed or whether the partition is still waiting for the I/O device and may be bypassed. Thus, if a printer goes "busy" while it performs some mechanical function or if a partition that does not currently control the terminal attempts to write to the CRT, the system bypasses that partition almost as effectively as if it were removed entirely from the system until the I/O device becomes available.

#### DOCUMENTATION

Careful documentation is a requirement of all BASBOL system software. It is essential for system maintenance and will encourage complete, well thought out design with well defined interfaces. Most of the module documentation should be included within the source listings; however, it is acceptable to provide supplementary narratives and diagrams in memo form. Documentation should be structured, providing first a quite general view of the project followed by progressively more detailed levels of description. The following approach should be used when documenting a logical software module.

### a. Module documentation

### 1. Introduction

Should present an overview of the function and scope of the naive reader. This is the starting point for understanding what the module does and how it performs that function.

### 2. Completion Report

Documentation should include a section describing what portion of the project has currently been implemented. For BASIC-3, specify all implementation exceptions and extensions to BASIC-2. For COBOL; include all exceptions and extensions to ANSI and VS COBOL.

### 3. Processing

This section should describe how the software performs the specified function. The explanation should describe what happens in each phase (entry, resolution, and execution) of processing general flow diagrams should be included to clarify the process flow where necessary.

#### 4. Data Structures

Descriptions and diagrams explaining the function, relationships, and data structures used should be provided.

### 5. Register and Data Memory Use

Register and data memory use common throughout the module should be described. Include equates for AUX registers and data memory locations.

c. Routine Section Comments

A routine generally should be decomposed into logical sections. Each section should be separated and started with a description of the function of that section.

For example, the following routine shifts a string to the right or left.

Describe whether to shift left or right.

LPI,R START get start address

BLRX CHCL,FIFO,LEFT branch if start dest.

\* LEFT: shift string to left. Now we start at left end of string.

LEFT XPA + 1,R,,0

It is often convenient to include checkpoint information at major section headers. Current register contents are particularly useful for program checkout. For example, the following logic is part of the MOVE statement:

\*%===SETUP======

- \* Setup parameters for move

- \* routine

MVX F3F2, PHPL

\*%===PERFORM MOVE====

- \* At this point the following

- \* registers are setup:

- AUX 3 = address of description A

- # AUX 4 = address of description B

- # AUX 5 = offset to A

- \* AUX 6 = offset to B

SB MOVE COB MOVE DATA

d. Source Line Comments

Nearly every source line should be commented as to its logical function. Avoid describing physically what the instruction does, for example,

MV CH,FO load FO with CH

e. Blank Lines

Blank lines should be used freely to improve code readability.

### f. Tags

Tags within a particular routine should all begin with the same prefix, to avoid conflicts with other programmers. Tags internally referenced should have a numeric suffix. Tags externally referencable (i.e., entry points) should have an alphabetic suffix.

### 5. NOTATION CONVENTIONS:

- a. byte = logical 8-bit group

- b. bit notation:

- X X X X X X in a byte, X 80 80 40 20 10 04 02 01 8 2 1

- 2. to reference more than 1 bit in a byte, the HEX value of the combined bits can be used. For example,

bits CO = bit 80 and bit 40 bits O5 = bit O4 and bit O1 bits A2 = bit 80, bit bit 20 and bit O2

3. in multibyte values (e.g., AUX's), the HEX value of the bits is used. For example,

bit 0001 = low order bit

bits 000F = low 4 bits

bits FF00 - high byte of value

### 6. REGISTER USE

Auxiliary registers 10-1F are reserved for system pointers and flags. They are referenced by name only (e.g., VSPTR) to improve code readability. AUX registers 00-0F are for general use. By convention, subroutines should use the lowest numbered registers possible. Hopefully, this will conserve the register use and minimize conflicts.

The following list specifies which AUX's are available during the various phases of processing.

Entry phase: AUX 0-7

Resolution phase: COBOL

IDENTIFICATION DIVISION: 0-7 ENVIRONMENT DIVISION: 0-7 DATA DIVISION: 0-F PROCEDURE DIVISION:

statements: 0-7 global logic: 8-F

BASIC-1.

statements: 0-7 global logic: 8-F

Execution phase: 0-F

The lower level routines should use lower numbered AUX's. For example, in COBOL the arithmetic and move primitives use AUX registers 0-6.

Lowest numbered file registers should be used whenever possible. Typically, entry and return parameters are passed through low numbered file registers. When 16 bit values are stored in a file registers pair, the register with the higher address contains the high byte of the value.

The low 2-bits of register SL specify the processing phase. The following equates should be used whenever phase checking is done:

EPHASE EQU FF-03 entry phase (00)

RPHASE EQU 01 resolution phase (01)

XPHASE EQU 02 execution phase (02)

### For example:

BFL XPHASE,SL,TAG1 branch if not exection BTL RPHASE,SL,TAG2 branch if resolution BFL RPHASE+XPHASE,SL, TAG3 branch if entry

### 7. BASBOL Base Code

The MVP BASIC-2 Release 2.1 microprogram provides the base code for BASBOL development. The base code resides at 0000-5FFF and will be changed infrequently, perhaps once a month, to incorporate developed code. Each microprogrammer will be assigned his own 2280 platter which will contain the base code external symbol table files, the base object code, and space for microcode development. The base source code should be modified at the prescribed update times. During development, the base code can be patched or routines can be duplicated in the development space and then modified.

The base object code is contained in the files @BAS.

# 8. CONTROL MEMORY MAP

0000-5DFF

BASE

CODE

5E00-5FFF

MDU

6000-7FFF

NEW

CODE

Current development units are limited to 32K; however, 64K units are under development.

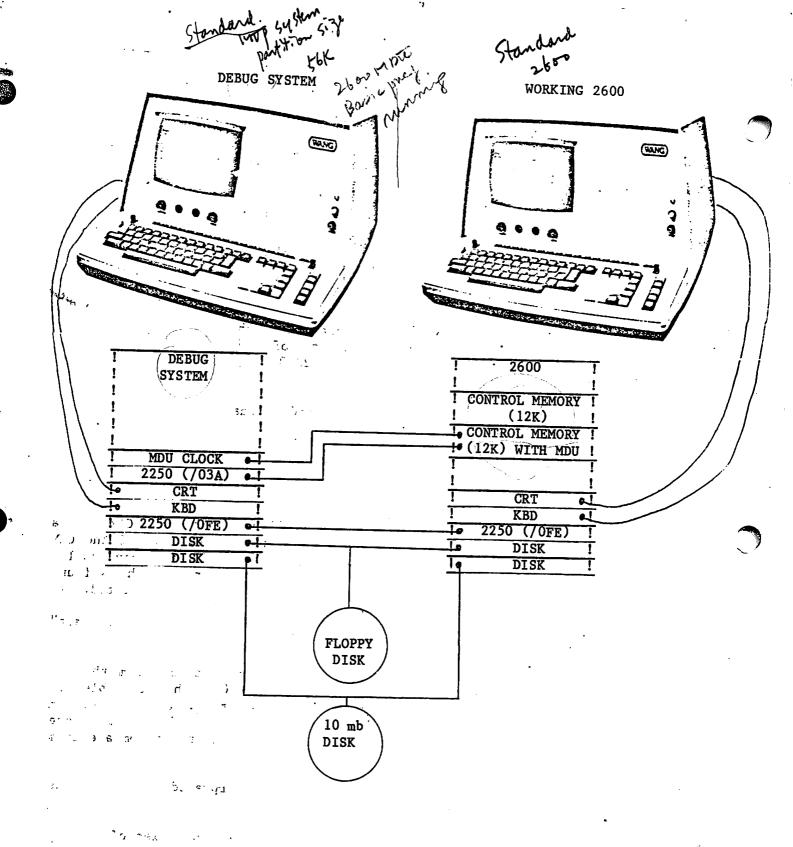

#### 9. DEVELOPMENT SYSTEMS

Four MDU systems are available for debugging microcode. A floppy disk (/310 or /320) and a sort to the band printer (/216) is available on each system.

Three additional 256K MVP systems are used for monitoring the MDU systems, editing, and assembling.

System #1 is used for editing, assembling, and 2280 backup to tape. Assembling is done via terminals in the lab. The following perpherals are available:

|                 | floppy disk                                |

|-----------------|--------------------------------------------|

| (/320)          | 10 mb disk                                 |

| (/D30-/D-75)    | Pair of 80 mb disks                        |

| (/215)          | chain printer                              |

| (/216)          | band printer                               |

| ( <b>/</b> 07B) | tape drive                                 |

|                 | (/320)<br>(/D30-/D-75)<br>(/215)<br>(/216) |

System #2 monitors MDU #1 and MDU #2 and provides partitions for editing. The following perpherals are available:

| 2270A  | (/310)      | floppy disk, shared with MDU #1 |

|--------|-------------|---------------------------------|

| 2270A  | (/320)      | floppy disk, shared with MDU #2 |

| 2280-3 | (/D30-/D75) | pair of 80 mb disks             |

| 2273   | (/216)      | band printer                    |

System #3 monitors MDU #3 and MDU #4 and provides partitions for editing. The following perpherals are available:

| 2270A  | (/310)      | floppy, shared with MDU #3 |

|--------|-------------|----------------------------|

| 2270A  | (/320)      | floppy, shares with MDU #4 |

| 2280-3 | (/D30-/D75) | pair of 8 mb disks         |

| 2273   | (/216)      | band printer               |

#### MEMORANDUM

TO:

2600 Distribution

FROM:

F. Vine, B. Patterson

DATE:

August 27, 1975, Revised September 12, 1975

SUBJECT:

Revisions to 2600 Hardware Structure

This memo describes changes, as understood by 2600 microcoding groups, to the 2600 CPU specifications described in the document "2600 Calculator Structure" dated December 6, 1974, Revised February 14, 1975. Additional specifications are also provided. Updated pages for the specifications document are included. If any specifications are incorrect, please provide corrected specification A.S.A.P.

1. Deletion of binary add (A) instruction

The register instruction binary add (A) has been eliminated from the micro-instruction repertoire. The binary add with carry (AC) instruction suffices since carry can be set off at the beginning of the instruction. Note, that the AI and ACI instructions have not been eliminated.

2. Addition of binary subtract with carry (SC) instruction

The register instruction binary subtract with carry (SC) replaces the A instruction.

3. Write control memory (SR, WCM) instruction

The SR, WCM instruction requires that the high 8-bits of the instruction being written (K register) be complemented; PH, PL remain as originally specified (true, uncomplemented).

The data read by a SR, RCM instruction is true in K, PH, and PL.

4. Write to data memory on an extended register instruction

In an extended register operation with write to data memory specified, the high order byte of the result is written (i.e., the result of the 2nd half of the operation).

#### 5. Instruction timings

The cycle time is 600 nanoseconds for all instructions except for the following 3 that execute in 800 nanoseconds:

**BLERX** BLRX SR

and the following 2 instructions that execute in 1.6 microseconds.

and the following instruction that executes in 1 microsecond LPI. SR, WCM

6. Trap addresses (located in PROM/ROM bootstrap area)

8000 -- PECM (parity error in control memory) 8001 - RESET 8002 -- PEDM (parity error in data memory) 8003 - POWER ON 8004 - 800F (spares)

7. Load PC's immediate instruction extention

> Write to data memory (W1, W2) are legal on LPI instructions; however, the data written is always zero since there are no extra bits available to specify what is to be written. In previous specifications write was illegal on LPI instructions.

8. Parity specifications

Page 14 describes instruction and data parity and parity errors.

#### MEMORANDUM

TO:

2600 FILE

FROM:

Bruce Patterson

DATE:

December 6, 1974, Revised February 14, 1975, Revised Sept. 12, 1975

SUBJECT:

2600 Calculator Structure

The following memo describes the 2600 structure as of December 1, 1974. I/O specification will be described in another document. The following list summarizes the major changes to the specifications presented in the memo "2600 Calculator Structure" dated October 11, 1974:

- 1. Due to timing considerations, instructions that reference data memory will use the contents of PH and PL at the beginning of the instruction as the memory address. Previously, the contents of PH and PL at the end of the instructions were to be used. The LPI instruction is the only exception to the rule; if an LPI instruction specifies a read or write, the new contents of PH and PL will be used as the memory address.

- 2. The codes for the Mini Instructions and SHFT instruction have been slightly changed for easier decoding.

- 3. The instructions that Read and Write control memory (RCM, WCM) have been replaced by 2 new instructions (SR, RCM and SR, WCM).

Note, that the SHFT instruction has been modified so that either the high or low 4-bits of both the A and B BUS registers can be specified. Also, A-BUS specification of PC incrementing and decrementing is disabled during extended operations.

#### . MEMORANDUM

TO:

2600 File

FROM:

Norman Lourie, Bob Kolk, Bruce Patterson

DATE:

October 11, 1974, REVISED December 5, 1974, REVISED February 14, 1975,

REVISED September 12, 1975

SUBJECT:

2600 Calculator Structure

This memo will specify in detail the register structure, instruction set and memory referencing structure for a 24-bit micro-programmed processor which is planned for the 2600. Although maintaining the A, B, C bus structure of the 800 micro-processor, it has a number of features which will significantly improve speed, code efficiency, and capacity.

### Register Structure

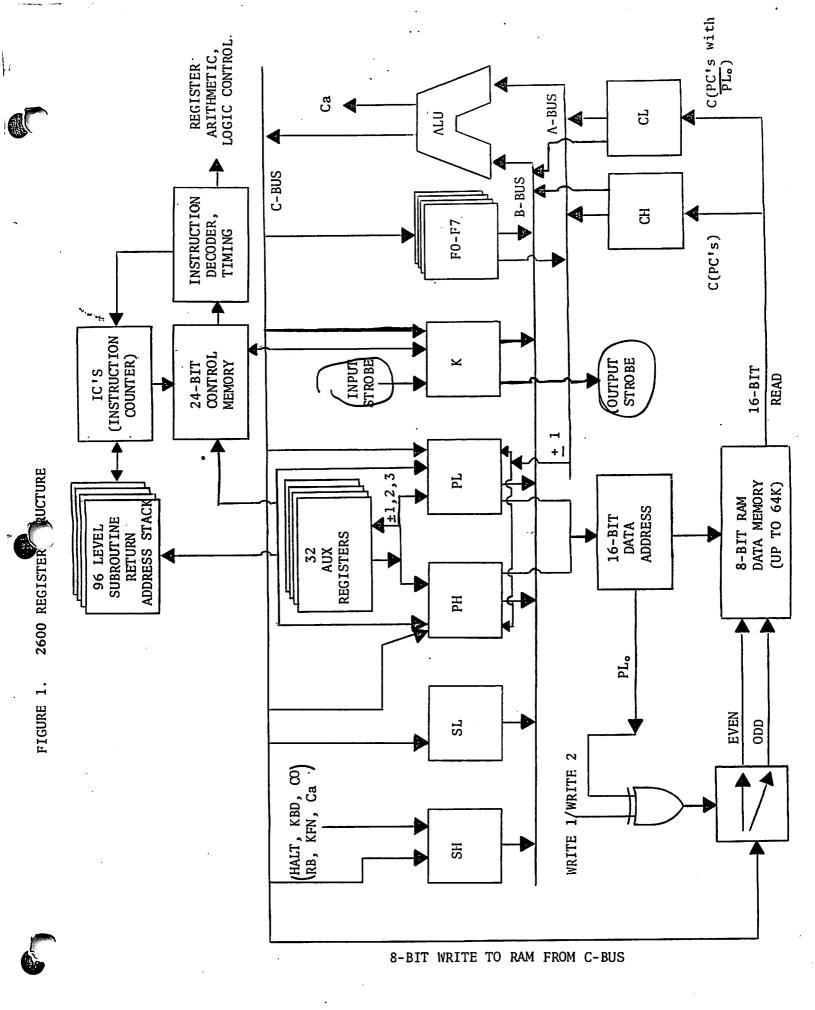

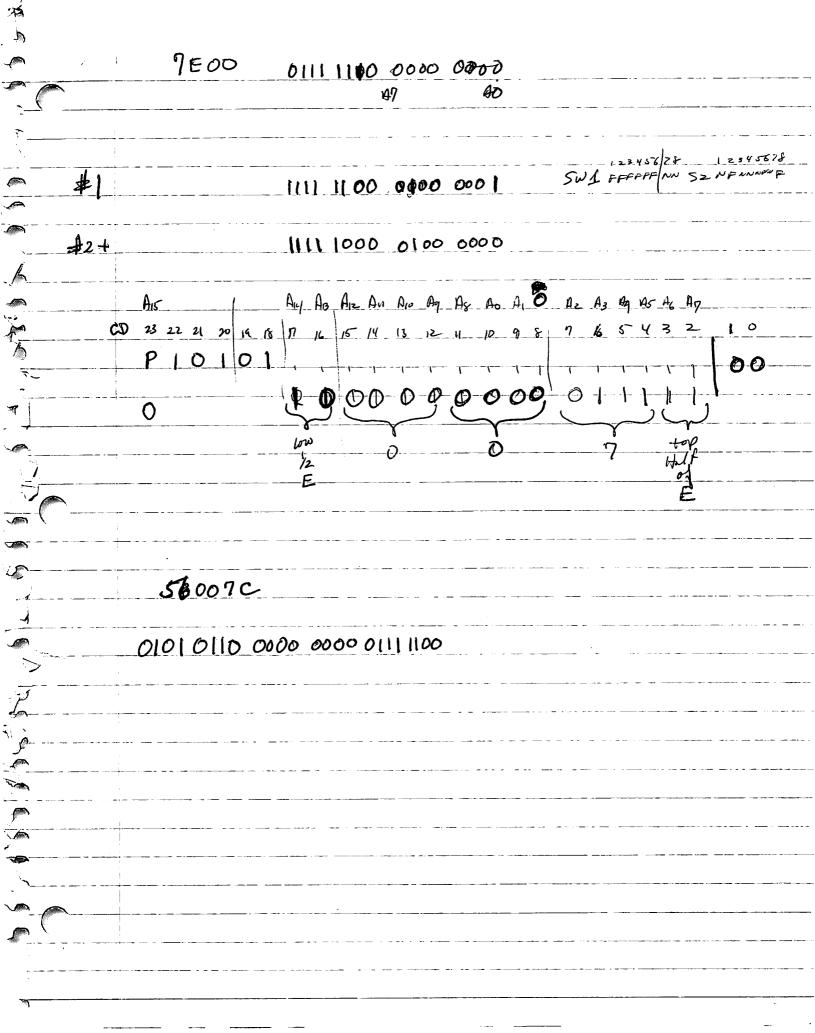

Figure 1 illustrates the tentative register structure for the processor.

The processor will contain 15 8-bit registers which can be read and/or written by micro-program instructions, an arithmetic logic unit and registers for holding the current 24-bit micro-program instruction and 16-bit address, and 32 16-bit auxiliary registers which back up the Data Memory Program Counter. In addition, an 8-bit dummy register exists, the dummy register cannot hold data; its value is always zero. level subroutine stack is provided to allow efficient subroutine calling.

1 = DO NOT TRAP IF PARITY ERROR

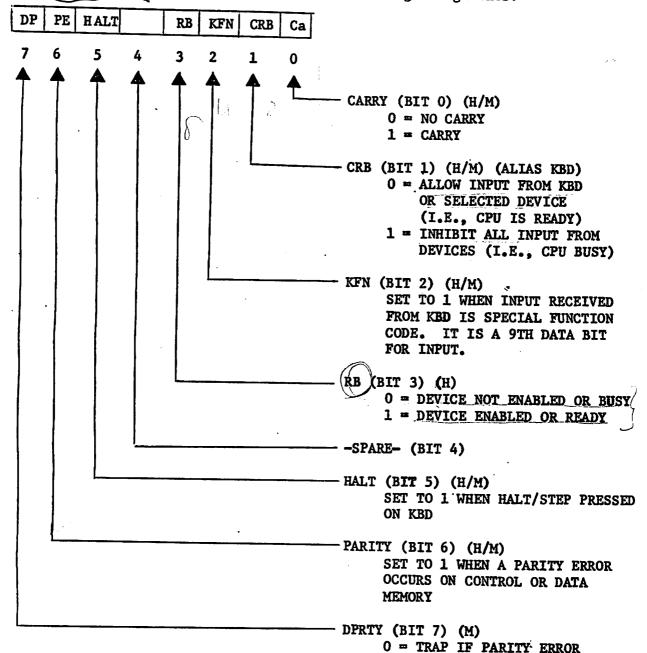

# (1) SH - Status Register High

An 8-bit register used to sense or set various arithemtic, I/O, and keyboard status conditions. It has the following assignments:

MOTE: (M) = Set by microprogram only.

(H) = Set by hardware only (D. C. level).

(M/H) = Set by microprogram or hardware.

### (2) SL - Status Register Low

An 8-bit status register used by the micro-program to indicate phase of processing, mode, and other conditions. This register is set only by the micro-program.

# (3) PH, PL - Data Memory Program Counters (PC's)

These 2 registers are used to hold the 16-bit current address of data words which are read from and written into Data Memory or Control Memory.

Data memory reads and writes are specified in the register instructions by use of the DD bits. For writes, 8-bit data is written from the C-bus to the Data memory location specified by the initial contents of the PC registers. For reads, 16-bits of data are read into the CH and CL registers. The details of memory addressing are described in a later section.

The PC's are also used for reading and writing the low 16-bits of a 24-bit instruction in control memory.

## (4) K - Keyboard Input and I/O Registers

This 8-bit register is used to receive keyboard input and to receive and send data to and from other I/O devices. The K register is also used to read or write data to Control Memory.

# (5) <u>FO - F7 - File Registers</u>

These eight 8-bit registers are general purpose registers which will be used to perform arithmetic computations and related calculator processing. The file registers can be both source and object registers for any of the register transfer micro instructions.

# (6) ALU - Arithmetic Logic Unit (5-bit path)

This unit is used to perform the addition, subtraction, and Boolean functions specified by the micro-program instructions.

Eight-bit data paths are input from the A and B bus and output to the C-bus. For add instructions, a carry bit is also transferred between the ALU and status register bit  $SH_0$ , if specified.

# (7) AUX 0 - 1F - Auxiliary PC Save Registers

There are up to 32 16-bit registers which are used to temporarily save and restore the contents to the Data memory program counters (PH, PL). Sixteen bit transfers of PC's  $\rightarrow$  AUX and AUX  $\rightarrow$  PC's and a sixteen bit exchange are provided. These operations are extremely useful when Data is being moved, or when two sets of data are being operated on at the same time. When the address is transferred (or exchanged) to the Auxiliary registers, a 16-bit incrementing or decrementing of  $\pm$  1,  $\pm$  2, or  $\pm$  3 can be specified on the data received by the auxiliary register by certain mini-instructions.

The AUX registers are selected by the five Ax bits of the mini-instructions which specify the transfers and exchange.

# (8) CH, CL - Data Memory Read Buffers

These two 8-bit registers are used to receive the 16-bits of data read from data memory. CH will always receive the 8-bits of data from RAM that is exactly specified by the 16-bit address in PH, PL. CL will receive the 8-bit word located at the address specified in PH, PL but with the low order bit of the address complemented. (i.e., the address in  $PC's \pm 1$ ).

# (9) IC1, IC2, IC3, IC4 - Instruction Program Counter

The four 4-bit registers contain the current micro-program instruction address. Although these registers are not addressable by register instructions, they are reset by Branch, Subroutine Branch and Subroutine Return Instructions. A 96 level circular subroutine address save stack is available to save and restore the IC register. In addition, commands are available to transfer the PC registers (Data Memory program counter) to and from the stack.

### B. Memory Addressing Structure

The processor can be considered to have two separate memories:

### (1) Control Memory (24-bit RAM)

This RAM memory contains up to 64K of 24-bit words. It holds the micro-instructions. Instructions fetched and executed under control of the Instruction Program Counter, (IC1, IC2, IC3, IC4), which is indexed for sequential instruction execution and reset for branch, subroutine branch and return micro instructions.

Control Memory is available in increments of 4K words, up to 64K words. Since only 10 bits are referenced by some branch instructions, instruction memory can be thought of as paged memory with 1024 24-bit words per page for these instructions and an in-page jump is performed. Other instructions allow full 16-bit (64K) transfers.

### (2) Data Memory (8/16-Bit RAM)

Data Memory is the memory which is read and written by the micro instruction. Up to 64K of 8-bit RAM (Random Access Memory) can be addressed.

The memory is addressed by the Data memory program counters (PH, PL). The program counter contains a 16-bit address which addresses a location in RAM.

Reads and writes are done by having non-zero data in the DD bits of register instructions. (00 = no read or write, 01 = read, 10 = write 1, 11 = write 2). For a read, 16-bits are read from Data memory. CH receives the 8-bits of data specified by the address in the PC's. CL receives the 8-bit word located at the address in the PC's but with the low order bit of the address ( $PL_0$ ) complemented (i.e., the address in PC's  $\pm$ 1).

For a write 1, 8-bits are written from the C-Bus (final result of a register instruction) to the address specified by the initial contents of the PC's. For a write 2, 8-bits are written from the C-Bus to the address in the PC's but with the low order bit of the address complemented. (i.e., the address is PC's + 1).

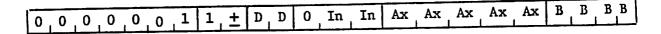

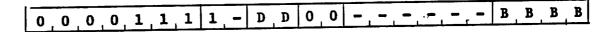

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 10                   |                                        | 苦思姓出语                                      |                               | ,         | <b>强复货运运运运</b>                                                                                                                                                                                           |          |                                                                                                                                                                                                                            |     |                       | <b>8888</b>                          |         | ммм                                                           | 11              | <del></del>                           | 1   |                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|----------------------------------------|--------------------------------------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|--------------------------------------|---------|---------------------------------------------------------------|-----------------|---------------------------------------|-----|--------------------------------------------------------------------|

| N. N. C. S. C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | , ,                  |                                        |                                            | 2 20 2                        |           |                                                                                                                                                                                                          | B. Billo |                                                                                                                                                                                                                            | ۱   | B-BU                  | дада                                 | B-BUS   | HHH                                                           |                 | × ×                                   |     |                                                                    |

| 1. NOMISTER INSTRUCTIONS   1. NOMISTER INSTRUC   |   | 9                    | A-BUS<br>A A                           |                                            | A A A MEDIAT                  | (LOH)     | ннининн<br>ннининн<br>ннининн                                                                                                                                                                            |          | AX A                                                                                                                                                                                   | -   | MASK                  | ****                                 | 1-BUS   | 444                                                           |                 | 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 |     | Address of auxiliary register<br>Increment/decrement specification |

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | œ                    | ပပပ                                    | 00000                                      | 0                             | 1         | 0000000                                                                                                                                                                                                  | H        | A A A A A A A A A A A A A A A A A A A                                                                                                                                                                                      | 4   | $\vdash$              | ZZZZ                                 |         | 4444                                                          | 11              |                                       |     | y regis:                                                           |

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 2, 11, 10            | 000                                    | (00000                                     |                               |           | 0000000                                                                                                                                                                                                  |          | 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                        |     |                       | ***                                  | -       | 我我我的                                                          | יו ו            | 'i l                                  |     | auxillar<br>ecrement                                               |

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 14 13 1              | Ca D D Ca D D                          | eeeaa                                      |                               |           | 00000000                                                                                                                                                                                                 | 11       | 963691160 6                                                                                                                                                                                                                |     | H FIELD               | <b>812</b>                           | H FIELD |                                                               | 1 3             | 22                                    |     | ress of au<br>rement/dec                                           |

| 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 7 16 15              |                                        | 5555 <u>2</u>                              | o o                           | ()        | пининин В                                                                                                                                                                                                | <br>     | нанананана                                                                                                                                                                                                                 |     | BEAUC                 | 机双双尺                                 | BRANC   |                                                               |                 |                                       | •   |                                                                    |

| 1. KEGISTER INSTRUCTIONS   COR     COR   C   |   | E1 .                 | 040                                    |                                            | E H                           |           | ононон                                                                                                                                                                                                   |          |                                                                                                                                                                                                                            |     |                       | et at et et                          |         | K N. K.                                                       | I BE            | 14 64                                 |     | AxticlxAx:<br>± In In:                                             |

| 1. KUNGISTER INSTRUCTIONS  OR  NOR  NOR  DECLINAL Subtract with Carry  OC  SC  DECLINAL Subtract with Carry  OC  SINT  BIANTY Maliciply  NOR  SHIFT  SHAFT  OR  AND  AND  AND  AND  AND  AND  BIANTY Add with Carry  OC  AND  AND  AND  AND  AND  BIANTY Add Immediate  AND  AND  AND  AND  BIANTY Add With Carry Immediate  OC  AND  AND  AND  BIANTY Add With Carry Immediate  OC  AND  AND  AND  BIANTY MALTIPLY Immediate  AND  AND  AND  AND  AND  AND  BARNAT ADD  AND  AND  AND  AND  AND  AND  AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . | تا <u>چ</u>          | 000                                    | 64444                                      | 0 8                           | $\dagger$ | 00004444                                                                                                                                                                                                 | OP CODE  | 00000000000                                                                                                                                                                                                                | -   | OPCODE                | ООНН                                 |         | 0011                                                          | OPCODE          | нн                                    |     | γx                                                                 |

| 1. NIGISTER INSTRUCTIONS  OR - Or  NOR - Exclusive Or  AND - And  SC - Banary Subtract with Carry  DSC - Decimal And with Carry  NGC - Decimal Subtract with Carry  AC - Binary Add with Carry  NUM - Shift  AI - Shift  AI - Shift  AI - Shift  AI - Binary Add with Carry Immediate  AI - Decimal Subtract with Carry Immediate  AI - Decimal Add with Carry Immediate  AI - Decimal Subtract with Carry Immediate  AI - Decimal Subtract with Carry Immediate  DACI - Binary Add with Carry Immediate  AI - Decimal Subtract with Carry Immediate  AI - Binary Add with Carry Immediate  AI - Binary Add with Carry Immediate  AI - Binary Hultiply Immediate  AI - Binary Hultiply Immediate  AI - Binary Hultiply Immediate  SR, WCM - Exchange PC's to Aux  TAP - Transfer Stack to PC's  SR, WCM - Ransfer Stack  BIR - Branch if Faise  BER - Branch if # Negister  BIR - Branch if # Negister  BIR - Branch if # Register  BIR - Bra | L |                      | 0000                                   | <u> </u>                                   | <u> </u>                      | -         | ate 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                | -        | 0000000000                                                                                                                                                                                                                 |     |                       | T I                                  | -       |                                                               |                 | ا ٥٠١                                 |     |                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | EGISTER INSTRUCTIONS | - Or<br>- Exclust<br>- And<br>- Bingry | Decimal Decimal Binary / Binary / Binary / | HEDLATE REGISTER INSTRUCTIONS | '         | - Or Immediate - Exclusive or Immediate - And Immediate - Binary Add Immediate - Decimal Add with Carry Imme - Decimal Subtract with Carry - Binary Add with Carry Immediate - Binary Hultiply Immediate |          | Transfer Aux to PC's  Transfer PC's to Aux Exchange PC's to Aux Transfer PC's to Stack Transfer Stack to Stack Transfer Stack to PC's RCM - Read Control Hemory Subroutine Return Control Input/Output Load PC's Immediate | •   | k braich instructions | Branch<br>Branch<br>Branch<br>Branch | BRANCH  | Branch 1f < Branch 1f < Branch 1f = Branch 1f = Branch 1f # R | CH INSTRUCTIONS |                                       |     | A-BUS<br>D-BUS                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 1 1                  | 8 2 2 2 2                              | N A D D                                    | 11                            | 1         | . 11                                                                                                                                                                                                     | KIK JII  |                                                                                                                                                                                                                            | - 1 | - 1                   | 1 1                                  | - 1     | BLER<br>BLER<br>BER<br>BIR                                    | VI. BRAYC       | SB                                    | KEY | AAAA:<br>Bubb:                                                     |

CaCa: RR...R: S: S: C-BUS Re Read/Wri 00 = n 01 = r 11 = w High/low

16, Ha:

.

# 1. D D - Data Memory Read and Write Selection Bits

D D = 00 Null (No read or write)

D D = 01 Read; 16 bits read from memory into CH, CL where  $C(PC's) \rightarrow \frac{CH}{PL_0} \rightarrow CL$

D D = 10 Write 1; 8-bit write to memory C-Bus  $\rightarrow$  C(PC's)

D D = 11 Write 2; 8-bit switched write into memory C-BUS  $\rightarrow$  C(PC's with PL<sub>0</sub>)

# 2. A, B, and C-Bus Register Addressing

| A-BUS                                                                                                                                                                                | B-BUS                           | C-BUS                               | BINARY ADDRESS                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------|-----------------------------------------------------------------------------|

| File registers (FO - F7) CL with PC's = PC's - 1 CH with PC's = PC's - 1 CL CH CL with PC's = PC's + 1 CH with PC's = PC's + 1 Dummy with PC's = PC's + 1 Dummy with PC's = PC's - 1 | FO-F7 PL PH CL CH SL SH K Dummy | FO-F7 PL PH illegal illegal SL SH K | 0000 - 0111<br>1000<br>1001<br>1010<br>1011<br>1100<br>1101<br>1110<br>1111 |

- The B-BUS and C-BUS registers are identical except that CL and CH are illegal on the C-BUS.

- 2. The A-BUS field can specify that the PC address bits be incremented or decremented by 1 at the completion of the instruction.

- When the D D bits specify a read or write and the A-BUS field specifies a PCl = PCl + 1, the read or write is executed before the PC's are incremented or decremented.

- 4. For mini commands with write selected, the B-BUS register will be written (before PC's are incremented or decremented, if applicable).

- 5. The "contents" of the dummy register is always zero.

## 3. X - Extended Operation Bit

Normally, a register instruction performs an 8-bit operation on the specified A-BUS and B-BUS registers and puts the result in the C-BUS register. A BLR (branch less than) or BLER (branch less than or equal) instruction compares two 8-bit registers and branches if the relation is true. In these cases, the extended operation bit is not set (i.e., X = 0).

If the extended operation bit is set (i.e., X=1), a register instruction performs a 16-bit operation on a pair of A-BUS registers with a pair of B-BUS registers and puts the result in a pair of C-BUS registers. A BLR (branch less than) or BLER (branch less than or equal) instruction compares a pair of A-BUS registers with a pair of B-BUS registers and branches if the relation is true.

For extended operations, the register pair is treated as a single 16-bit register. The registers used are determined as follows. The low half of the pair is the register whose address is specified in the instruction. The high half of the pair is the register whose address is one more than the address specified.

## EXTENDED OPERATION REGISTER PAIRS

| A-BUS                                                                                                                       | B-BUS                                                                                                               | C-BUS                                                                                                                          | BINARY ADDRESS                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| F1, F0 F2, F1 F3, F2 F4, F3 F5, F4 F6, F5 F7, F6 CL, F7 CH, CL CL, CH CH, CL CL, CH CH, CL Dummy, CH Dummy, Dummy F0, Dummy | F1, F0 F2, F1 F3, F2 F4, F3 F5, F4 F6, F5 F7, F6 PL, F7 PH, PL CL, PH CH, CL SL, CH SH, SL K, SH Dummy, K F0, Dummy | F1, F0 F2, F1 F3, F2 F4, F3 F5, F4 F6, F5 F7, F6 PL, F7 PH, PL illegal illegal illegal illegal SH, SL K, SH Dummy, K F0, Dummy | 0000<br>0001<br>0010<br>0010<br>0011<br>0100<br>0101<br>0111<br>1000<br>1001<br>1010<br>1011<br>1100<br>1101 |

#### NOTE:

- 1. On extended operations A-BUS specification of PC incrementing or decrementing is disabled.

- 2. On an extended operation, if write is specified the value written is the high order result.

# 4. CaCa - Set Carry Field

All register instructions except  $\,^{M}\,$  and SHFT can set the carry bit (SH<sub>0</sub>) to 0 or 1 at the beginning of the instruction execution. The set carry options are:

CaCa = 00 -- Do not set carry CaCa = 10 -- Set carry to 0 CaCa = 11 -- Set carry to 1

(NOTE: 01 reserved for SHFT)

# 5. Ha, Hb -- High/Low 4-Bit Selection

The Mask Branch, M, and MI instructions operate on either the high or low 4 bits of the A and/or B registers. The Ha bit specifies the high or low 4 bits of the A-Bus register; the Hb bit specifies the high or low 4 bits of the B-Bus register.

Ha = 0 Low 4-bits of A-Bus register

Ha = 1 High 4-bits of A-Bus register

Hb = 0 Low 4-bits of B-Bus register

Hb = 1 High 4-bits of B-Bus register

### 6. II...I -- Immediate Operand

For Immediate Register Instructions, the actual 8 bits contained in the Immediate Operand Field (IIII) are gated directly to the A-Bus. For the LPI '(load PC's immediate) instruction, the PC's are set equal to the 16-bit immediate field.

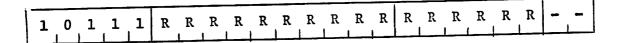

### 7. RR...R -- Branch Addresses

The R field is the branch address specified by the micro-instruction. The 10-bit address branches are treated as in-page branching for theoretical pages of 1024 steps. (i.e., the upper 6 bits of the branch address are the same as that of the current instruction).

### 8. MMMM -- Branch Mask

For the mask branch instructions, these 4 bits in the instruction have the following meaning:

Branch True, Branch False -- MMM specifies what bits in the specified B-bus register are to be tested.

M = 1. test the corresponding bit: if

M = 1, test the corresponding bit; if M = 0, do not test the corresponding bit.

Ŋ

Branch Equal, Branch Not Equal -- MMM is the 4-bit pattern to which the high or low 4 bits of the specified B-Bus register is to be compared.

9. AxAxAxAxAx — Auxiliary Register Field

This field specifies which of the 32 Auxiliary registers is to be used in the Auxiliary -- PC Mini-Instruction. Three mini-instructions (TPA, TAP, and XPA) transfer 16 bits between the program counter (PH, PL) and the specified Aux register (0 - 1F).

10. ± In In -- Increment/Decrement Field

The + In In field specifies whether or not the 16-bit value in the PC's is to be incremented or decremented (by 1, 2, or 3) as it is being transferred to the Auxiliary register (TPA, XPA) or subroutine return stack (TPS).

| + In In<br>+ In In | 0 0 0 0 0 | 001<br>010<br>011<br>100<br>101<br>110 | PC's + 1 → PC's + 2 → PC's + 3 → PC's → PC's → | Aux or stack |

|--------------------------------------------------------------------------------------|-----------|----------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|                                                                                      |           |                                        | $PC's - 2 \rightarrow$                         | Aux or stack                                                                                            |

| + In In                                                                              | =         | 111                                    | $PC^{\dagger}s - 3 \rightarrow$                | Aux or stack                                                                                            |

# E. Timing Sequence

The following timing sequence of events takes place for the 2600 micro-instructions:

# Register and Mini-Instruction Timing Sequence

- For LPI instructions, the PC registers are loaded with the specified value.

- 2. If DD bits specify a Read or Write, the contents of the Data Memory Program Counter (PH, PL) are transferred to the memory control logic to select the address.

- 3. The <u>initial</u> contents of the registers selected by the A-Bus (or Immediate Operand), and the B-Bus fields, and carry bit are gated to the Buses and into the ALU.

- 4. If set carry is specified (CaCa field of Register Instructions), the carry (SH<sub>O</sub>) is set as specified.

- 5. The arithmetic or logical operation is performed in the ALU.

- 6. The results of the arithmetic or logical operation in the ALU is stored in the register specified by the C-Bus field.

- 7. If PC, stack, and Auxiliary Register transfers or exchanges are specified by the instruction, they are done. (TPA, TAP, XPA, TPS, TSP).

- 8. If Auxiliary register  $\pm 1$ ,  $\pm 2$ , or  $\pm 3$  incrementing or decrementing is specified, (e.g., TP+1, XPA-3, XPA+2)  $\pm 1$ ,  $\pm 2$ , or  $\pm 3$  is added with 16-bit of data received by the Auxiliary PC register.

- 9. If a Read or Write is specified, data is read into CH, CL or written from C-Bus (result of ALU operation) to memory.

- If PC incrementing or decrementing is specified by the A-field, PC's are incremented or decremented by 1.

- 11. The Instruction Program Counter (IC's) is incremented by 1.

# Branch Instruction Timing Squence

- 1. For Conditional Branches, the test is made to branch or not branch based on the contents of the B-Bus Register.

- 2. If the test is valid, the branch is made by replacing the low order 10 or full 16-bits of the IC registers with the R instruction operands.

- 3. If the test is not valid, the IC counters are incremented by 1 to get the next instruction.

- (Note --For Subroutine Branches and Subroutine Returns, the address saved in the subroutine stack is the current instruction address + 1. The stack is circular.

- If PC incrementing or decrementing is specified by the A-field, PC's are incremented or decremented by 1 after the branch test is performed. The incrementing will occur whether the test is true or false.

#### F. 2600 Trap Locations

16 control memory locations are reserved as traps (address 8000 through 800F). When a trap condition occurs, normal processing is immediately terminated and an automatic branch is made to the appropriate trap location. At the trap location is a branch instruction which transfers control to the specified microcode routine so that appropriate action can be taken. Presently, the following trap locations are defined:

PECM (parity error in control memory) 8000 ---

8001 RESET

8002 PEDM (parity error in data memory)

8003 ---(power on -- MASTER INITIALIZE) POR

### G. Memory Parity

The 2600 uses odd parity on both control memory and data memory.

### 1. Control Memory Parity

The high order bit of each instruction in control memory is the parity bit; parity is odd. The parity bit of each instruction is generated by software; the SR, WCM instruction writes the 24 bits in the  $\overline{K}$ , PH, and PL (parity and instruction). The WCM instruction does not generate parity.

Instruction parity is checked when fetching an instruction for execution. If there is a parity error, the system will set parity error status bit  $(SH_6) = 1$  and trap to location  $8000_{16}$  in control memory. The address +1 of the instruction with bad parity is pushed into the subroutine return stack.

If the instruction (data) read by a SR, RCM instruction has bad parity, the parity error status bit (SH<sub>6</sub>) is set to 1. No trap is made and the address of the instruction with bad parity is not saved in the stack.

### 2. Data Memory Parity

Odd parity is generated and written by the hardware at the time of a write to data memory.

On a read from data memory, parity is checked on the 16 bits read. If there is a parity error, the parity error status bits (SH $_6$ ) is set to 1. If the parity trap control status bit (SH $_7$ ) is set to 0, the system will trap to location  $8002_{16}$  in control memory. If SH $_7$  = 1, the trap is inhibited. The address of the data with bad parity is not saved in the stack regardless of whether the system traps or not. Also, the PC's may not be the address of the data with bad parity (e.g., XPA, R).

### 3. Parity Status Bits

- SH<sub>6</sub> parity error. Set to 1 whenever bad parity is detected when fetching instructions or reading data.

- SH<sub>7</sub> -- parity trap control. (Data Memory)

- parity error trap for data memory enabled.

- parity error trap for data memory inhibited.

# APPENDIX A

DETAILED DESCRIPTION

OF THE

INSTRUCTION SET

|   |    |   |   |   |   |   |    |    | T |          | T_ |            |            |          |          | ٨ | Δ | A | B        | В | В | . в    |  |

|---|----|---|---|---|---|---|----|----|---|----------|----|------------|------------|----------|----------|---|---|---|----------|---|---|--------|--|

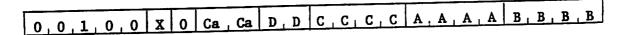

| 0 | .0 | 0 | 0 | 0 | X | 0 | Ca | Ca | D | <u>D</u> | C  | <u>. U</u> | <u>, U</u> | <u> </u> | <u> </u> |   |   |   | <u> </u> |   |   | لــــا |  |

If X=0, the OR of the registers specified by the A and B fields is formed and the result is stored in the register specified by the C field. If X=1, the OR of the register pair specified by the A field is OR'ed with the register pair specified by the B field and the result is stored in the register pair specified by the C field.

Register use in the A, B, and C fields:

```

A: F0 - F7, CL-, CH-, CL, CH, CL+, CH+, +, -

B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy

(1f X = 0) C: F0 - F7, PL, PH, , SL, SH, K, dummy

(1f X = 1) C: F0 - F7, PL, , SL, SH, K, dummy

```

Carry (SH) ) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

D D = 00: no read or write D D = 01: read D D = 10: Write 1 D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If A and/or B and/or C are set to indicate the dummy register, the net result will be:

| A       | ==  | Dummy |      | В | <b>→</b> | C | [Memory] |

|---------|-----|-------|------|---|----------|---|----------|

| В       | =   | Dummy | •    | A | <b>→</b> | C | [Memory] |

| č       | 22  | Dummy | A or | В | <b>→</b> |   | [Memory] |

| A, B    | =   | Dummy |      | 0 | <b>→</b> | C | [Memory] |

| A, C    | =   | Dummy |      | В | <b>→</b> |   | [Memory] |

| B, C    | =   | Dummy |      | A | <b>→</b> |   | [Memory] |

| A, B, C | . = | Dummy |      | 0 | <b>→</b> |   | [Memory] |

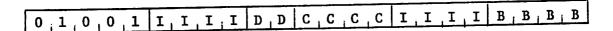

| 0 0 0 0 1 X 0 | Ca Ca D D C C C C A A A A B B B B |

|---------------|-----------------------------------|

|               | I A A B B B B                     |

If X = 0, the exclusive OR of the registers specified by the A and B fields is formed. The results are stored in the register specified by the C field. If X = 1, the register pair specified by the A field is exclusive OR'ed with the register pair specified in the B field and the result is stored in the register pair specified by the C field.

Register use in the A, B, and C fields:

```

A: F0 - F7, CL-, CH-, CL, CH, CL+, CH+, +, -

B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy

(1f X = 0) C: F0 - F7, PL, PH, , SL, SH, K, dummy

(1f X = 1) C: F0 - F7, PL, , SL, SH, K, dummy

```

Carry (SH<sub>0</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction

CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

D D = 00: no read or write D D = 01: read D D = 10: Write 1 D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If A and/or B and/or C are set to indicate the dummy register, the net result will be:

| A<br>B<br>C<br>A,<br>B, | C<br>C | C | :<br>::<br>::<br>:: | Dummy Dummy Dummy Dummy Dummy Dummy | B<br>A<br>A (+) B<br>O<br>B<br>A | + + + + + + | C<br>C | [Memory]<br>[Memory]<br>[Memory]<br>[Memory]<br>[Memory] |

|-------------------------|--------|---|---------------------|-------------------------------------|----------------------------------|-------------|--------|----------------------------------------------------------|

| A,                      | В,     | C | =                   |                                     | 0                                | <b>→</b>    |        | [Memory]                                                 |

|     |       |     |     |   |   |   |    |    |   |   |   |   |     | _ |   |   |   |     | _  |   |    | _ |

|-----|-------|-----|-----|---|---|---|----|----|---|---|---|---|-----|---|---|---|---|-----|----|---|----|---|