# ARCHIVING CARTRIDGE TAPE DRIVE

Models:

2229

6529

2529V

#### PREFACE

This document is the Standard (STD) Maintenance Manual for the Wang Archiving Cartridge Tape Drive. It is organized in accordance with the approved STD outline established at the Field/Home Office Publications meetings conducted on September 14th and 15th, 1982. The scope of this manual reflects the type of maintenance philosophy selected for this product (swap unit, printed circuit assembly, chip level or any combination thereof).

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with instructions to operate, troubleshoot and repair the Archiving Cartridge Tape Drive. It will be updated on a regular schedule.

## Second Edition (October, 1983)

This edition of the Archiving Cartridge Tape Drive STD manual obsoletes document no. 729-1184. The material in this document may only be used for the purpose stated in the Preface. Updates and/or changes to this document will be published as Product Service Notices (PSN's) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

© Copyright WANG Labs., Inc. 1983

## TABLE OF CONTENTS

| Chapter |             |                                                 | Page |

|---------|-------------|-------------------------------------------------|------|

|         | LIST OF ILL | USTRATIONS                                      | vii  |

|         | LIST OF TAB | LES                                             | viii |

| 1       | INTRODUCTIO | N                                               | 1-1  |

|         | 1.1         | Purpose & Scope                                 | 1-1  |

|         | 1.2         | Applicable Documents                            | 1-1  |

|         | 1.3         | General Description                             | 1-1  |

|         | 1.4         | Specifications                                  | 1-2  |

| 2       | THEORY OF O | PERATION                                        | 2-1  |

|         | 2.1         | Introduction                                    | 2-1  |

|         | 2.2         | The OIS/VS Interface Board                      | 2-1  |

|         | 2.2.1       | Controls and Indicators                         | 2-5  |

|         | 2.2.2       | Data Link                                       | 2-6  |

|         | 2.2.3       | Z80 Central Processor Unit                      | 2-9  |

|         | 2.2.4       | Direct Memory Access Logic                      | 2-11 |

|         | 2.2.5       | Counter Timer Chip                              | 2-12 |

|         | 2.2.6       | Memory                                          | 2-14 |

|         | 2.2.6.1     | Random Access Memory                            | 2-14 |

|         | 2.2.6.2     | Power-up Diagnostic PROM                        | 2-14 |

|         | 2.2.7       | Tape Interface                                  | 2-16 |

|         | 2.2.7.1     | Tape Commands                                   | 2-19 |

|         | 2.2.7.2     | Status Latches                                  | 2-22 |

|         | 2.3         | The 2200 Interface Assembly                     | 2-24 |

|         | 2.3.1       | 2200/Controller Interface                       | 2-26 |

|         | 2.3.1.1     | Port B Data Transfers (DMA mode)                | 2-26 |

|         | 2.3.1.2     | 2200/Controller Data Transfers (Interrupt Mode) | 2-26 |

|         | 2.3.2       | Tape Interface                                  | 2-26 |

|         | 2.3.2.1     | Control Signals                                 | 2-27 |

|         | 2.3.2.2     | Command Transfers to the Formatter              | 2-27 |

|         | 2.3.2.3     | Parameter Transfers to the Host                 | 2-28 |

|         | 2.3.2.4     | Data Transfers to the Formatter (Write)         | 2-28 |

|         | 2.3.2.5     | Data Transfers to the Host (Read)               | 2-29 |

|         | 2.3.3       | Controller Operations                           | 2-29 |

|         | 2.3.3.1     | The Identity Group                              | 2-29 |

# TABLE OF CONTENTS (continued)

| Chapter |           |                                               | Page |

|---------|-----------|-----------------------------------------------|------|

|         | 2.3.3.2   | The Positioning Group                         | 2-30 |

|         | 2.3.3.3   | The Data Transfer Group                       | 2-30 |

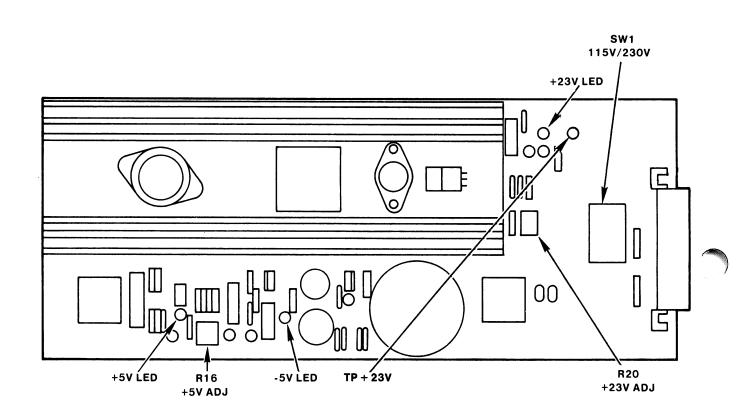

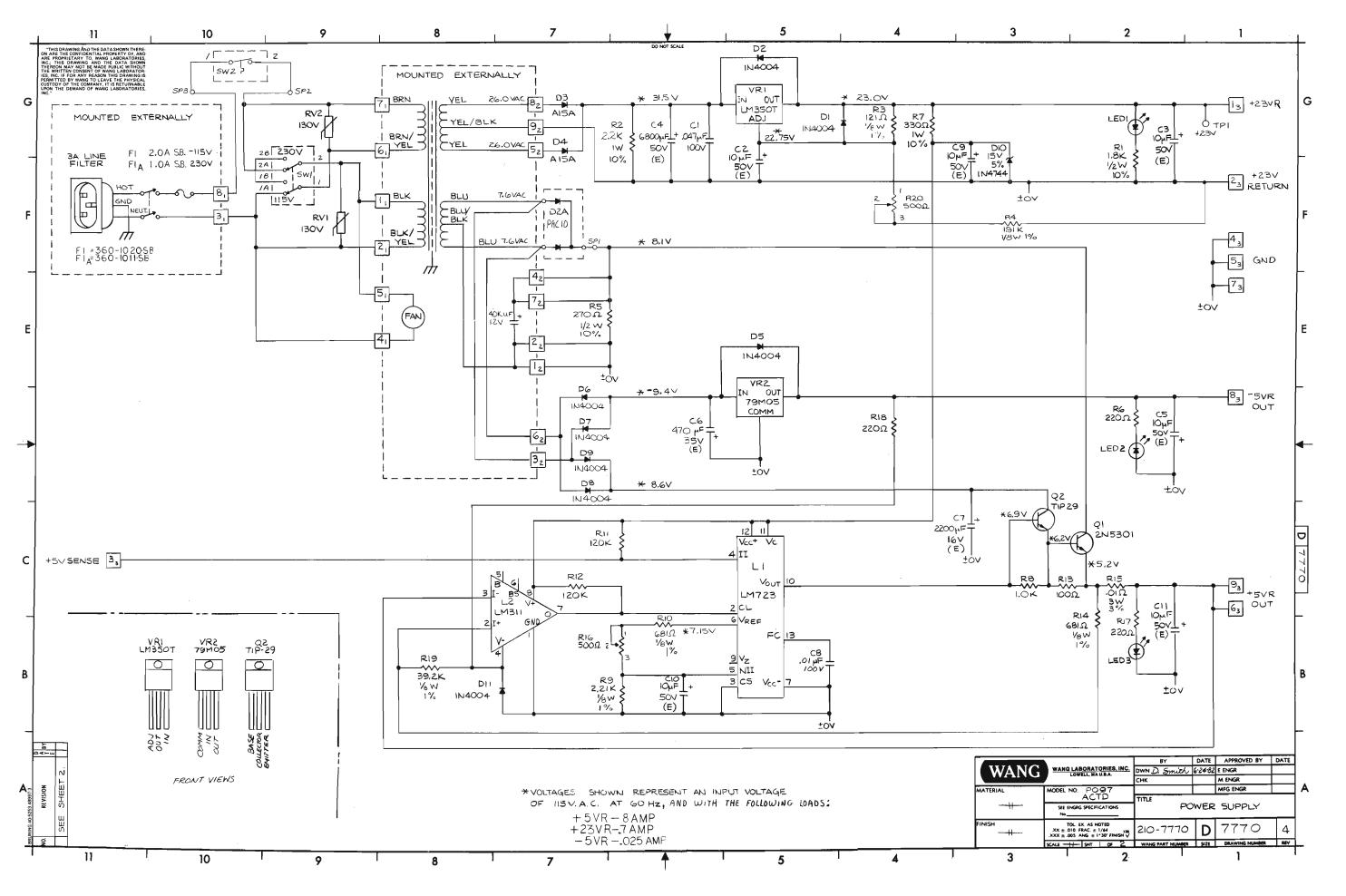

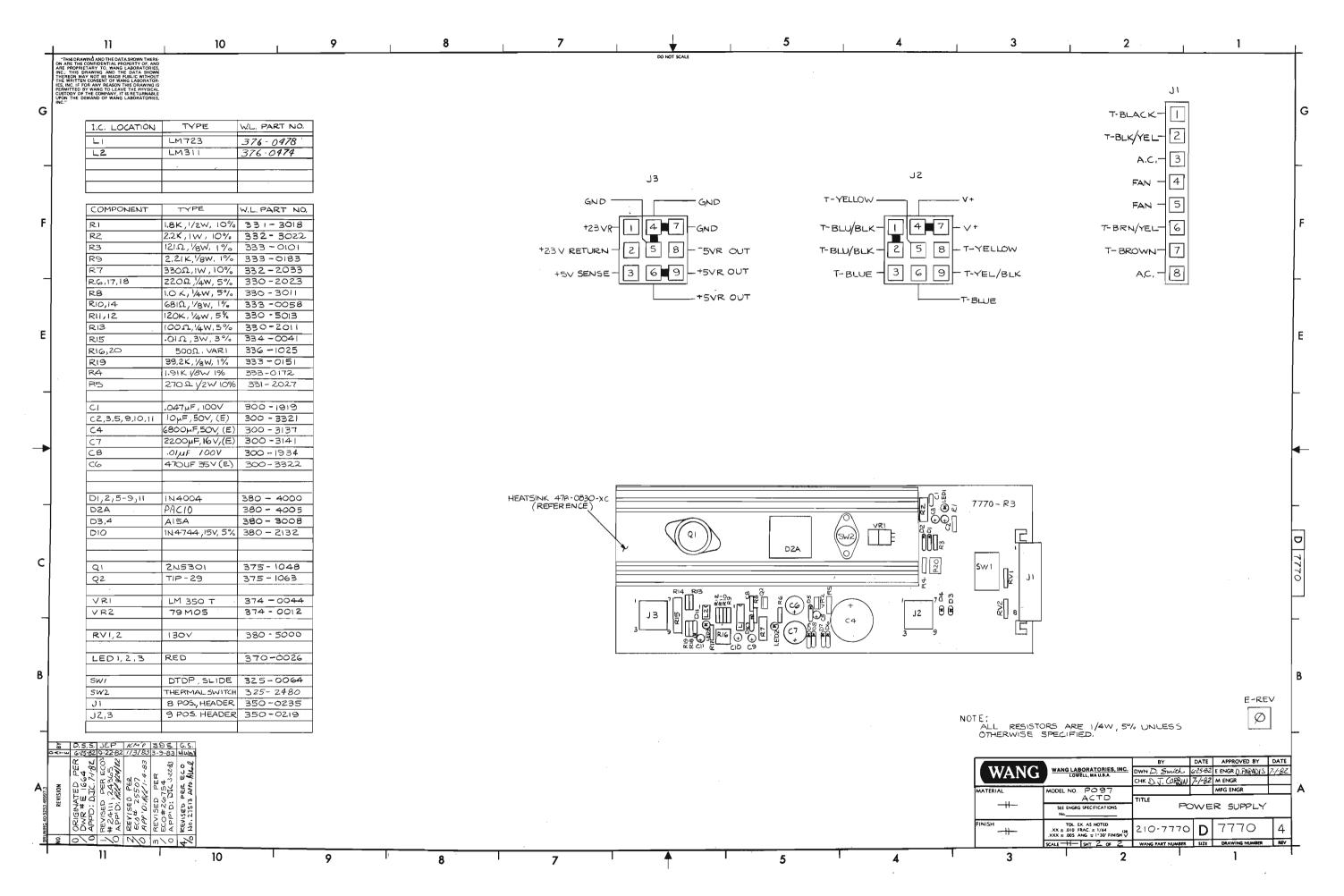

|         | 2.4       | Tape Drive Power Supply                       | 2-31 |

|         | 2.4.1     | The 23V Supply                                | 2-31 |

|         | 2.4.2     | The -5V Supply                                | 2-31 |

|         | 2.4.3     | The +5V Supply                                | 2-32 |

|         | 2.4.4     | Power Supply Specifications                   | 2-32 |

|         | 2.4.4.1   | +5V Supply                                    | 2-32 |

|         | 2.4.4.2   | +23V Supply                                   | 2-32 |

|         | 2.4.4.3   | -5V Supply                                    | 2-32 |

|         | 2.4.4.4   | AC Input                                      | 2-32 |

| 3       | OPERATION |                                               | 3-1  |

|         | 3.1       | Introduction                                  | 3-1  |

|         | 3.2       | Controls, Indicators and External Connections | 3-1  |

|         | 3.3       | Initial Turn-on Procedure                     | 3-4  |

|         | 3.4       | Handling the Tape Cartridge                   | 3-4  |

|         | 3.5       | Tape Utilities                                | 3-5  |

|         | 3.5.1     | 2229 Utilities                                | 3-5  |

|         | 3.5.1.1   | Backup Platter From Tape                      | 3-6  |

|         | 3.5.1.2   | Recover Platter From Tape                     | 3-6  |

|         | 3.5.1.3   | Recover File From Platter Backup              | 3-6  |

|         | 3.5.1.4   | Create Reference File                         | 3-6  |

|         | 3.5.1.5   | Backup Files To Tape                          | 3-6  |

|         | 3.5.1.6   | Recover Files From Tape                       | 3-6  |

|         | 3.5.1.7   | Tension Tape Cartridge                        | 3-6  |

|         | 3.5.2     | 6529 Utilities                                | 3-7  |

|         | 3.5.2.1   | Initialize Tape                               | 3-7  |

|         | 3.5.2.2   | Backup to Tape                                | 3-7  |

|         | 3.5.2.3   | Restore From Tape                             | 3-7  |

|         | 3.5.2.4   | Copy to Tape                                  | 3-7  |

|         | 3.5.2.5   | Copy From Tape                                | 3-7  |

|         | 3.5.3     | 2529V Utilities                               | 3-7  |

|         | 3.5.3.1   | Tapeinit                                      | 3-8  |

|         | 3.5.3.2   | Backup                                        | 3-8  |

# TABLE OF CONTENTS (continued)

| Chapter |                            |                                                                 | Page         |

|---------|----------------------------|-----------------------------------------------------------------|--------------|

| 4       | INSTALLATION               |                                                                 | 4-1          |

|         | 4.1                        | Unpacking                                                       | 4-1          |

|         | 4.2                        | Minimum Revision Levels                                         | 4-1          |

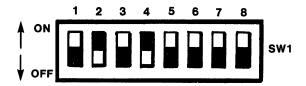

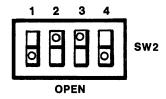

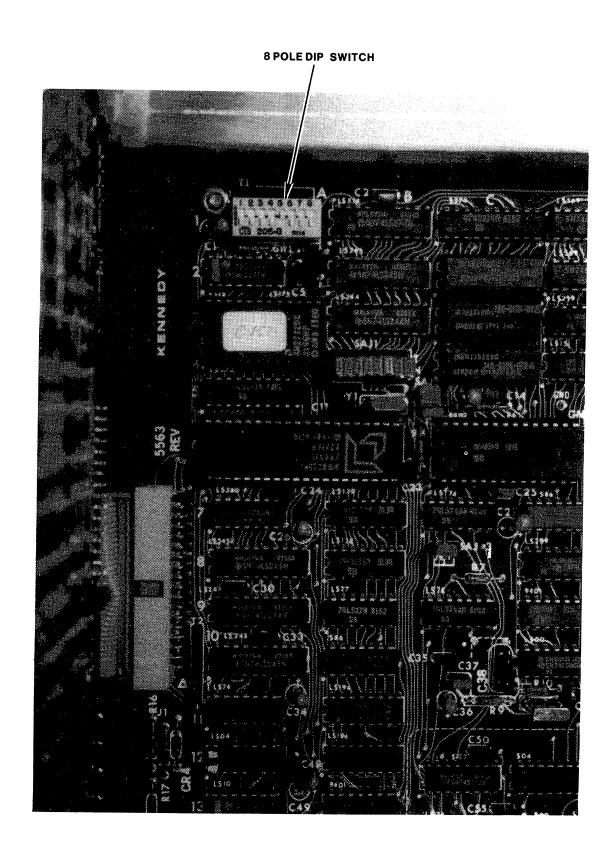

|         | 4.3                        | Switch Settings                                                 | 4-2          |

|         | 4.3.1                      | Model 6529/2529V                                                | 4-2          |

|         | 4.3.2                      | Model 2229                                                      | 4-5          |

|         | 4.4                        | Voltage Checks                                                  | 4-5          |

|         | 4.5                        | System Interconnections                                         | 4-5          |

|         | 4.5.1                      | Model 2229                                                      | 4-5          |

|         | 4.5.2                      | Model 6529/2529V                                                | 4-5          |

|         | 4.6<br>4.7                 | Power-up Procedure<br>Software Loading                          | 4-10<br>4-10 |

| 5       | DREVENTIVE AND             | CORRECTIVE MAINTENANCE                                          | 5-1          |

| J       |                            |                                                                 |              |

|         | 5.1                        | Preventive Maintenance                                          | 5-1          |

|         | 5.1.1                      | Daily Check                                                     | 5-1          |

|         | 5.1.2                      | Cleaning                                                        | 5-1          |

|         | 5.1.2.1                    | Head Cleaning                                                   | 5-1          |

|         | 5.1.2.2                    | Other Cleaning                                                  | 5-1          |

|         | 5.1.3                      | Routine Adjustments                                             | 5-2          |

|         | 5.1.4                      | Lubrication                                                     | 5-2          |

|         | 5.1.5                      | Head Wear                                                       | 5-2          |

|         | 5.1.6                      | Periodic Inspection                                             | 5-2          |

|         | 5.2                        | Corrective Maintenance                                          | 5-2          |

|         | 5.2.1                      | Disassembly Procedures                                          | 5-2          |

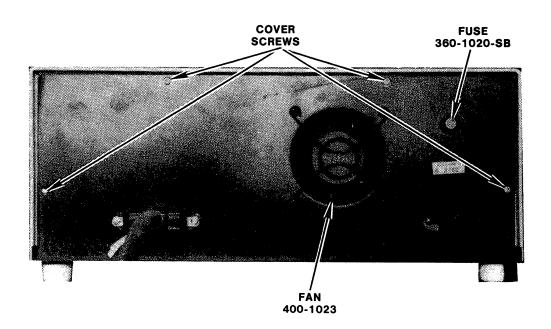

|         | 5.2.1.1                    | Cabinet Cover                                                   | 5-2          |

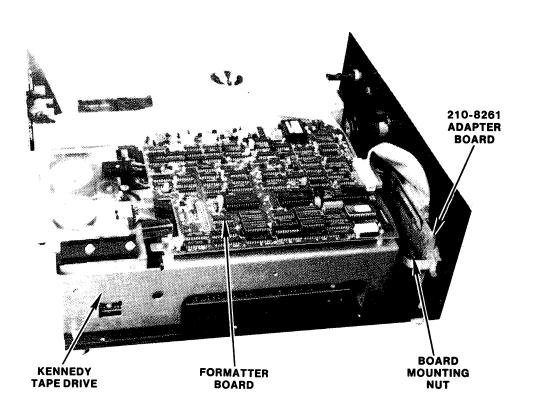

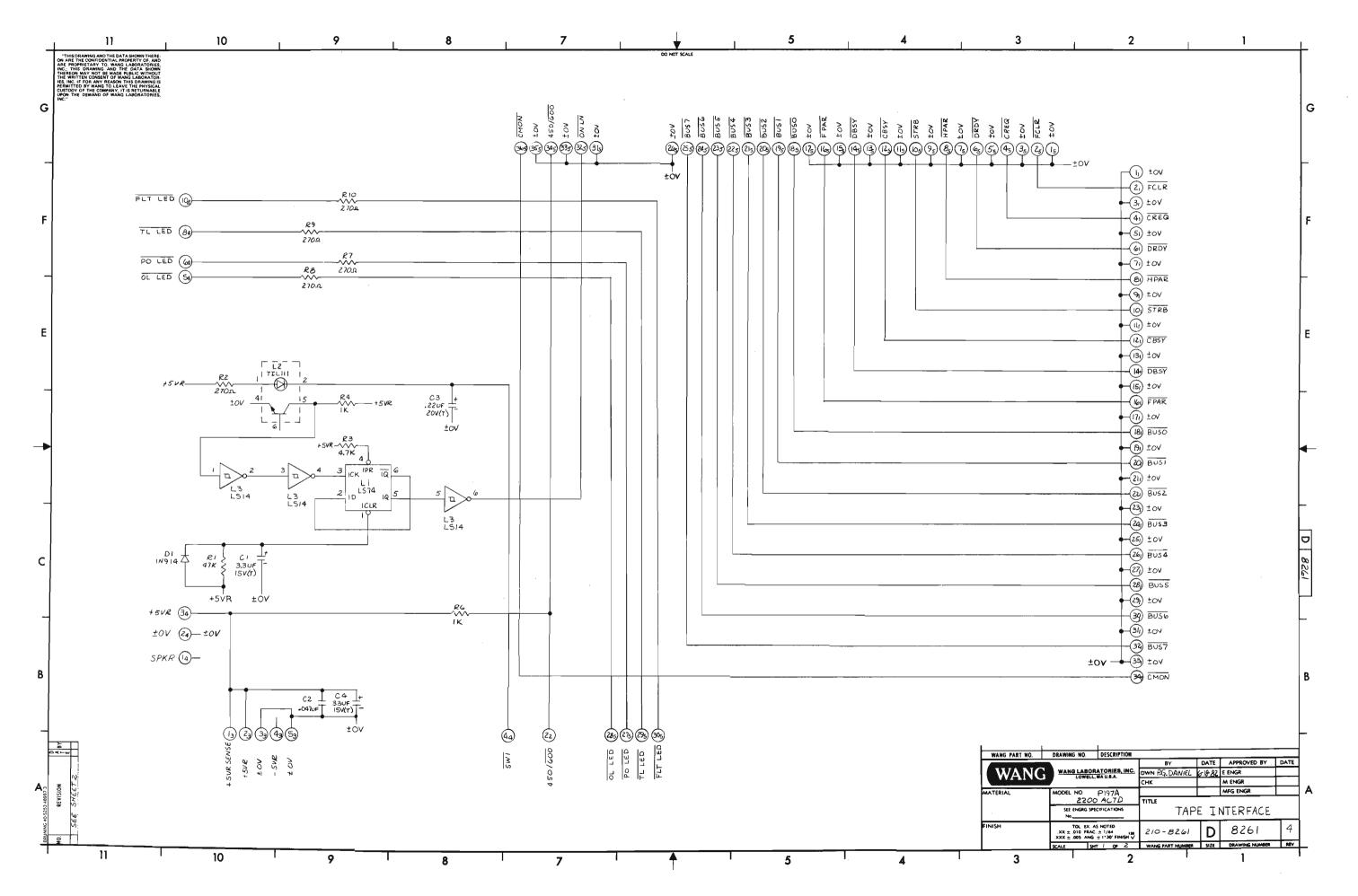

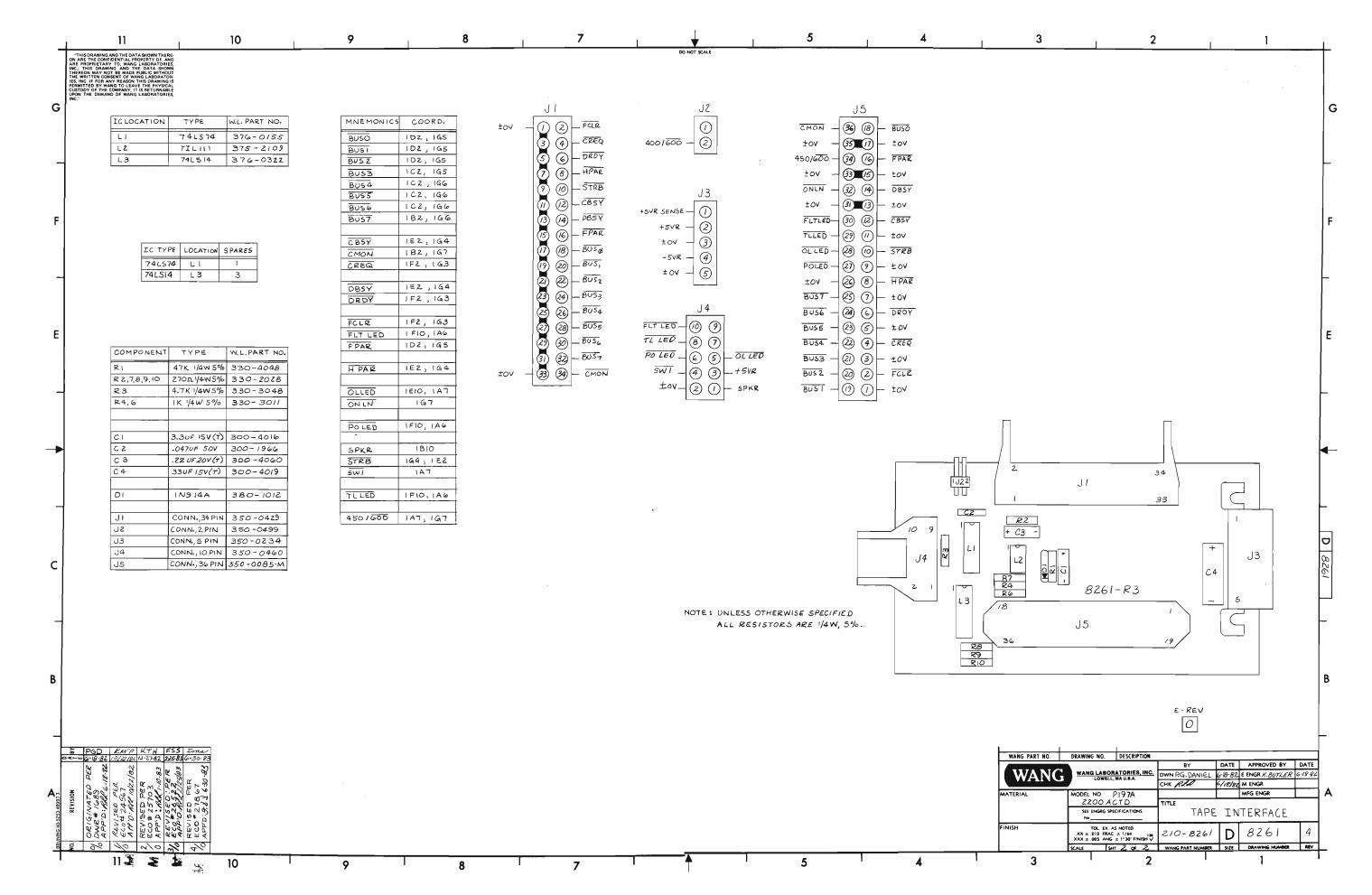

|         | 5.2.1.2                    | 210-8261 Adapter Board (Model 2229 only)                        | 5-2<br>5-4   |

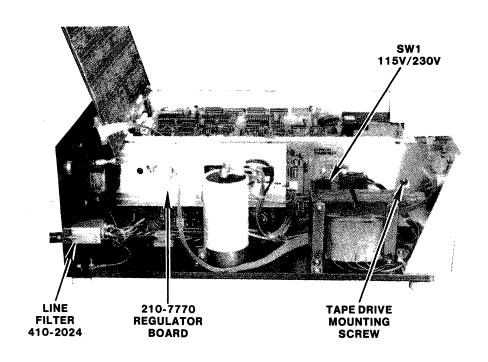

|         | 5.2.1.3                    | 210-7770 Regulator Board                                        | _            |

|         | 5.2.1.4                    | Control Panel                                                   | 5-4<br>5-4   |

|         | 5.2.1.5                    | Loudspeaker                                                     |              |

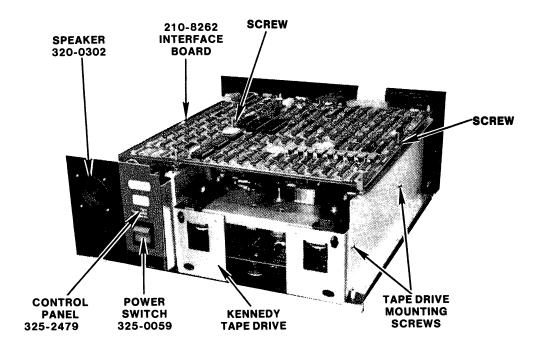

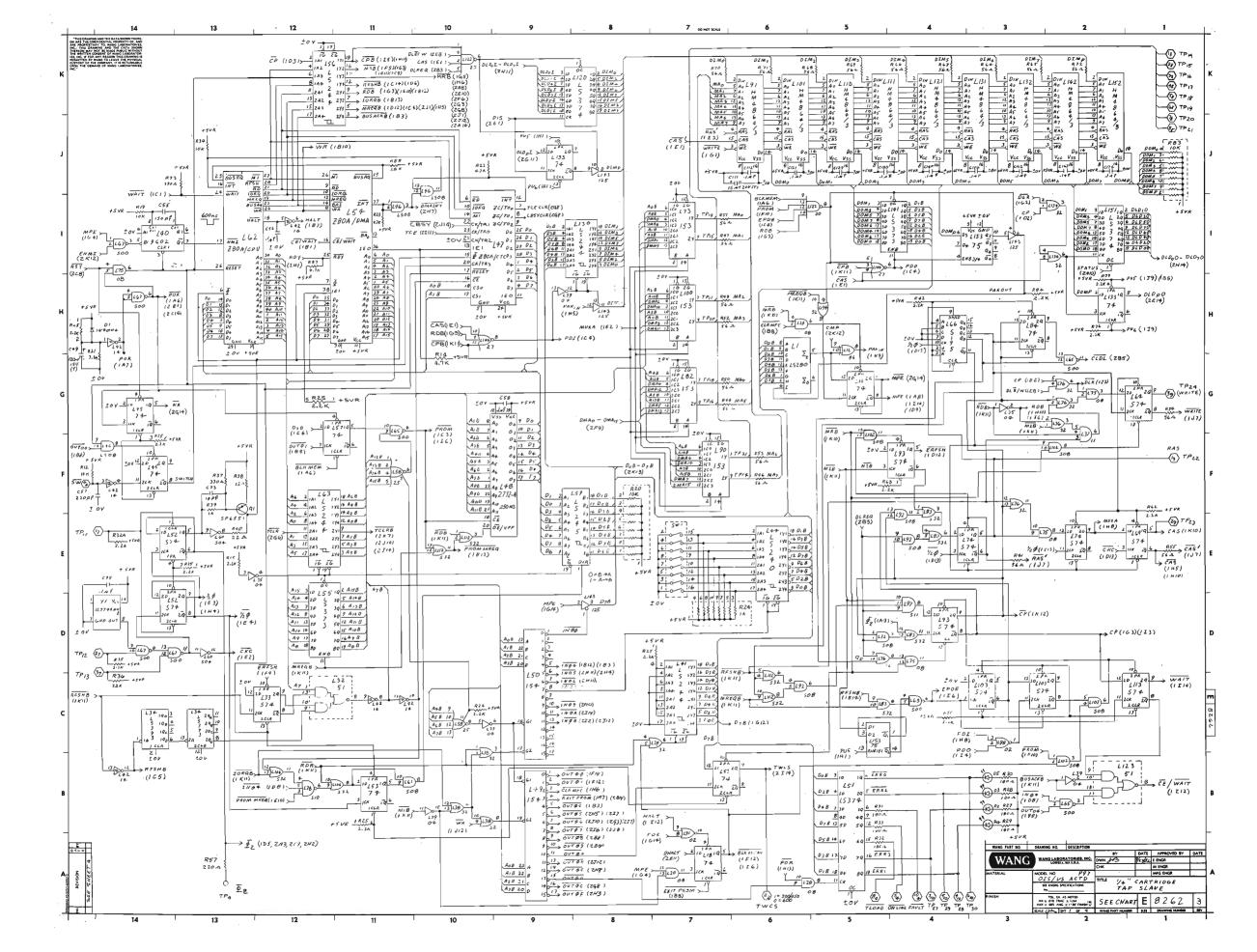

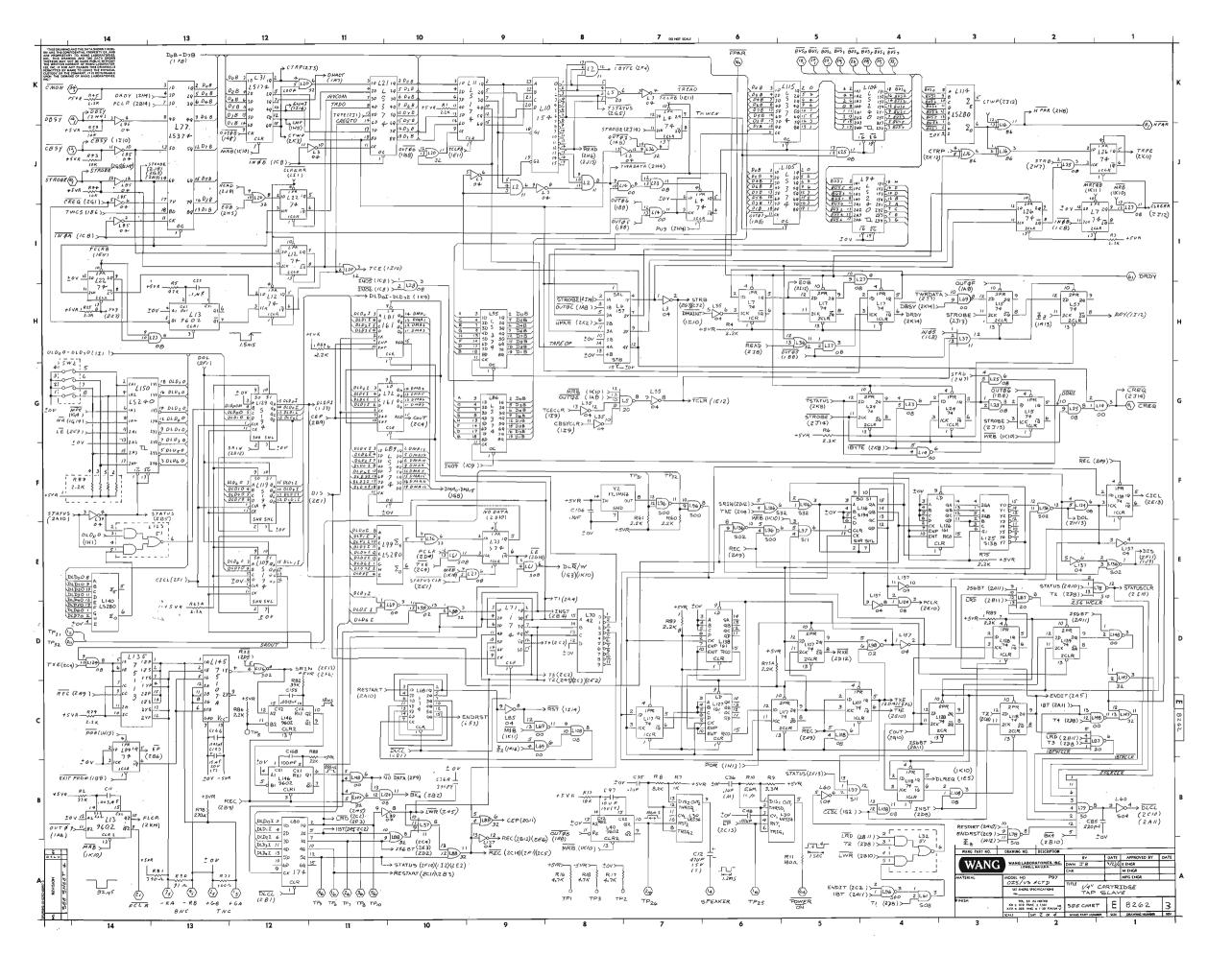

|         | 5.2.1.6                    | 210-8262 Interface Board (Model 6529/2529 only)                 | 5-4          |

|         | 5.2.1.7                    | Fan                                                             | 5-4<br>5-4   |

|         | 5.2.1.8                    | Kennedy Tape Drive (278-4029)                                   | 5-4<br>5-8   |

|         | 5.2.1.8.1                  | Kennedy Parts Replacement                                       | 5-8          |

|         | 5.2.1.8.1.1<br>5.2.1.8.1.2 | Formatter Board Replacement EOT/BOT Infrared Sensor replacement | 5-8          |

|         | 5.2.1.8.1.3                |                                                                 | 5-8          |

|         | 5.2.1.8.1.4                | Capstan Motor Replacement Magnetic Head Replacement             | 5-11         |

|         | 5.2.1.8.1.5                | Interlock Assembly Replacement                                  | 5-11         |

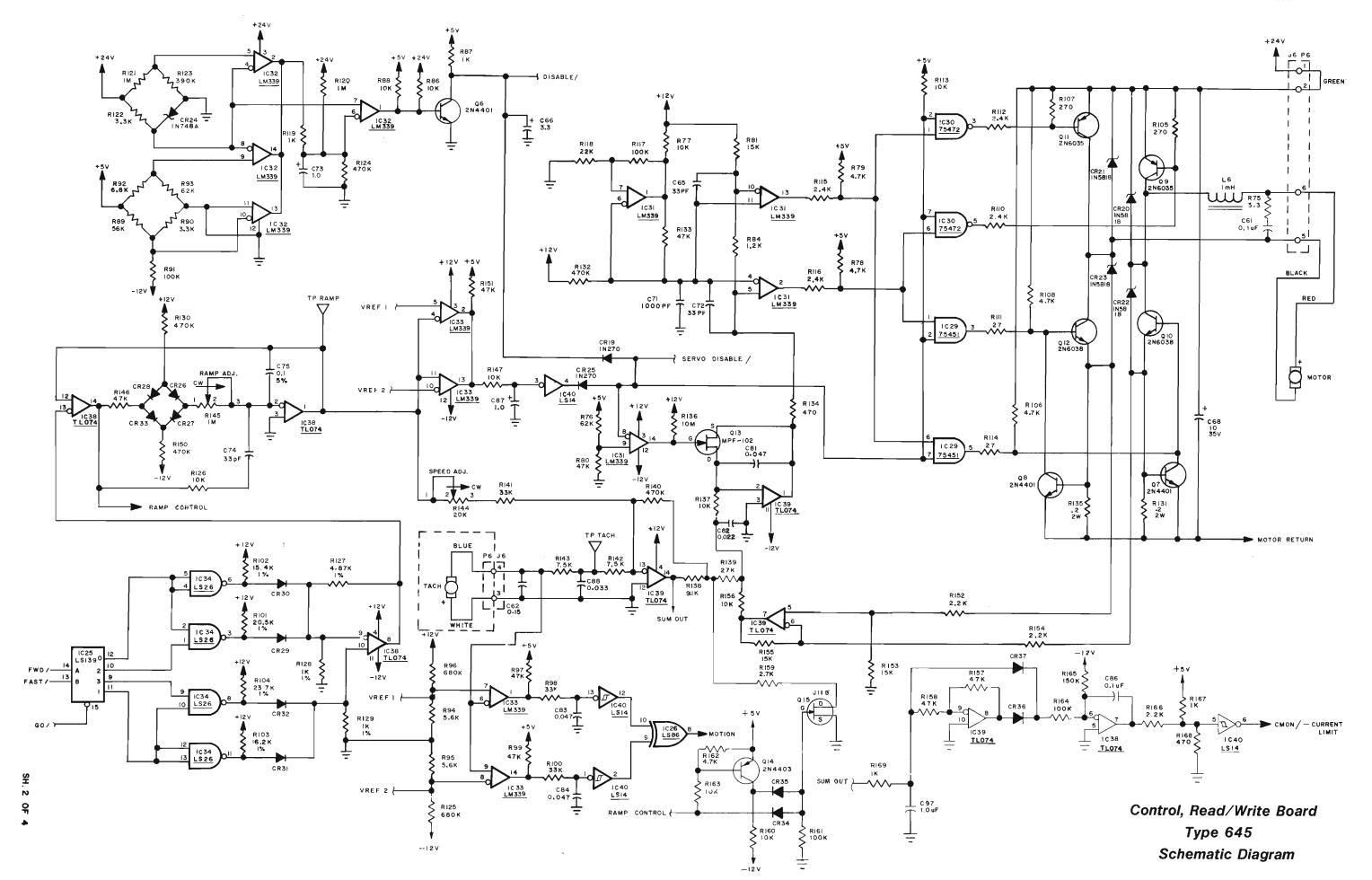

|         | 5.2.1.8.1.6                | Read/Write Board Replacement                                    | 5-11         |

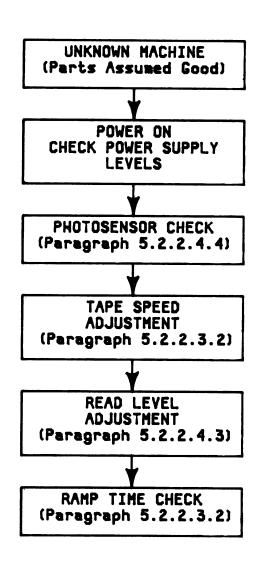

|         | 5.2.2                      | Diagnostics and Adjustments                                     | 5-11         |

|         | 5.2.2.1                    | General                                                         | 5-11         |

|         | 5.2.2.2                    | On-line Diagnostics                                             | 5-11         |

|         | 5.2.2.3                    | Off-line Diagnostics                                            | 5-11         |

|         | 5.2.2.3.1                  | General                                                         | 5-11         |

|         | 5.2.2.3.2                  | Tape Drive Diagnostics                                          | 5-14         |

|         | 5.2.2.3.3                  | Formatter Diagnostics                                           | 5-15         |

## TABLE OF CONTENTS (continued)

| Chapter | •                      |                                                                                                    | Page         |

|---------|------------------------|----------------------------------------------------------------------------------------------------|--------------|

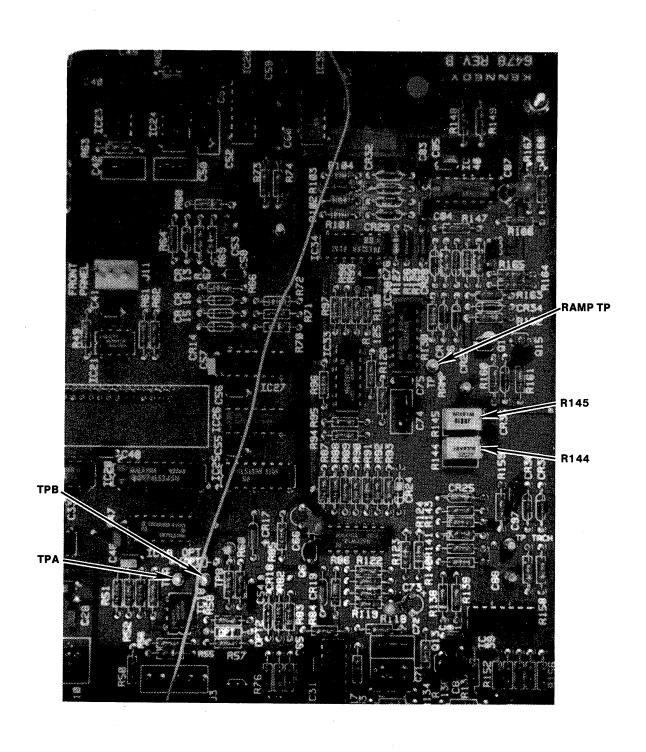

|         | 5.2.2.4<br>5.2.2.4.1   | Formatter and Deck Adjustment Procedures<br>Formatter VCO Center Frequency Adjustment<br>Procedure | 5-17<br>5-17 |

|         | 5.2.2.4.2              | Formatter Integrator Offset Adjustment                                                             | 5-19         |

|         | 5.2.2.4.3<br>5.2.2.4.4 | Recorder Read Amplitude Adjustment Procedure<br>Infrared Sensor Check                              | 5-19<br>5-19 |

|         | 5.2.2.4.5              | Interlock Switch Check and Adjustment                                                              | 5-20         |

| 6       | SCHEMATICS             |                                                                                                    | 6-1          |

| 7       | ILLUSTRATED 1          | PARTS BREAKDOWN                                                                                    | 7-1          |

| 8       | TROUBLE SHOOT          | TING                                                                                               | 8-1          |

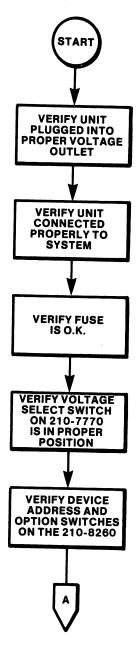

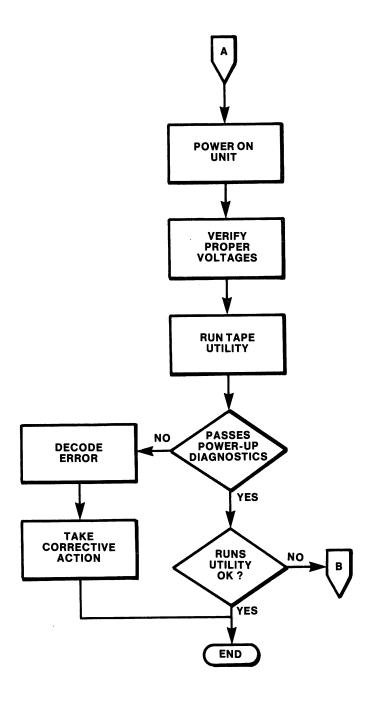

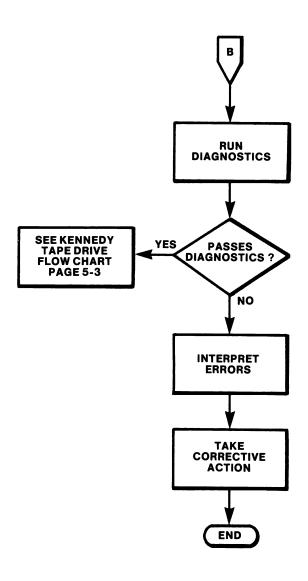

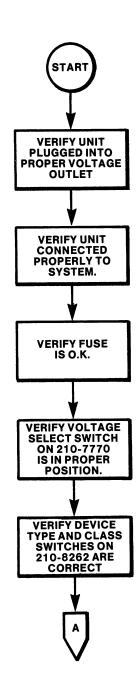

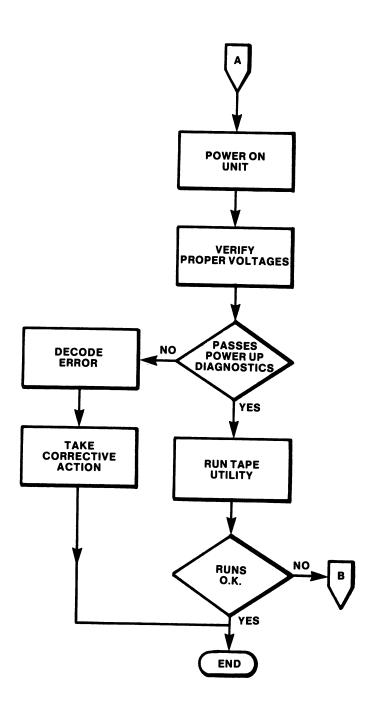

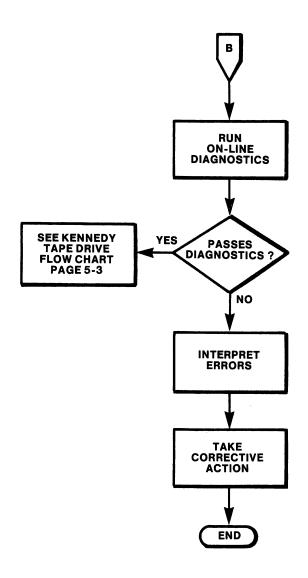

|         | 8.1<br>8.2             | Troubleshooting Flow Diagrams<br>Diagnostics                                                       | 8-1<br>8-7   |

## LIST OF ILLUSTRATIONS

| Number       | Title                                                          | Page         |

|--------------|----------------------------------------------------------------|--------------|

|              |                                                                | 1.2          |

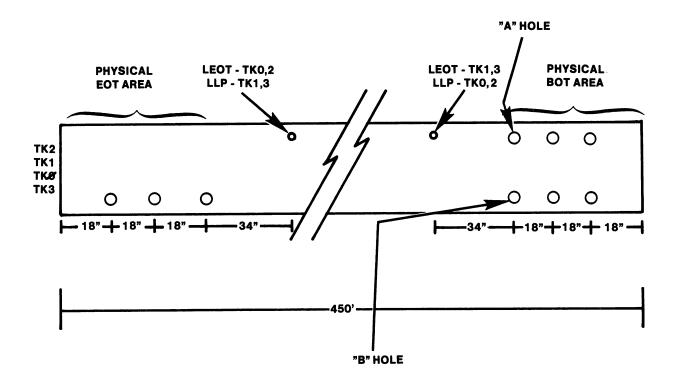

| 1-1          | EOT/BOT Areas on Serial Serpentine Recorded Tape               | 1-3          |

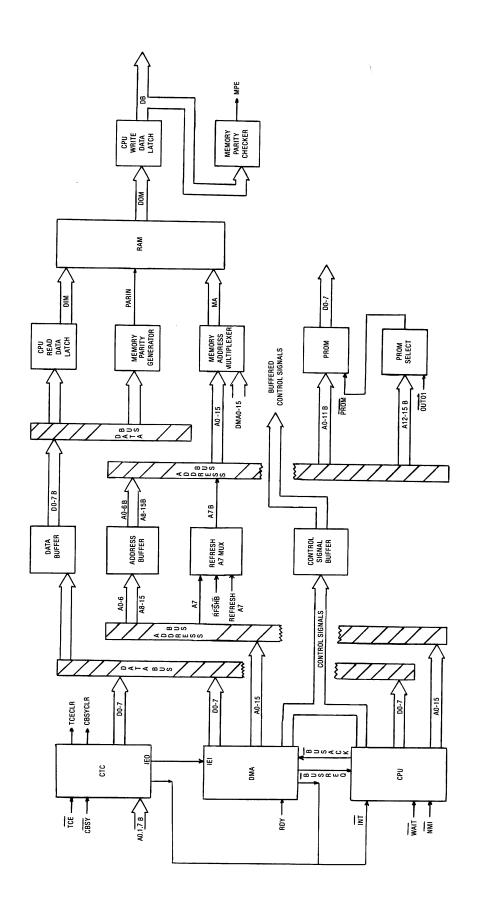

| 2-1          | OIS/VS Interface Block Diagram                                 | 2-2          |

| 2-2          | Data Link Receive Block Diagram                                | 2-7          |

| 2-3          | Data Link Transmit Block Diagram                               | 2-8          |

| 2-4          | CPU, DMA, CTC, PROM and RAM Block Diagram                      | 2-10         |

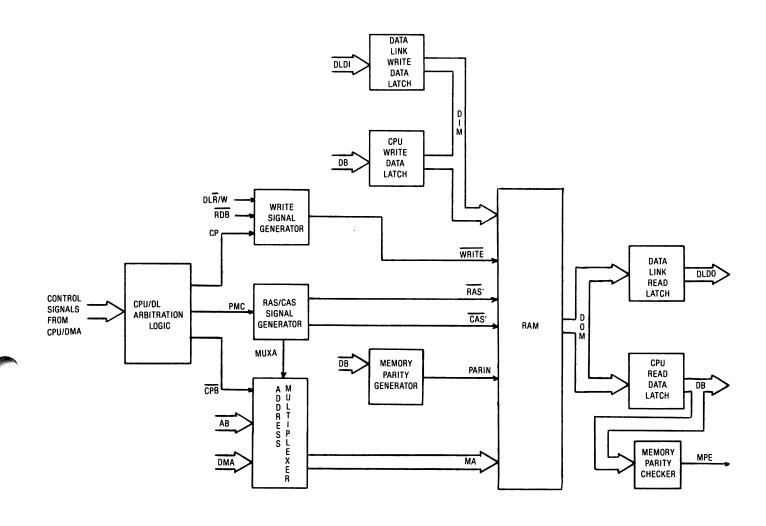

| 2-5          | Block Diagram of Data Paths to and from RAM                    | 2-15         |

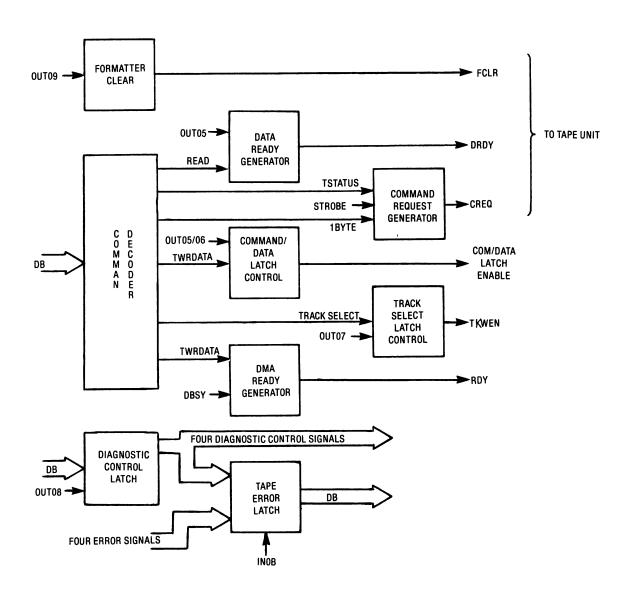

| 2-6          | Tape Interface Control Block Diagram                           | 2-17         |

| 2-7          | Tape Interface Receive Data Path Block Diagram                 | 2-18         |

| 2-8          | Tape Interface Transmit Data Path Block Diagram                | 2-18         |

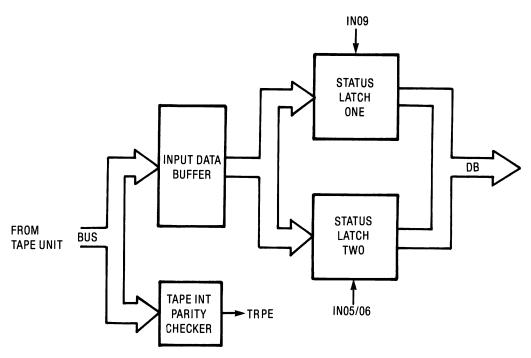

| 2-9          | Block Diagram of 2200 Interface Assembly                       | 2-25         |

| 3-1          | Front Panel                                                    | 3-2          |

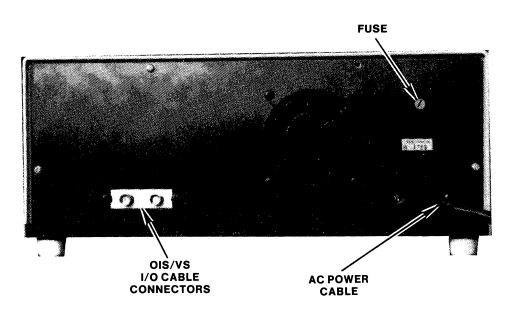

| 3-2          | Rear Panel - Model 2229                                        | 3-2<br>3-3   |

| 3-3          | Rear Panel - Model 6529/2529                                   | 3-3<br>3-3   |

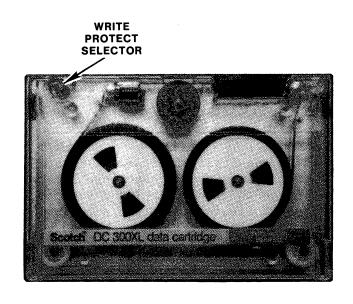

| 3-4          | Tape Cartridge                                                 | 3-3<br>4-3   |

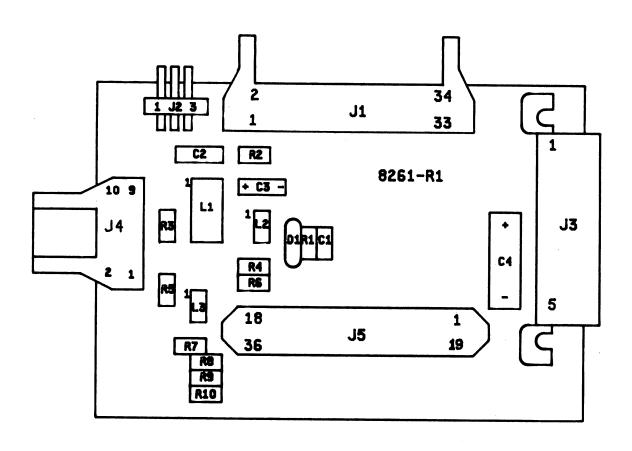

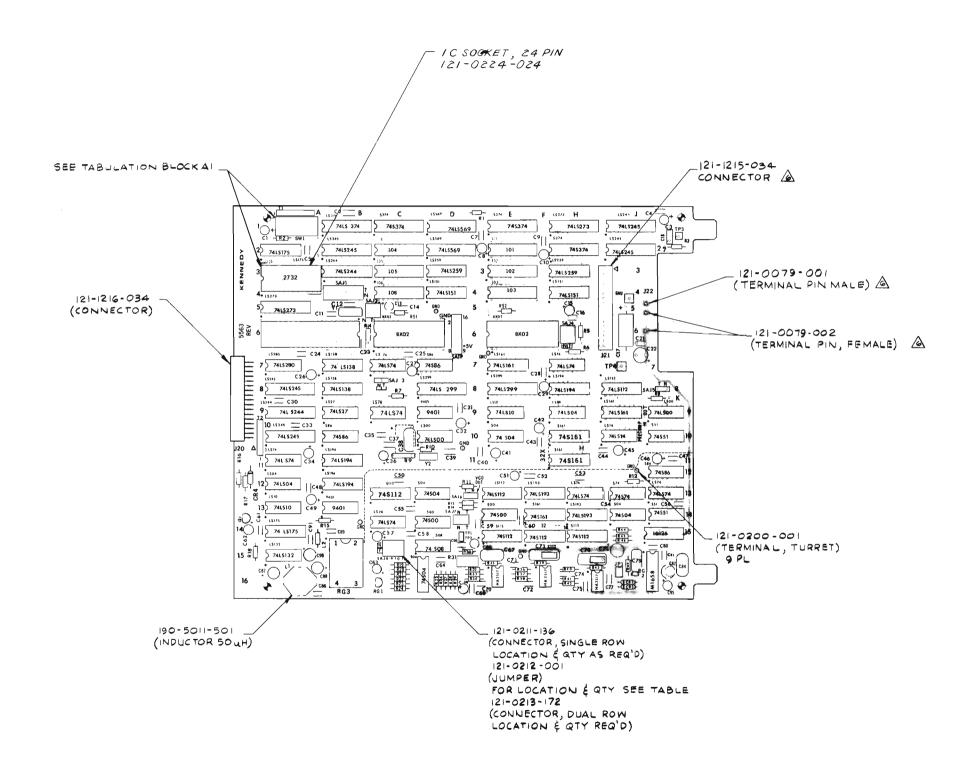

| 4-1          | 210-8262 Interface Board                                       | 4-3<br>4-4   |

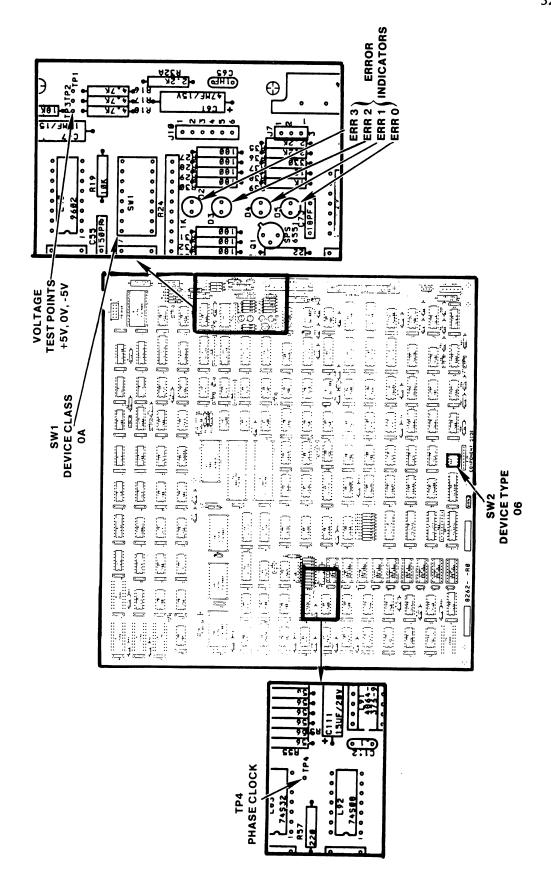

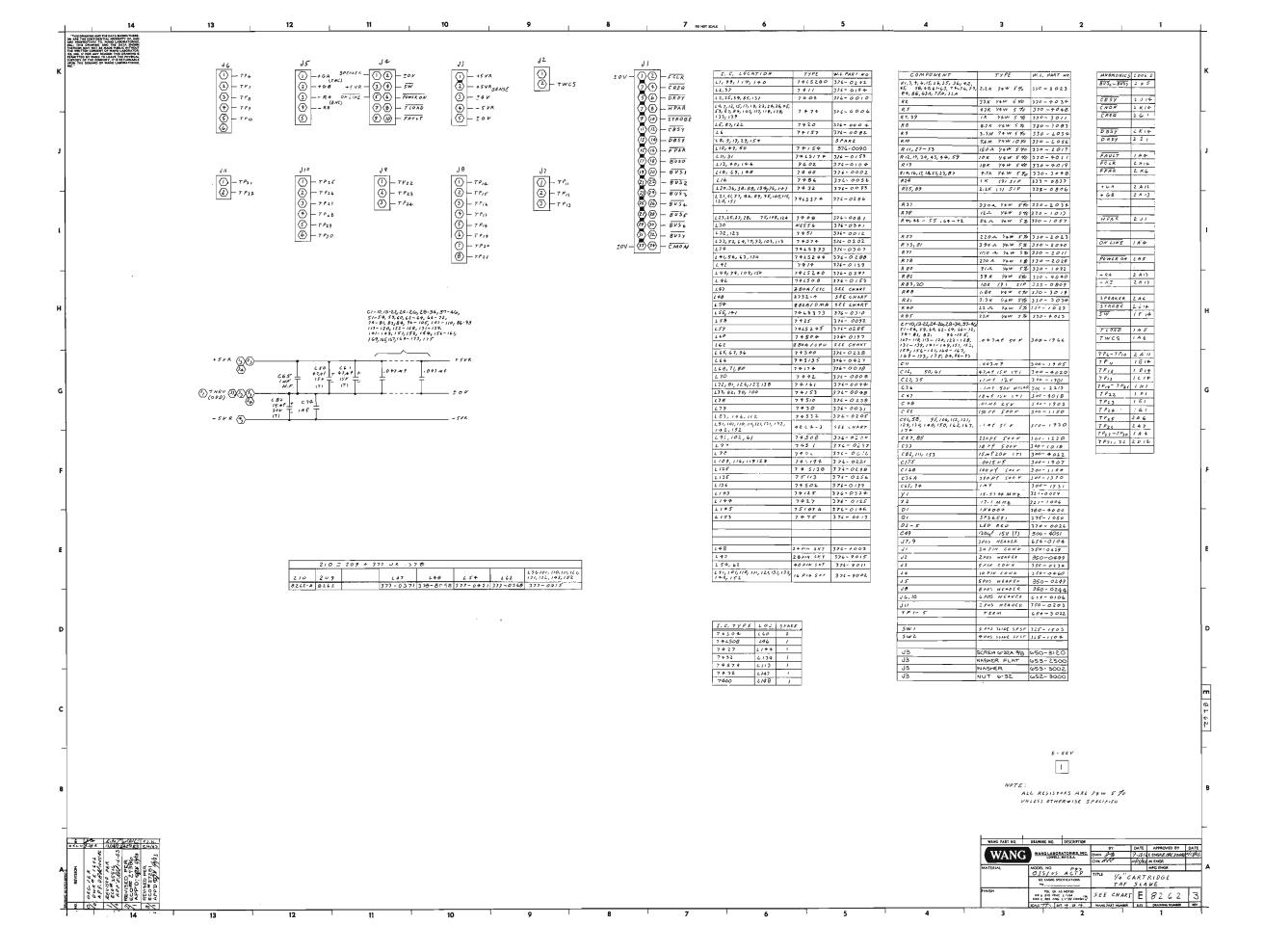

| 4-2          | 210-7770 Regulator Board                                       | 4-4<br>4-6   |

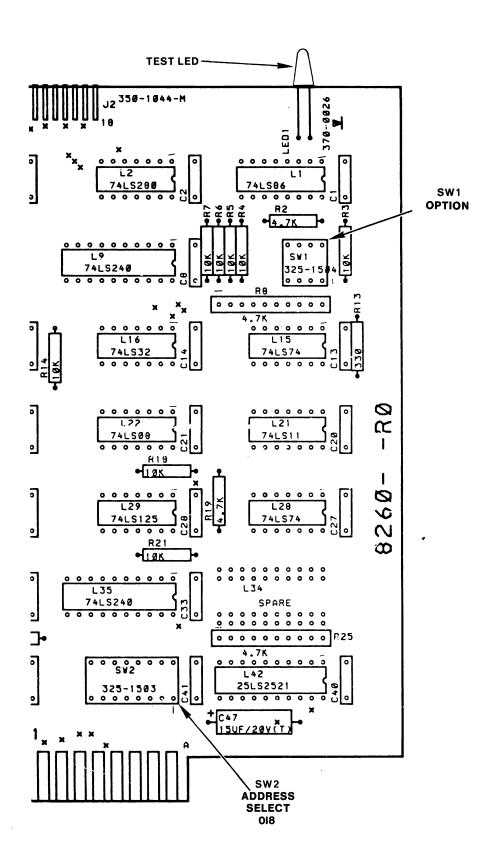

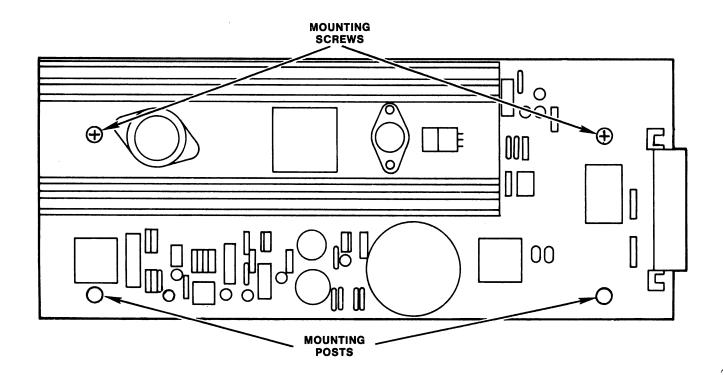

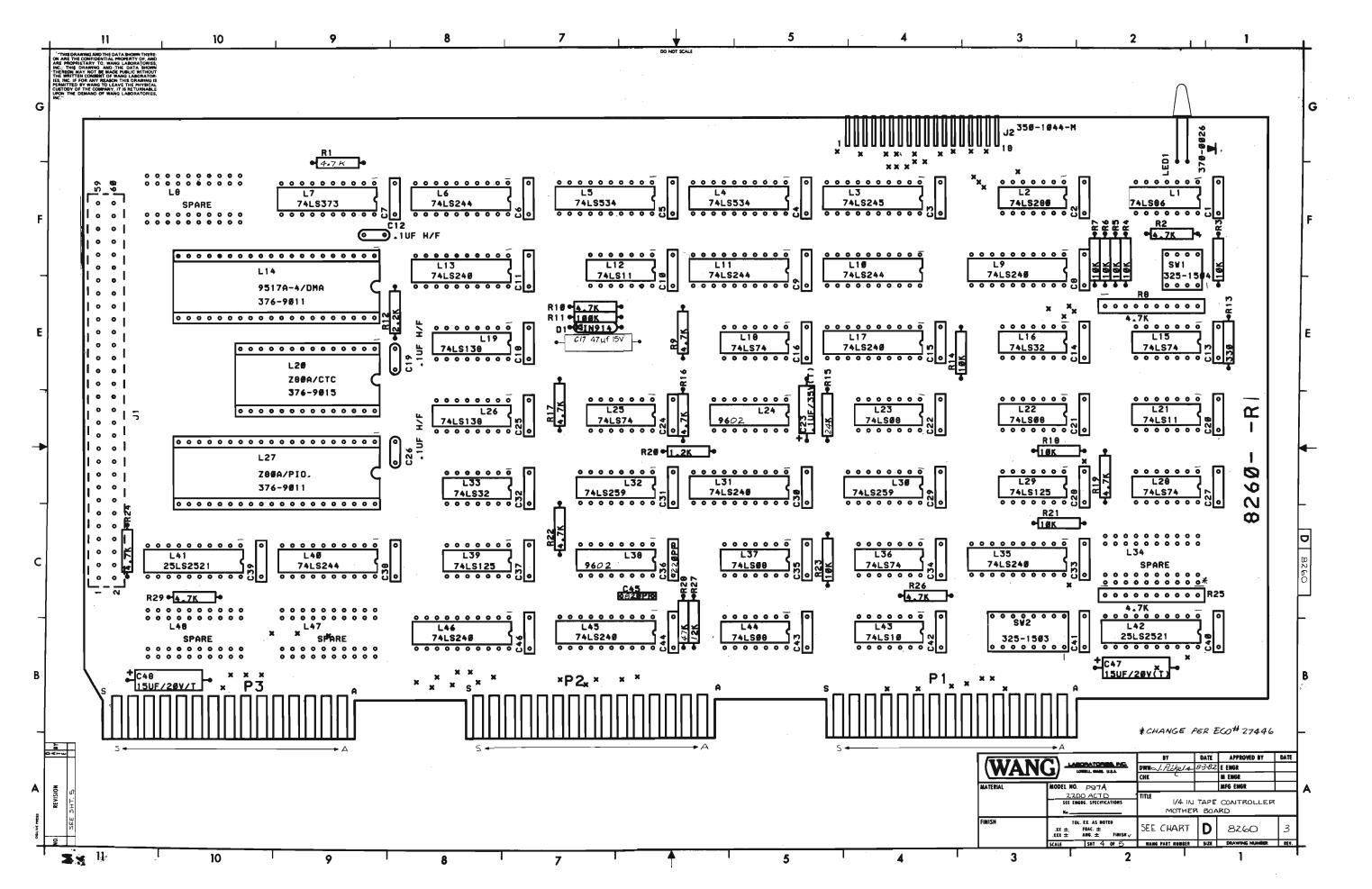

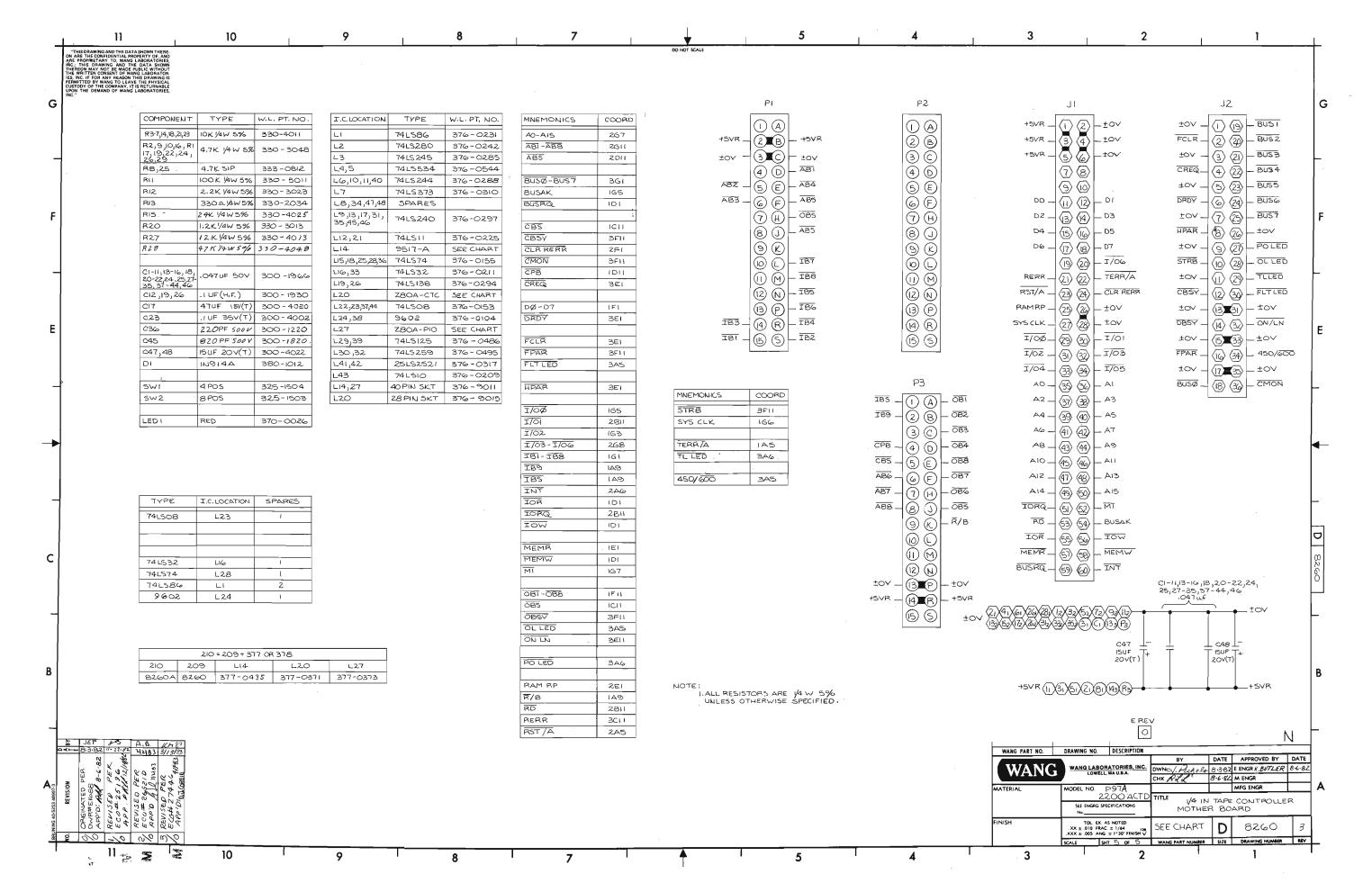

| 4-3          | 210-8260 Motherboard                                           | 4-7          |

| 4-4          | Model 2229 Interconnections                                    | 4-7<br>4-8   |

| 4-5          | 210-8261 Adapter Board                                         | 4-8<br>4-9   |

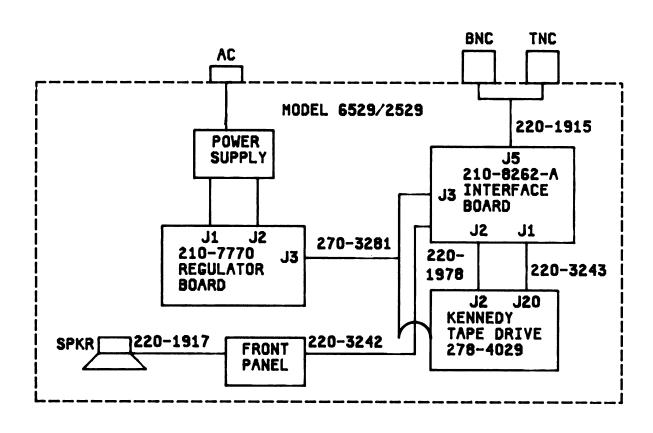

| 4-6          | Model 6529/2529 Interconnections                               | 4-9<br>5-5   |

| 5-1          | Cabinet Cover Screws                                           | 5-5          |

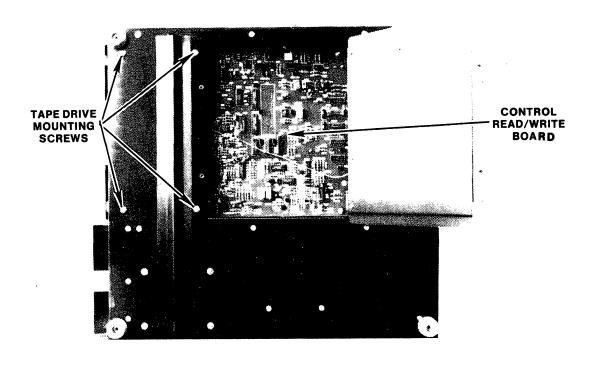

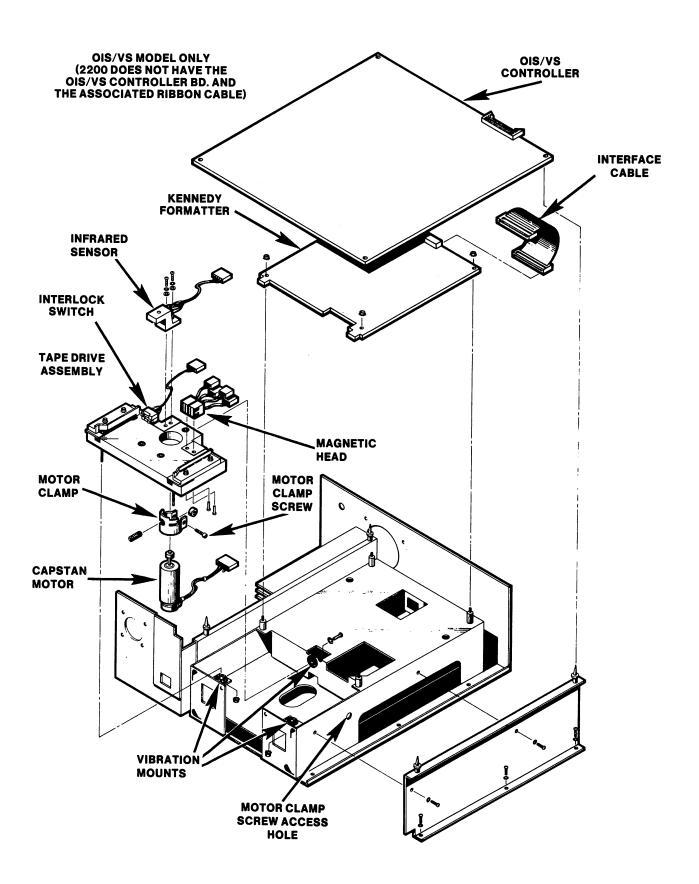

| 5-2          | Internal Components - Model 2229                               | 5-6          |

| 5-3          | Power Supply Components                                        | 5-6          |

| 5-4          | 210-7770 Regulator Board Mounting                              | 5-7          |

| 5-5          | Internal Components - Model 6529/2529<br>Chassis Bottom        | 5-7          |

| 5-6<br>5-7   |                                                                | 5-7<br>5-9   |

|              | Kennedy Replaceable Parts Assembly                             | 5-10         |

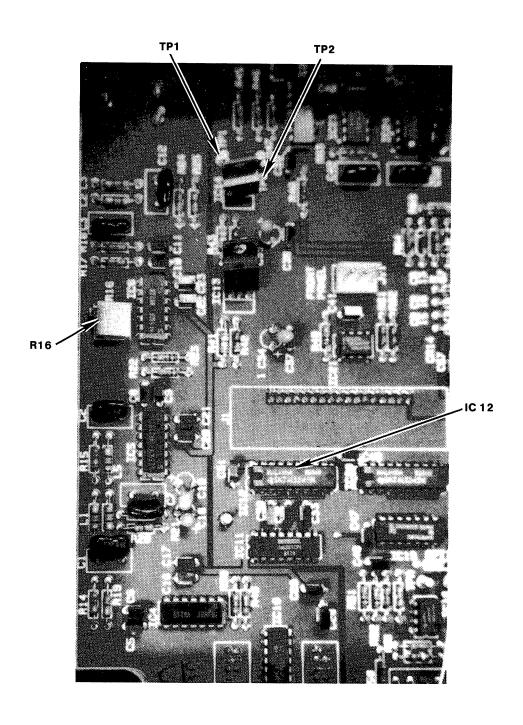

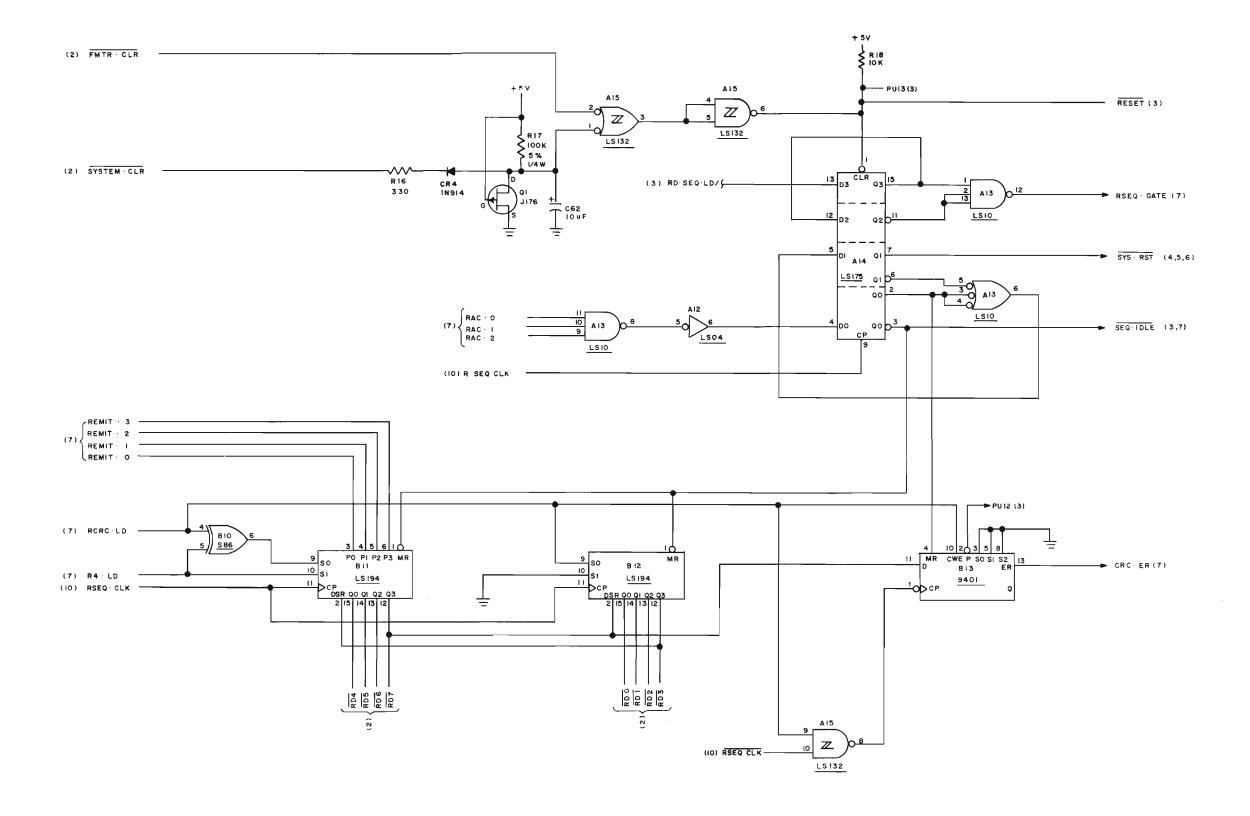

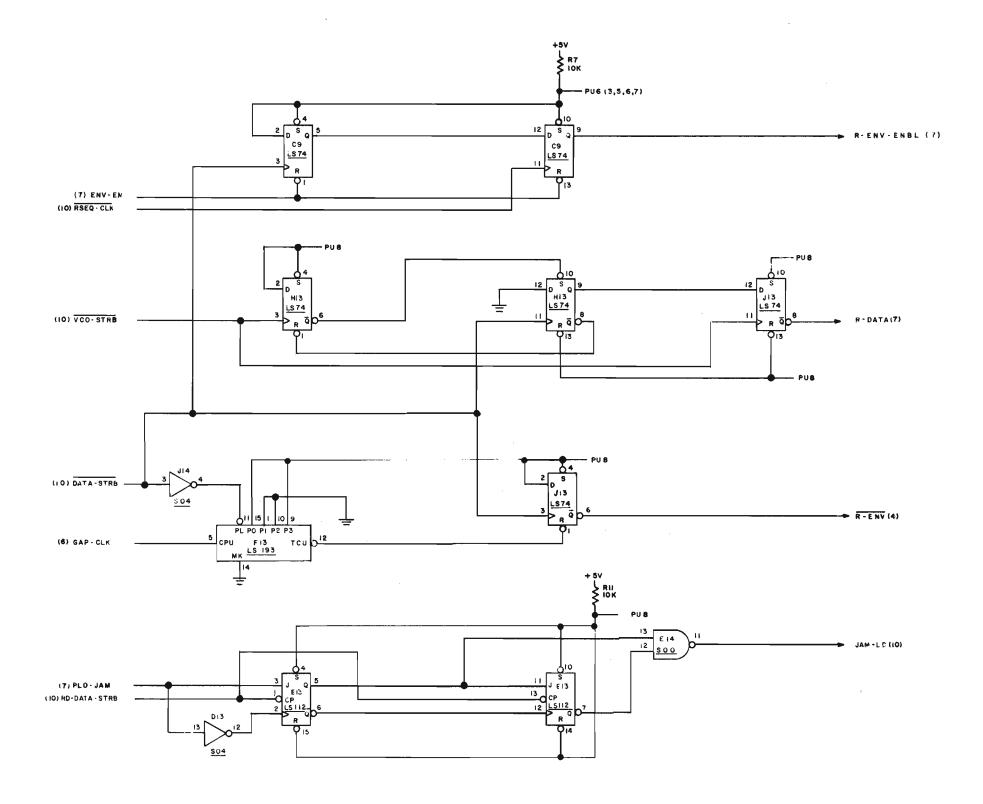

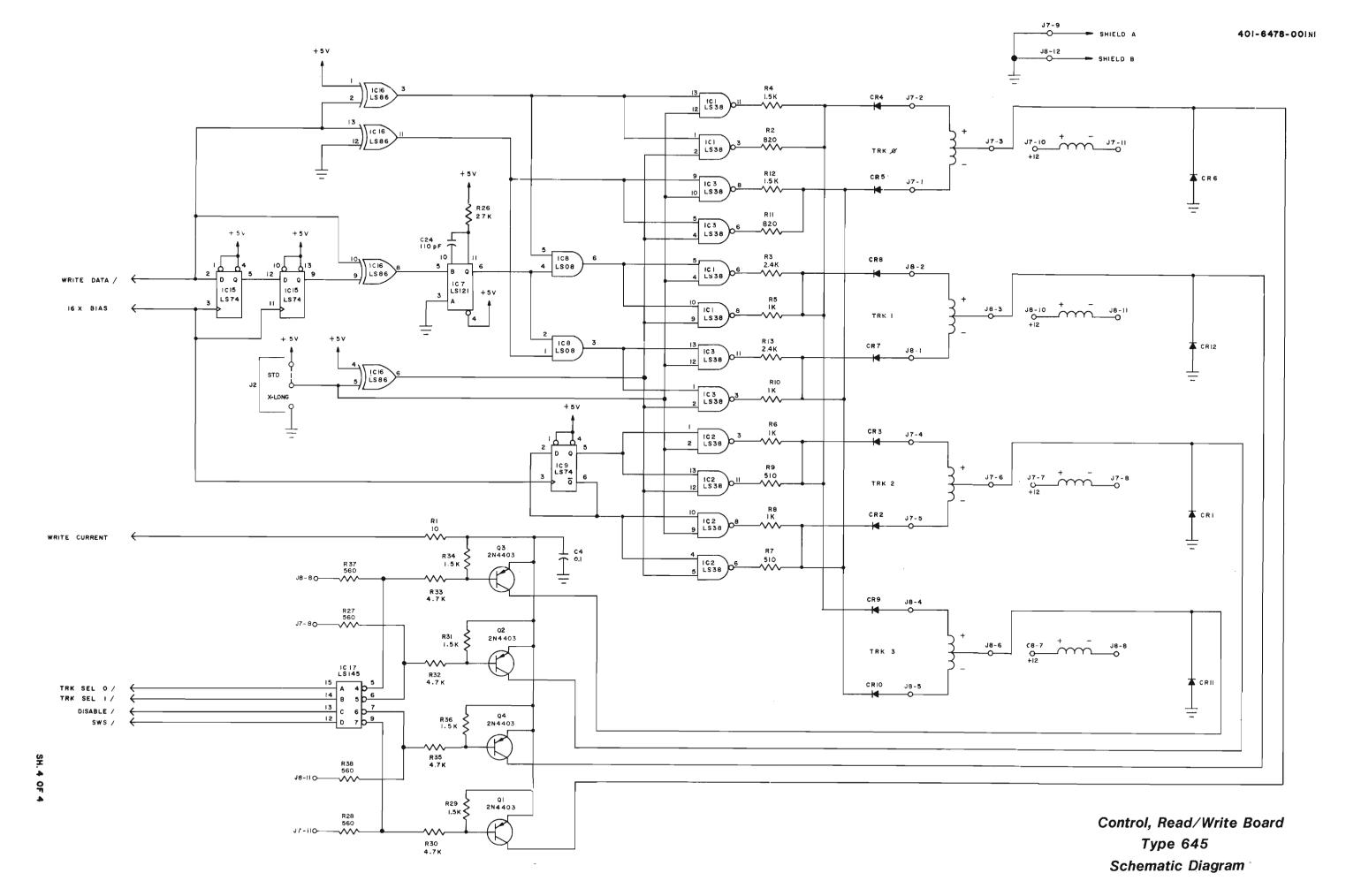

| 5-8<br>5-9   | Portion of Control/Read/Write Board Portion of Formatter Board | 5-10<br>5-12 |

| 5-9<br>5-10  | Portion of Control/Read/Write Board                            | 5-16         |

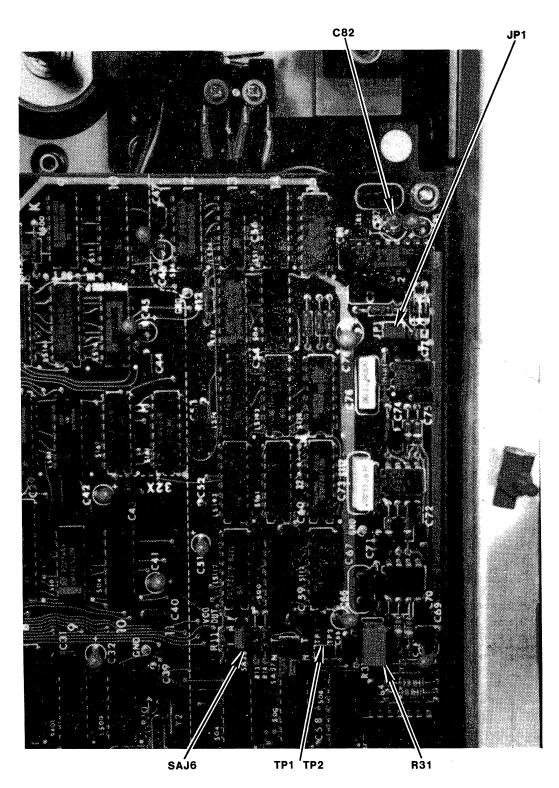

| 5-10<br>5-11 | Portion of Formatter Board                                     | 5-18         |

## LIST OF TABLES

| Number | Title                                     | Page |

|--------|-------------------------------------------|------|

| 2-1    | Kennedy Model 6455/6570 Specifications    | 2-4  |

| 2-2    | Maskable Interrupts                       | 2-13 |

| 2-3    | Command Function Codes                    | 2-19 |

| 2-4    | Summary Status Byte                       | 2-23 |

| 2-5    | Positional Status Byte                    | 2-24 |

| 5-1    | Adjustment Sequence                       | 5-3  |

| 5-2    | Off-line Diagnostics Switch Setting Chart | 5-13 |

| 8-1    | Built in Test Error Report                | 8-7  |

| 8-2    | Diagnostic Switch Settings on 210-8262    | 8-8  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 SCOPE & PURPOSE

This manual contains information necessary to unpack, install and maintain the Wang Archiving Cartridge Tape Drive (ACTD). Included is a functional block level theory of operation, installation instructions, maintenance information, schematic diagrams and troubleshooting information. With the aid of this manual the Wang Customer Engineer will be able to make all necessary cable connections, perform initial turn-on and system checkout, make necessary adjustments, analyze failures and troubleshoot faults down to the major component and board level and remove and replace major components.

## 1.2 APPLICABLE DOCUMENTS

The following documents contain additional information which would be helpful to those who install or use this product:

| Title                                       | Wang Part No. |  |  |

|---------------------------------------------|---------------|--|--|

| Model 2229 Cartridge Tape Drive User Manual | 700-7716      |  |  |

| Model 6529 Cartridge Tape Drive User Manual | 700-8071      |  |  |

| VS Utilities Reference Manual 800-1303UT-02 |               |  |  |

| Model 2529V User Summary Card               | 800-6212      |  |  |

The address for ordering the above documents follows:

Wang Laboratories, Inc. Supplies Division c/o Order Entry Dept., M/S 5511 51 Middlesex St. No. Chelmsford, MA 01863

#### 1.3 GENERAL DESCRIPTION

The Archiving Cartridge Tape Drive is a peripheral device that utilizes a 1/4 inch magnetic tape cartridge to store data. It is designed primarily as a slave processor to provide reliable backup for Wang systems having fixed disk drives. There are three stand-alone models available: Model 2229 for use with the 2200 system, Model 6529 for OIS systems and Model 2529V for VS systems.

The tape interface is made to the Kennedy Model 6455 quarter inch cartridge tape system. Models 6529 and 2529V contain their own data link logic for interface to a master, a central processing unit (CPU), memory, tape DMA controller, and interface electronics to the Kennedy tape drive. All this logic is located on a single board that is contained within the tape unit. Model 2229 uses a mother/daughter board arrangement located in the 2200 CPU for interface with the 2200 system in place of the logic board used in the other models.

#### 1.4 SPECIFICATIONS

Tape

Width Length 0.25 in. (0.64 cm) 450 ft (137.16 m)

6400 bpi

Recording

Recording Density Physical Tracks Formatted Capacity Record Format

Up to 15 mb with 450 ft tape Single Track, serial

Tape Transport

Tape Speed (Normal)

Tape Speed (Rewind)

Read Operation

Write Operation

70 ips Serial/Serpentine (see Figure 1-1) Serial/Serpentine

Start/Stop Time

Read/Write Operations

Rewind/Search Operations

25 ms 75 ms

30 ips

Start/Stop Displacement

Read/Write Operations Rewind/Search Operations 0.38 in. (0.97 cm) 3.38 in. (8.59 cm)

Tape Head

Recording Head

Serpentine Read after Write Selective Erase

Data Transfer Rate (drive

to controller)

192,000 bits per second 24,000 bytes per second

Dimensions

Height Width Depth 6.69 in. (16.99 cm) 15.38 in. (37.07 cm) 17.81 in. (45.24 cm)

Weight

28.5 lbs (12.96 kg)

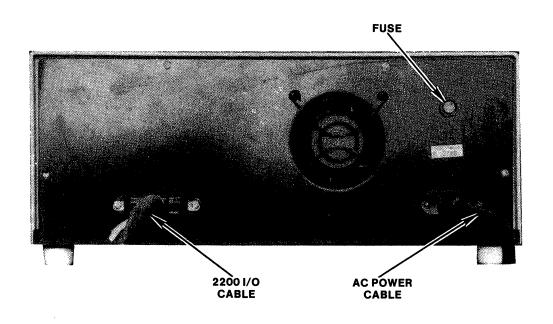

Cables

Model 2229

Models 2529V, 6529

10 ft (3.05 m) parallel cable from Tape Drive to CPU

25 ft (7.6 m) dual coaxial cable from Tape Drive to CPU (optional lengths up to 2000 ft (609.6 m)

Fuses

2 amp. @ 115V 1 amp. @ 230V

## SPECIFICATIONS (continued)

Operating Environment

Temperature Relative Humidity 50°F to 90°F (20° C to 32° C) 35% to 65% noncondensing (recommended) 20% to 80% noncondensing (allowable)

Power Requirements

115Vac (98V to 128V allowable), 50/60 Hz 1.4 amp. to 2 amp. @ 115V 220Vac (196V to 256V allowable), 50/60 Hz 0.7 amp. to 1 amp. @ 220V

Controls

Power On/Off On-Line

Indicators

Power On On-Line Fault Tape Loaded

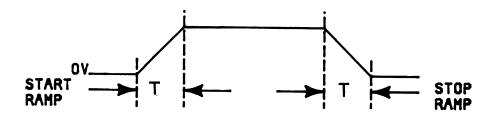

Figure 1-1 EOT/BOT Areas on Serial Serpentine Recorded Tape

#### CHAPTER 2

#### THEORY OF OPERATION

#### 2.1 INTRODUCTION

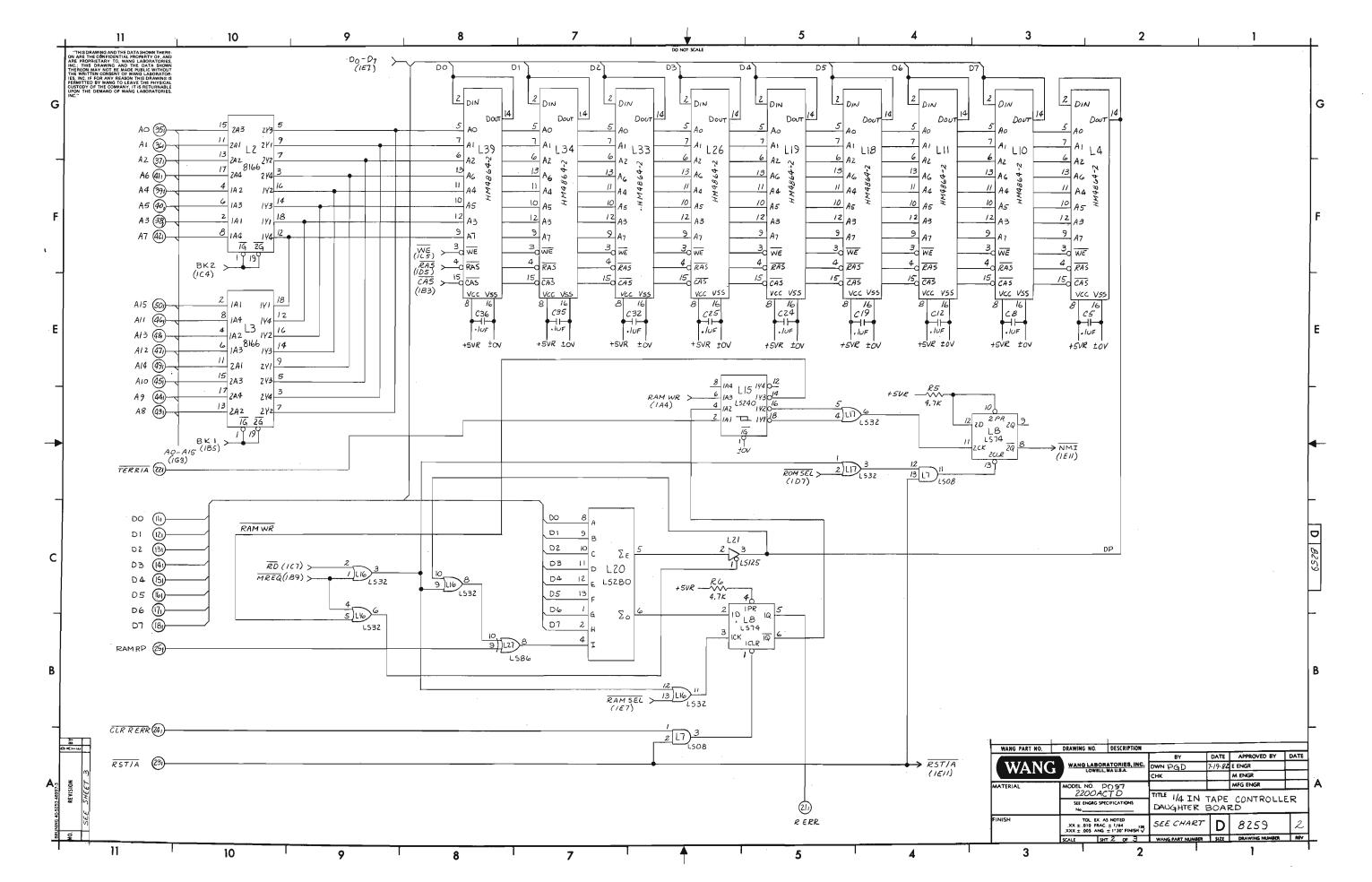

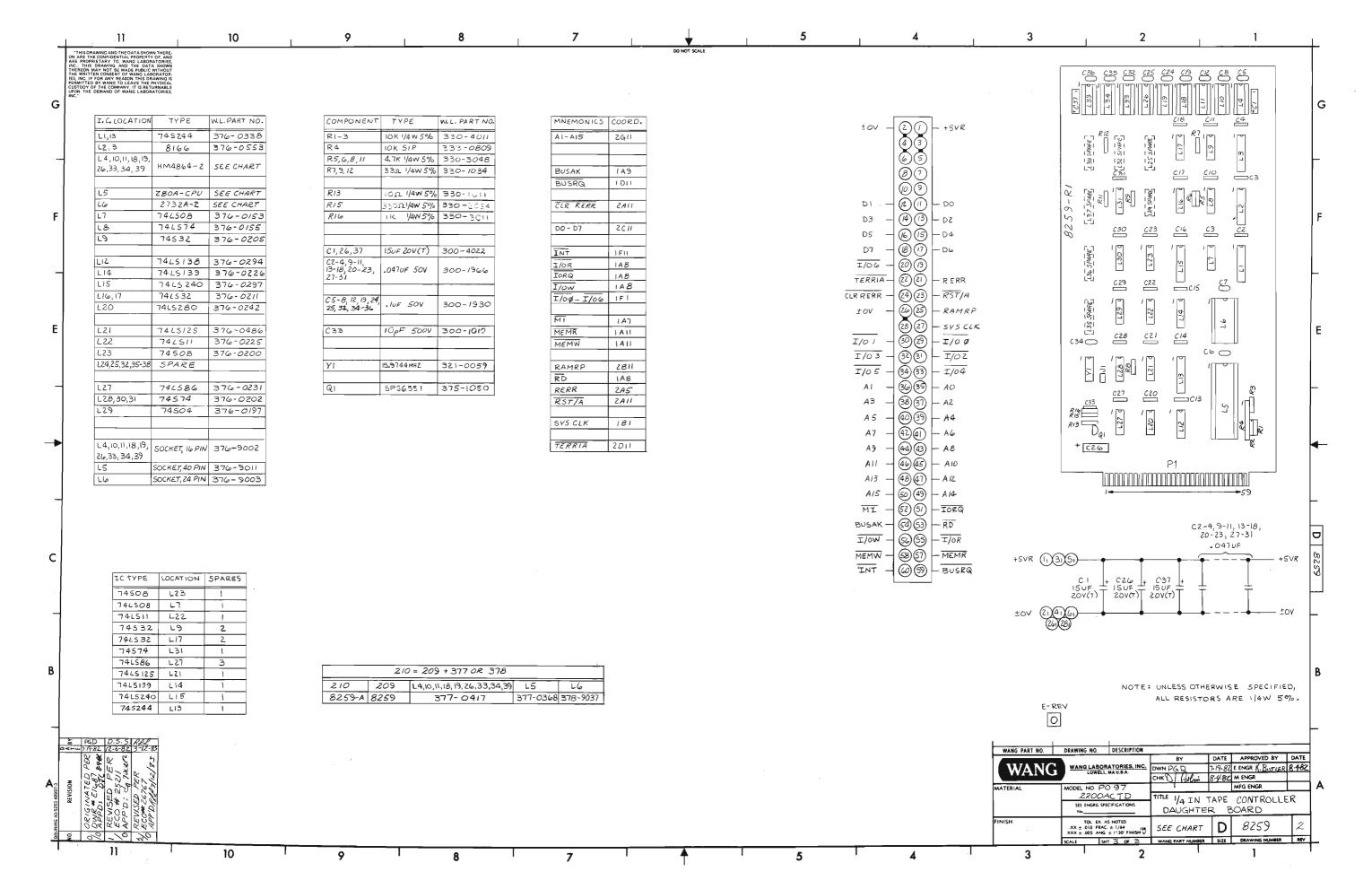

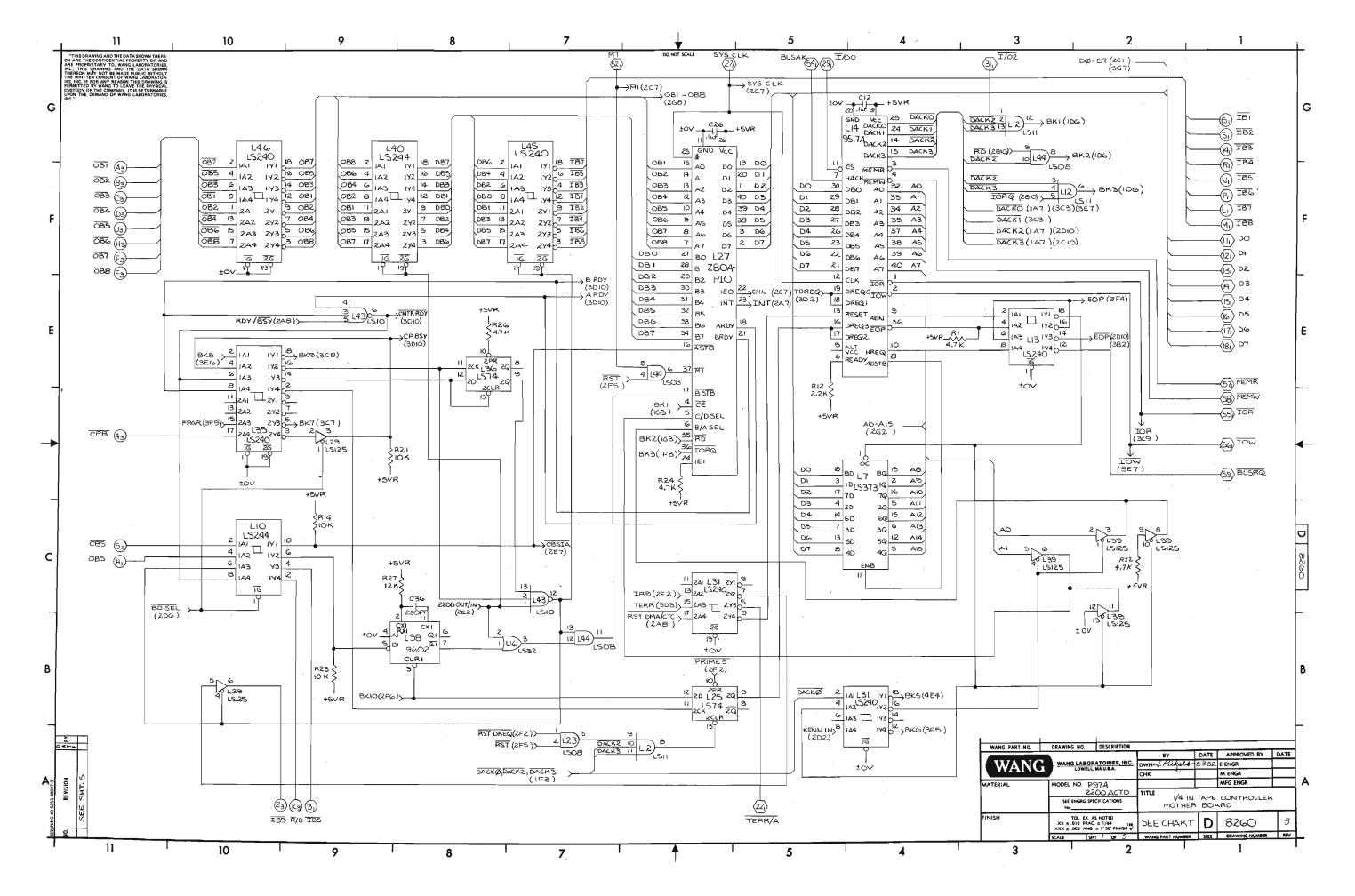

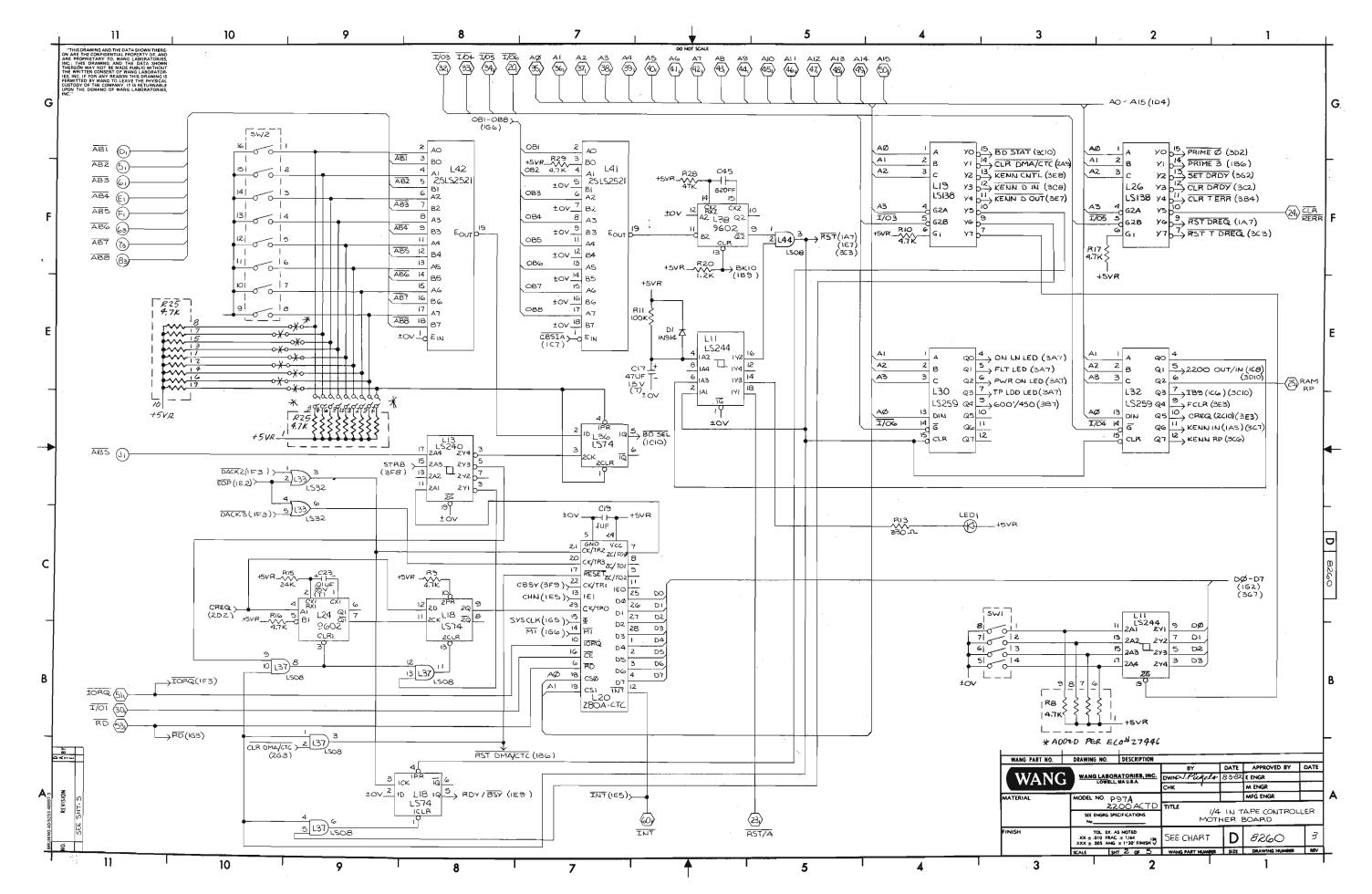

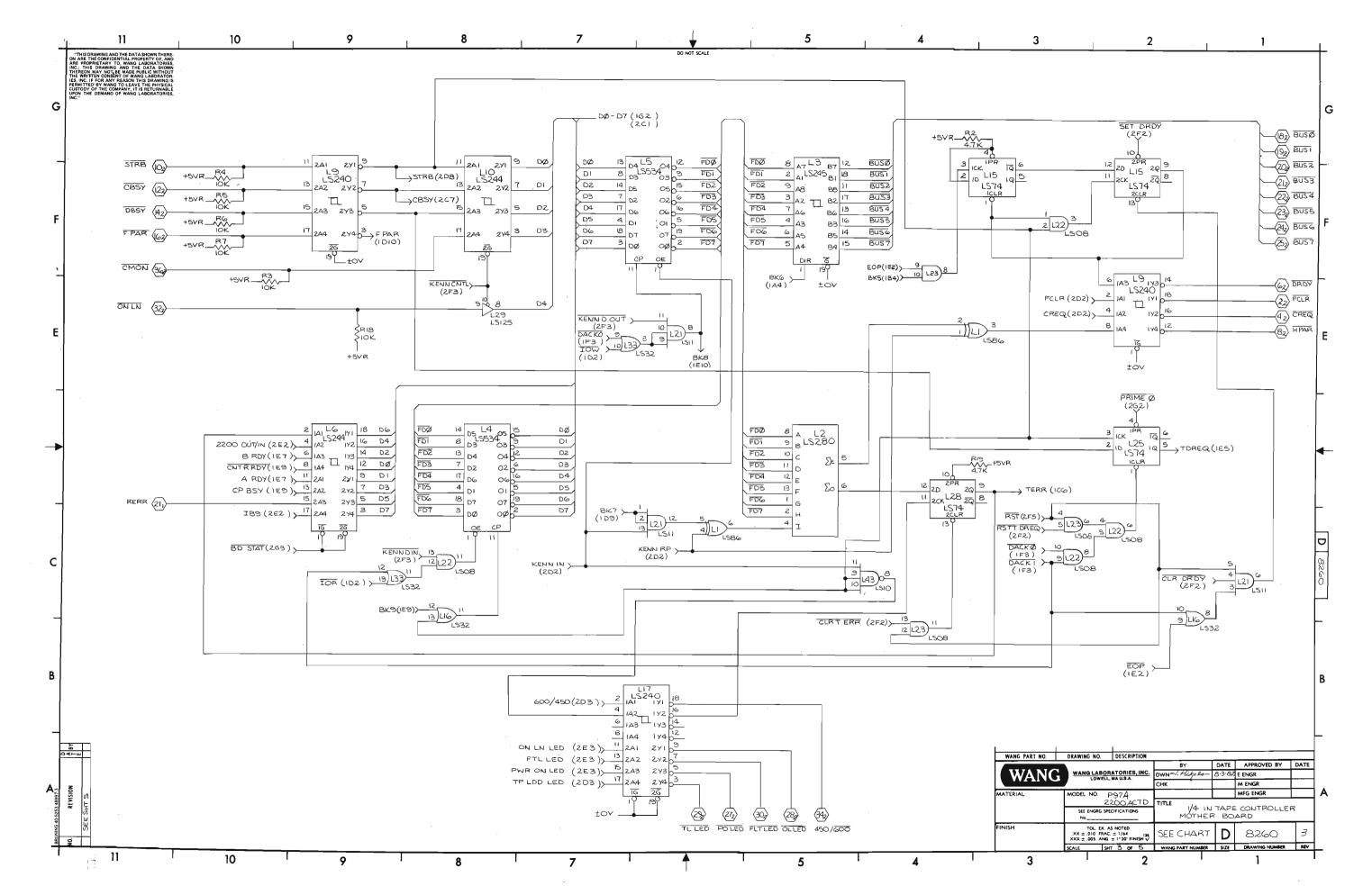

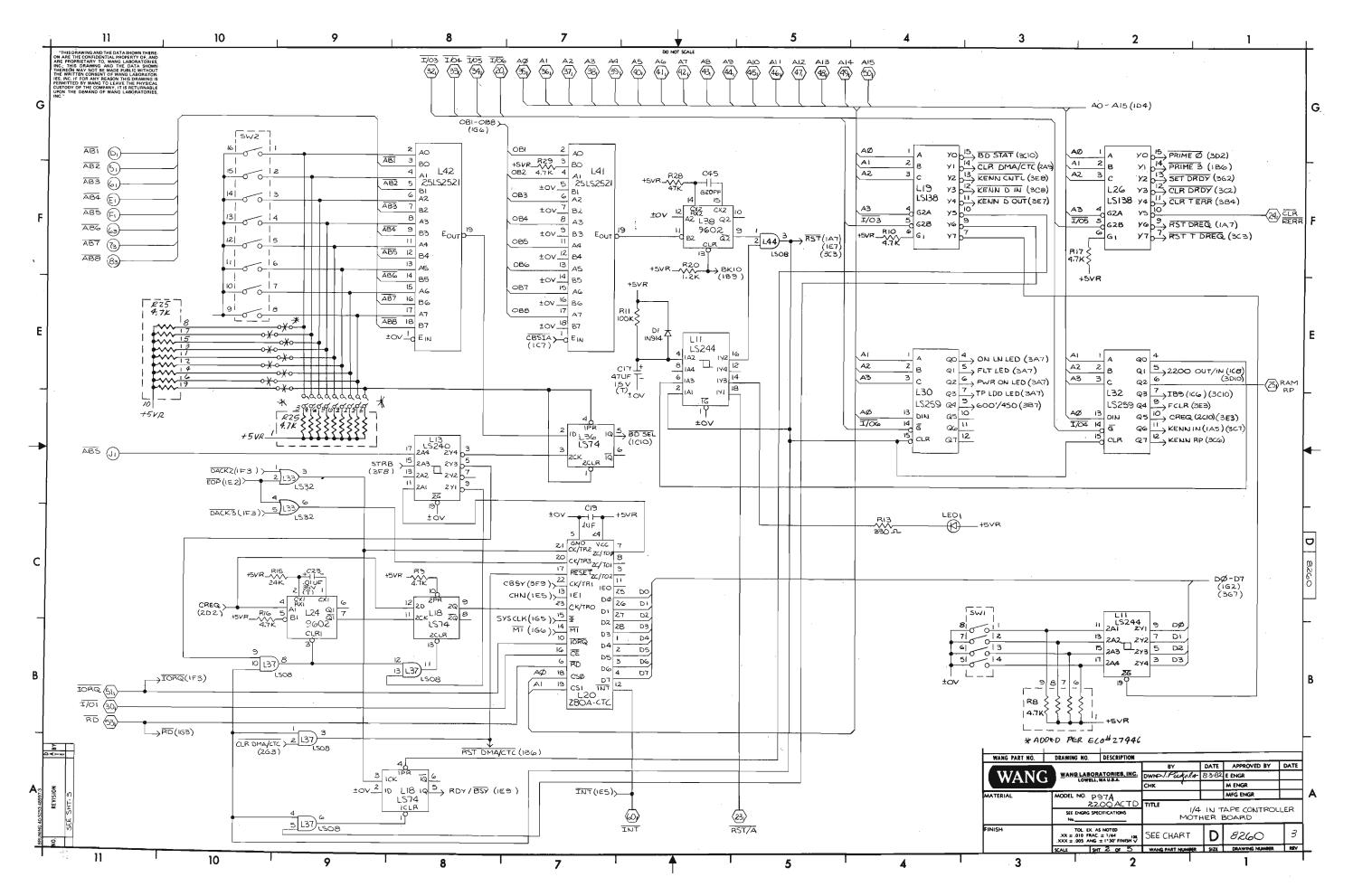

This chapter provides a functional description of the circuitry on the OIS/VS Interface board (210-8262A) used with Models 6529/2529V, the Mother board (210-8260) and Daughter board (210-8259) used with Model 2229 and the Regulator board (210-7770) used on all models.

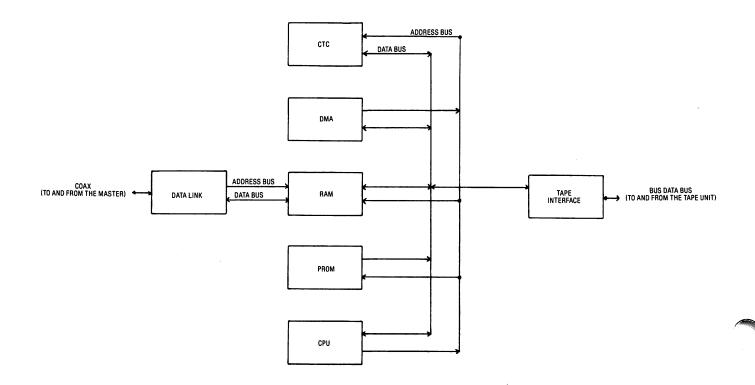

#### 2.2 THE OIS/VS INTERFACE BOARD

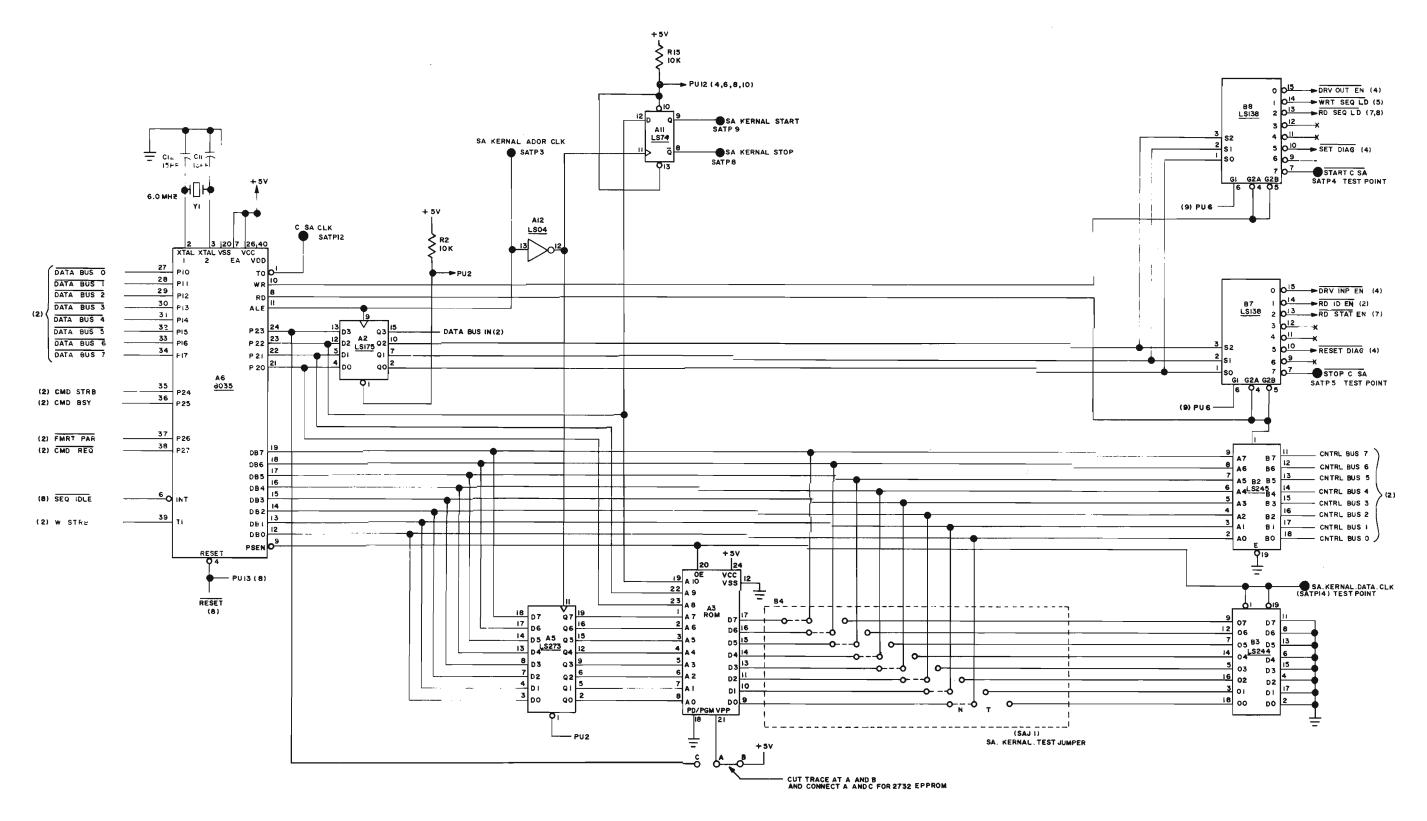

The OIS/VS Interface Board (210-8262) acts as an interface between a Kennedy 6455 or 6470 quarter-inch cartridge tape system and a Wang OIS or VS master, providing high density tape backup for 8 inch and 14 inch Winchester disk drives. It comprises seven major functional blocks: Z80A Central Processor Unit, Z8410 Direct Memory Access Controller, Z80-CTC Counter Timer Chip, Data Link, Memory (64k bytes of RAM and 4k bytes of PROM), and Tape Interface (see Figure 2-1). Information is received and transmitted from the 8262 board serially via the standard dual coaxial cable. Normally in the receive mode, the 8262 can transmit only under master control.

A 4 mHz Z80A CPU is the main processor, with a 16-bit unidirectional address bus, an 8-bit bidirectional data bus, and several control lines. Since the CPU is capable of driving only one TTL load, all address, data, and control lines are buffered by buffer/drivers. The control lines carry information to and from the Z80A specifying the required operation. The wait control line tells the CPU to enter a wait state so that a CPU-independent action can occur. There are two kinds of interrupts; nonmaskable and maskable. When activated, the nonmaskable interrupt causes the CPU to trap automatically to location 66. The five maskable interrupts specify their own trap locations.

The CPU can provide a 7-bit dynamic RAM refresh address, making 128 memory row addresses available for refresh. The 8262, however, has 64k bytes of dynamic RAM memory and therefore requires 256 row addresses for refresh. The 256-row address refresh is accomplished by toggling the A7 Address Bit with a Refresh A7 Bit and multiplexing the Refresh A7 Bit into the row address. This procedure provides an additional address line and, therefore, the necessary 256 row addresses for refresh.

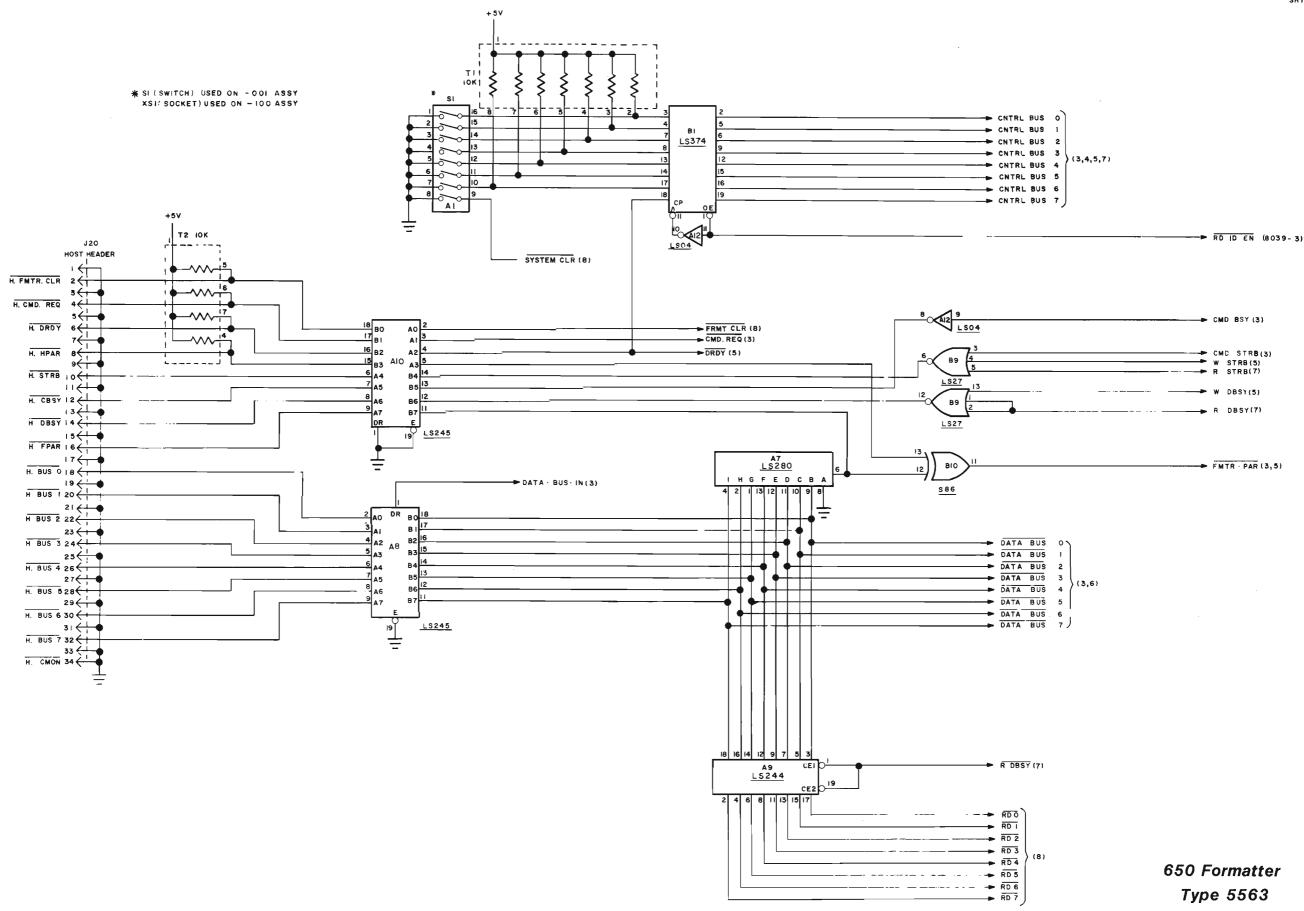

Figure 2-1 OIS/VS Interface Board Block Diagram. Data Link receives data from OIS or VS master via coaxial cable and transfers data and addresses directly to memory via DLDO and DMA buses. CPU, DMA, CTC, RAM, and PROM share DO-7 and DO-7B data buses. Data bus sends and receives data via tape interface, which transmits data to tape unit via /BUS data bus.

Data transfers to and from the tape unit are controlled by a Z8410 DMA Controller that contains a 16-bit address bus, an 8-bit data bus, and 13 control lines for external interfacing. The DMA Controller can generate independent addresses for Port A and Port B. Readable registers contain the current address of each port and a count of the number of bytes transferred. The Z8410 can be programmed via 21 writable control registers, and its status can be checked via seven readable status registers. When it is enabled and needs to transfer data, the Z8410 uses /BUSREQ, which requests the Z80A to relinquish the bus. At the end of the current CPU machine cycle, the CPU releases control of the bus to the Z8410 via /BUSACK, which asserts the DMA Controller. The Z8410 transfers a block of data in the byte transfer mode by transferring one byte and then releasing the bus until the next byte transfer is required. It also can be programmed to generate a maskable interrupt request at the end of a block transfer.

The Counter Timer Chip (CTC) generates and prioritizes Mode 2 maskable interrupts and provides a general purpose event timer. Channels 0, 1, and 3 are used in the counter mode to generate an interrupt for the first strobe pulse indicating that a specific event has occurred. Channel 2, driven by the system clock, is used in the timer mode and has a range of 4 us to 16.384 ms. It generates an interrupt request when the general purpose timer counts down to zero.

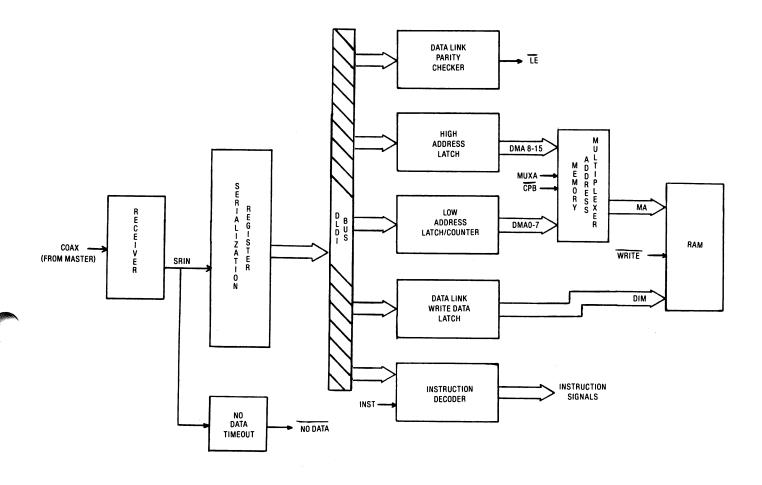

The Data Link is an asynchronous receiver/transmitter with a coaxial cable connection to the OIS master or VS serial IOP. It receives serial data from the master, checks data parity, and then assembles the data into a parallel (byte) format. It attaches to an 8-bit data bus and a 16-bit address bus, both of which are routed directly to RAM. The Data Link is normally in the receive mode, waiting for a start bit from the master. The start bit is always followed by an instruction telling the slave what type of operation will follow. The Data Link is transparent to the slave and, therefore, is not tested by the slave's power-up diagnostics.

There are 64k bytes of RAM resident on the 8262 as well as all the timing, multiplexing, refresh, and sequence logic required to interface to the RAM chips. Basically, the 8262 always performs a 256-row refresh regardless of the type of RAM loaded. Parity generation and checking are performed on all CPU memory cycles to check the integrity of data coming from memory. Limited application of power resets the parity generator/checker to even parity by default. The Z80A CPU and the Data Link must access the single-port memory concurrently. A pseudo cycle stealing scheme provides DMA access to memory: the DMA controller accesses memory via the Z80A's memory interface by disabling the Z80A through a Bus Request/Bus Acknowledge cycle.

Four kbytes of PROM contain the power-up diagnostic software. At power on, the CPU is reset to location 0000, the diagnostic PROM shadows the first 4k bytes of addressable CPU memory space, and the Data Link Receiver is disabled. The diagnostic PROM contains all the programs and data needed to verify the correct operation of the 8262 board before the system master can perform Initial Program Load (IPL). The Data Link is transparent to the 8262 and, therefore, is not tested by the power-up diagnostics.

The 8262 interfaces to the Kennedy cartridge tape system via the Kennedy Pico Bus Interface. This interface consists of two separate Write Data Latches, two Read Data Latches, and a bidirectional 8-bit data bus that uses odd write and read parity bits, four handshaking control signals, a data strobe, and a cable interlock signal (Cable Monitor, CMON) that indicates whether the cable between the slave and tape unit is connected. The tape interface can be tested via diagnostic loopback tests without actually being connected to an active tape unit.

Switches resident on the SW2 board provide four device type bits in the Status Word that inform the master that it is communicating with the 8262. SW1 Device Class Switches define additional 8262 characteristics to the master. The 8262 board has its eight device type switches set to a value of OAH for use with the Kennedy Model 6455 and to OBH for use with the Model 6470. The switch inputs are placed on the DO-7B bus to be read by the /INO7 command, enabling a Switch Buffer.

Model 6455, a 4-track, 6400-bit/in (30/70-ips) unit, can store a maximum of 23M bytes of unformatted data. Model 6470, a 7-track, 10,000-bit/in (45/90-ips) unit, can store a maximum of 63M bytes of unformatted data. Upward tape read compatibility allows the 6470 to read tapes written by the 6455; the 6455, however, cannot read tapes written on the 6470. Specifications for both models are listed in Table 2-1. (Model 6470 has not yet been released; therefore, its specifications are subject to change.)

Table 2-1: Kennedy Model 6455/6470 Specifications

#### Specifications Identical For Both Models

Cartridge Type 3M Type DC300A (300 ft), DC300XL (450 ft), DC600A (600 ft)

Isoelastic Data Cartridge

Recording Head Serpentine, Read-After-Write, with

Selective Erase

Record Format Single-Track, Serial

Data Reliability

- soft error rate

- hard error rate  $1 \text{ in } 10^{10} \text{ bits}$   $1 \text{ in } 10^{11} \text{ bits}$

Power Requirements  $5 \pm 0.25$  Vdc at 3 A avg and 5 A pk  $24 \pm 4$  Vdc at 1.5 A avg and 3 A pk

24 <u>-</u> 4 vac at 1.5 h avg and 5

- Slave CPU Pico Bus, TTL low-true, 34-pin 3M flat

- Power 6-pin molex

- Write Current Select 3-pin molex

Interface

Table 2-1 (continued)

#### Specifications Unique To Each Model

|                                                 | Model 6455                                | Model 6470                                 |

|-------------------------------------------------|-------------------------------------------|--------------------------------------------|

| Unformatted Capacity - 300 ft - 450 ft - 600 ft | 11.5M bytes<br>17.3M bytes<br>23.0M bytes | 31.5M bytes<br>47.25M bytes<br>63.0M bytes |

| Recording Density                               | 6400 bits/in                              | 10,000 bits/in                             |

| Number of Tracks                                | 4                                         | 7                                          |

| Normal Tape Speed                               | 30 ips                                    | 45 ips                                     |

| Fast Tape Speed                                 | 70 ips                                    | 90 ips                                     |

| Start/Stop Time                                 | 25 ms @ 30 ips<br>65 ms @ 70 ips          | 50 ms @ 45 ips<br>75 ms @ 90 ips           |

| Data Transfer Rate                              | 24k bytes/s<br>41.7 us/byte               | 56.25k bytes/sl<br>17.8 us/byte            |

|                                                 | Cannot read<br>6470 format                | Can read<br>either format                  |

Since the 8262 sees only the data passing between itself and the master, and this data is not system dependent, it detects no difference between an OIS or VS system. An OIS system uses the tape drive strictly for archiving, whereas a VS system also uses it for file backup and restoration procedures. Both VS and OIS systems determine which device they are communicating with by reading a device code that identifies the device as the tape drive and also distinguishes the particular model of the tape drive. The master then loads the device with the appropriate software to bring the tape drive up and running. The tape drive is treated as a batch device, since it does not interact actively with the operator.

#### 2.2.1 CONTROLS AND INDICATORS

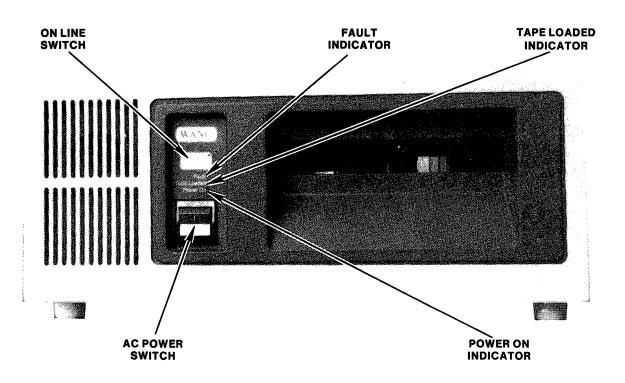

Operator controls consist of an AC power switch and an ONLINE membrane switch, both located on the front panel. When the ONLINE switch is operated, a Switch Flip-flop issues the SWITCH signal which asserts the CTC trigger input. The CTC then generates a maskable interrupt request via channel 3. Once the ONLINE pushbutton is pressed, further switch interrupts are disabled until an /OUT00 command reenables the interrupt. To ensure that the switch is properly debounced, the 8262 waits 20 ms before issuing OUT00.

Front panel indicators consist of POWER ON, ONLINE, FAULT, and TAPE LOADED. Four ERROR indicators also located on the board are used to identify particular errors. Of the eight indicator LED's on the ACTD slave, seven are driven by the L51 LED Latch, which is controlled by data bits DO-5B, D7B, and the /OUTOD command. The eighth LED, the ONLINE indicator, goes on when the ONLINE switch is activated and stays on as long as the unit is online. The FAULT indicator indicates to the operator that a hardware error condition exists; the particular error is diagnosed according to the board resident error indicators. The TAPE LOADED light indicates that a tape cartridge is properly loaded. The tape cartridge should not be removed unless this indicator is OFF.

The POWER ON LED blinks on and off during execution of the PROM-resident power-up diagnostics until the /EP (Exit Prom) signal becomes active. At this time, the POWER ON LED comes on steadily, indicating successful completion of the power-up diagnostics. This indicator is not under CPU control; it is driven by the Power-On Monitor.

A speaker generates a beeping signal to alert the operator when the tape unit needs service or when a problem is encountered in the unit. When a 1-Shot receives the /OUTO8 command, it issues a signal to activate a Timer (100 ms) which, in turn, generates the SPEAKER signal.

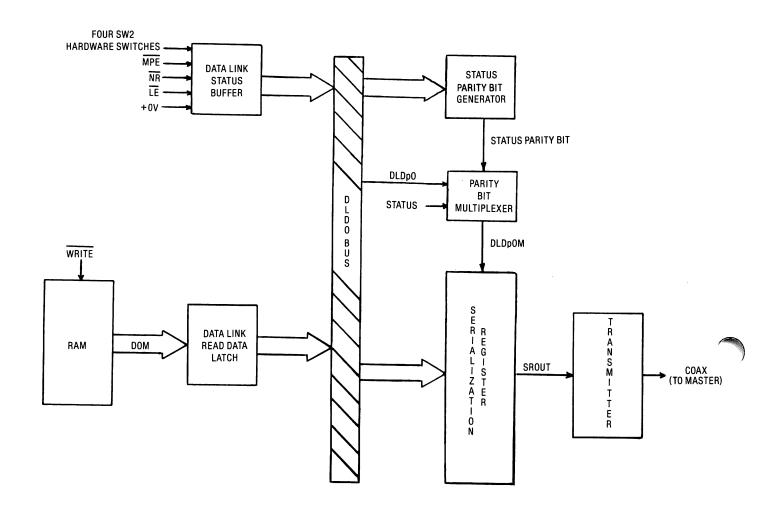

#### 2.2.2 DATA LINK

The Data Link is basically a standard OIS data link that establishes bidirectional, half-duplex, asynchronous communication between interface board memory and an OIS master or VS serial IOP. At one end of the communication path, an 8-bit data bus and a 16-bit address bus carry bytes of parallel data to RAM. At the other end, serial data passes between the Data Link and the master along two coaxial cables. During receive operations, as shown in Figure 2-2, the Data Link accepts serial data from the master, assembles it into a parallel byte format, and stores it into memory. To transmit, as shown in Fig 2-3, the Data Link accepts parallel data from memory, converts it to serial format, and sends it to the master. The serial format for each byte provides a start bit, eight data bits, an odd parity bit, and a stop bit, in that order.

The Data Link responds to six commands from the master: a restart command, a status inquiry, two read commands, and two write commands. Upon receiving the 1-byte restart command code, it performs a hardware initialization sequence. In response to the 1-byte status command code, it returns a byte of device status information. Read and write commands require a 1-byte command code and a 2-byte data address. The Data Link can read or write either a single byte or a block of 256 consecutive bytes. The 2-byte data address is the address of the single byte or the address of the first byte in the 256-byte block. It follows the 1-byte command code, with its high-order byte first.

Figure 2-2 Data Link Receive Block Diagram. Serial data from master is received and arranged in parallel by Serialization Register. Input line is monitored by No Data Timeout logic. From DLDI bus, data is checked for parity and decoded to determine instruction. Address is routed to memory via Low and High Address Latches and Address Multiplexer. Data is routed to memory via Data Link Write Data Latch.

Figure 2-3 Data Link Transmit Block Diagram. Data Link Read Latch places data onto DLDO bus. Data is then passed to Serialization Register, where it is serialized and transmitted. Data Link Status Buffer is used for IN STATUS command only. Status Byte is read from Status Buffer onto DLDO bus. Status Parity Bit Generator provides parity bit, which is multiplexed into Serialization Register, for Status Byte.

The Data Link normally idles in its receive mode, awaiting a start bit from the master. Upon receipt of a start bit, the Data Link accepts and deciphers the 1-byte command code that follows. If the command is a read or write command, it also accepts a 2-byte address. It then executes the command, entering the transmit mode if the command is a write, and returns to the receive mode to await the next command. /LE, the Line Error signal, is generated when the Data Link detects bad parity within the received data. /LE is stored and can be read by the master using the STATUS instruction. STATUS also clears the stored line error condition, enabling the master to detect a line error and then retransmit. A line error prevents any data from being written to memory until the error can be cleared.

Receiver/Transmitter logic moves the serial data it receives between the master and the Serialization Register. The receiver/transmitter also converts data from serial differential data to serial data (Write) and vice versa (Read). The Serialization Register converts data from the receiver from serial to parallel format. Outgoing data is converted from parallel to serial format and sent to the Data Link Transmitter.

There are two unidirectional buses in the Data Link. The Data Link Data Input (DLDI) bus carries inbound data from the receiver to memory; the Data Link Data Output (DLDO) bus carries outbound data to the transmitter from memory or from the Status Buffer. Line Turnaround Delay logic generates a delay to prevent information collisions when the direction of information to or from the Data Link is changed.

#### 2.2.3 Z80A CENTRAL PROCESSOR UNIT

A 4 mHz Z80A CPU is the main processor. At power-on, the processor is reset to begin power-up diagnostics from PROM. It defaults the PROM chip to memory address 0000 and disables the Data Link Receiver logic. When diagnostics are completed, an /OUT03 command enables the Data Link Receiver logic (making the controller visible to the master) and removes the PROM from the memory address space. A HALT instruction then places the CPU into a state in which only NOP instructions are executed. A RESTART command from the Data Link logic terminates NOP execution by resetting the processor, allowing it to begin program execution from memory address 0000. Figure 2-4 is a block diagram of CPU-associated logic.

The CPU has a 16-bit unidirectional address bus (A0-15), an 8-bit bidirectional data bus (D0-7), and several control lines. The address bus, the data bus, and some of the control lines are shared with the DMA Controller. All address, data, and control lines are buffered since the CPU is a MOS device capable of driving only one TTL load.

Figure 2-4 CPU, DMA, CTC, PROM and RAM Block Diagram

Referring to Figure 2-4, the CPU, DMA and PROM share address bus AO-15. DO-7 data bus is shared by CPU, DMA, CTC and PROM. Either CPU or DMA, whichever has bus control, issues operation control signals. RAM and PROM are accessed via buffered Address and Data Buses. Data is transferred to and from memory via CPU Read and Write Data Latches. Memory Address Multiplexer provides address. Memory Parity logic establishes and checks incoming data parity.

#### 2.2.4 DIRECT MEMORY ACCESS LOGIC

The Z8410 Direct Memory Access (DMA) Controller contains a 16-bit address bus and an 8-bit data bus, and uses 11 of its 13 control lines in the controller application (see Figure 2-4). The DMA Controller transfers data to and from the tape unit and can generate independent addresses for Input and Output Ports. Twenty-one writable control registers are used to program the Z8410 and seven readable status registers contain the current address of each port and a count of the number of bytes transferred. OUTPUT to PORT 04H writes a command to the controller and INPUT to PORT 04H reads its status registers. Since no reset pin is available, the controller can be reset only via software.

Several of the control lines, as well as all of the address and data buses, are shared between the DMA and CPU. The DMA Controller has two unique control outputs, /BUSREQ and /INT, and five control outputs that it shares with the CPU: /Ml, /RD, /WR, /IORQ, and /MREQ. The /Ml signal is active during op-code fetch cycles. The /RD signal goes active when a read operation is pending. When a write operation is pending, /WR goes active. When either the CPU or DMA makes an I/O operation request, /IORQ goes active. When a memory read or memory write is pending, /MREQ goes active.

/BUSREQ and /INT are the two control outputs unique to the DMA Controller. The /BUSREQ signal goes active on pin 15 when the controller requests bus control for a DMA transfer. The /INT signal goes active when the controller must interrupt the CPU.

The DMA Controller uses four unique control input signals: /BAI, /CE,/WAIT, /RDY, and IEI. (The /BAO and /IEO control pins are not used in the controller application.) When the controller obtains bus control, the CPU /BUSACK signal asserts /BAI. The /CE,/WAIT line has two uses: When the DMA Controller is not active, the /CE signal enables the controller; if the controller is already the bus master, a /WAIT signal causes a wait state when the Data Link needs bus access. When a data byte is ready for transfer, the RDY signal initiates the DMA Controller to begin the /BUSREQ-/BUSACK cycle to gain bus access. Since the DMA Controller has the highest priority among non-maskable interrupts, the Interrupt Enable Input (IEI) is tied high. The DMA disables the CTC interrupt by issueing a signal to disable CTC interrupts whenever the DMA has an active interrupt. CTC-generated interrupts have a lower priority than DMA-generated interrupts.

In the byte transfer mode, the DMA Controller transfers a block of data by transferring one byte and then releasing the bus until another byte transfer is required. In this manner, the CPU is disabled for 2.5 of every 41.7 us (Model 6455) or 2.5 of every 17.8 us (Model 6470). In the byte transfer mode, the byte counters are n-1 counters ("n" represents the tape record length); therefore, the smallest record must be at least 2 bytes long.

The DMA Controller Chip governs data transfers between the tape unit and memory. While the CPU is active, the Z8410 is disabled, with its tri-stated signals off the bus (in a high-impedance state). A RDY signal to controller pin 25 enables the controller to request bus control from the CPU. (During diagnostics, an output to PORT OFH generates the RDY signal.) A /BUSREQ signal notifies the CPU of the DMA's request for bus control. At the end of the current CPU machine cycle, the CPU releases control of the bus to the Z8410 via a /BUSACK signal.

The Z8410 is now the bus master, controlling the primary signals to achieve its data transfers. When it is through transferring data, the controller releases the bus and the CPU resumes program execution from where it left off. The Z8410 is programmed to generate a maskable interrupt at the end of a block transfer. Vectored interrupt XX08 notifies the CPU that the End-of-Block has been reached and all transfers have been completed.

#### 2.2.5 COUNTER TIMER CHIP

The Z80A Counter Timer Chip is a programmable, 4-channel device that provides counting and timing functions for the controller. It includes an 8-bit data bus, eight control outputs, and 10 control inputs (including the clock input); three control outputs and the data bus are shared with the CPU and DMA (see Figure 2-4). The chip can be reset by /MR (Master Reset) or by a software reset command.

The Counter Timer Chip (CTC) prioritizes and generates Interrupt Mode 2 maskable interrupts and acts as a general purpose event timer. When the CTC issues an interrupt, it places a unique vector on the data bus to accompany the interrupt to the CPU. This vector combines with information programmed in the CPU's Instruction (I) Register to provide a pointer to a table. The table contains a list of interrupt service routine addresses that point the CPU to the proper service routine.

The CTC receives buffered Address Bits AOB, AlB, and A7B. AOB and AlB provide the CSO and CSl (Channel Selection) signals that select one of the four CTC channels to generate prioritized interrupts. A7B provides the /CE (Chip Enable) signal.

In the counter mode, Channels 0, 1 and 3 generate an interrupt upon the arrival of the first strobe pulse to indicate which particular event has occurred. Therefore, the CTC Down Counter for these channels must be set to 1. Four trigger inputs initiate the generation of prioritized outputs. TCE (Tape Command Error) activates trigger 0 to generate an interrupt signal plus output signal TCECLR (1-ms Tape Command Timeout/Tape Command Error). TCE indicates that either an invalid code or a code with bad parity was sent to the tape unit and TCECLR clears the tape operation. An inactive /CBSY (Command Busy) signal activates trigger 1, generating an interrupt signal plus output signal CBYSCLR. When /CBSY goes inactive (high), it indicates that the tape unit has successfully completed a command. CBSYCLR clears the tape operation. SWITCH indicates that the ONLINE switch has been activated on the slave control panel. It asserts trigger 3 to generate an ONLINE interrupt data code from the CTC's data pins.

Channel 2 has a range of 4 us to 16.384 ms and, since it is used in the timer mode off the 250 ns system clock, needs no trigger. It can be loaded with a prescaler that defines the number of clock pulses from 16 to 256 to be counted down before the CTC generates an interrupt at count = 0. The CPU can count these interrupts generated on Channel 2 to timeout long events such as searching for a File Mark. Channel 2 use is controlled entirely by software.

The /RD, /IORQ, and /Ml control outputs from the CTC are shared between the CPU and DMA. They allow a control word to be written to or a status word read from the CTC. /RD goes active on pin 6 when a read operation is pending, /IORQ on pin 10 is active when the CPU or DMA makes an I/O operation request, and /Ml is active on pin 14 during op-code fetch cycles.

The DMA Controller has the highest priority maskable interrupt. When the DMA has an interrupt, a signal to the CTC disables the CTC generated interrupts. Table 2-2 illustrates the established priority among all the maskable interrupts.

Table 2-2: MASKABLE INTERRUPTS

| <u>Priority</u> | <u>Type</u>                                              | Vector |

|-----------------|----------------------------------------------------------|--------|

| 1               | Tape End of Block                                        | хх08н  |

| 2               | <pre>1-ms Tape Command Timeout/Tape Command Error.</pre> | хх00н  |

| 3               | Tape Command Completion.                                 | XXO2H  |

| 4               | CTC Channel 2 Timeout.                                   | хх04н  |

| 5               | ONLINE Switch Contact Closure                            | хх06н  |

#### 2.2.6 MEMORY

## 2.2.6.1 Random Access Memory

The controller provides 64k bytes of onboard RAM as well as all the timing, multiplexing, refresh, and sequence logic necessary to interface this memory. To the CPU or the Data Link the RAM is basically a 2-port (input and output) memory. Therefore, the RAM cannot be accessed simultaneously (see Figure 2-5). The RAM chips require a 256-row address refresh (eight row address bits/4-ms refresh time). Refresh occurs when the memory receives both a refresh address on its address pins and a /RAS (Row Address Strobe) signal.

#### 2.2.6.2 Power-Up Diagnostic PROM

When power is first applied, the CPU is reset to location 0000, the first 4k bytes of addressable CPU memory space default to the diagnostic PROM and the Data Link receiver is disabled. The diagnostic PROM contains all the programs and data needed to verify the correct operation of the cartridge tape slave before it can be accessed by the system master. When the PROM is selected by the upper four address bits (A12-15B), the lower 4k bytes of RAM are de-selected, causing the real RAM address space to begin at location 1000H.

Power-up diagnostic software on the controller board is contained in PROM. /POR (Power-On Reset) presets the PROM Select Flipflop, enabling the PROM to begin the diagnostic routine. A /PROM signal is then generated via the logic and this signal enables the PROM.

/RDB and /PROM MREQ (Buffered CPU Memory Read and CPU PROM Memory Request) combine to create a signal that asserts the Output Enable (/OE), thereby enabling the outputs of the diagnostic PROM. /RDB must be active while the PROM is being read, and /PROM MREQ ensures that the PROM is selected and a memory request has been made.

For the diagnostic program to test the lower 4k bytes of RAM, the diagnostic program in PROM is de-selected from the lower 4k bytes of RAM and loaded into the next higher 4k bytes. PROM maintains control of the diagnostic program as the software is loaded into RAM. The PROM is de-selected after the move and diagnosis of the lower 4k bytes of RAM proceeds. During diagnostic testing, PROM is enabled and disabled by a ported output to the PROM Enable logic.

The PROM Select Flipflop handles PROM selection and de-selection: an /OUTO1 command and the D7B bit select and de-select the PROM as required. When power is applied, PROM diagnostic routines are located in the lower 4k bytes of RAM. (The lower 4k bytes of RAM are de-selected.) To diagnose the lower 4k bytes of RAM, the /OUTO1 command de-selects the PROM when D7B goes low. PROM then loads the diagnostic program code into RAM. The PROM is de-selected, and diagnostics continue via the diagnostic program in the upper RAM. When diagnostics are completed, the PROM is again selected.

Figure 2-5 Block Diagram of Data Paths To and From RAM. When memory is written, it receives data and parity bits from DIM bus; when it is read, data and parity bits are transmitted out via DOM bus. CPU and Data Link maintain separate routes to and from RAM; there are two data paths into DIM bus and two from DOM bus. Sixteen-bit address used in read or write operations is sent to memory in two address bytes. Four-to-one Memory Address Multiplexer connects either low or high address byte of AB or DMA Address Bus with Memory Address Bus (MAO-7).

The POWER UP indicator on the front panel flashes throughout diagnostic testing. When diagnostics are completed, the I/O Decoder issues an /OUTO3 command to turn the POWER ON light on continuously, de-select the PROM from memory space, enable the Data Link Receiver and force a HALT onto the bus to halt the CPU. If the diagnostics fail, the Data Link Receiver will not be enabled. Instead, the FAULT light will be go on and an error code will be issued to the Error LEDs. Fifteen error conditions can be represented in the Error LEDs (see TAble 8-1).

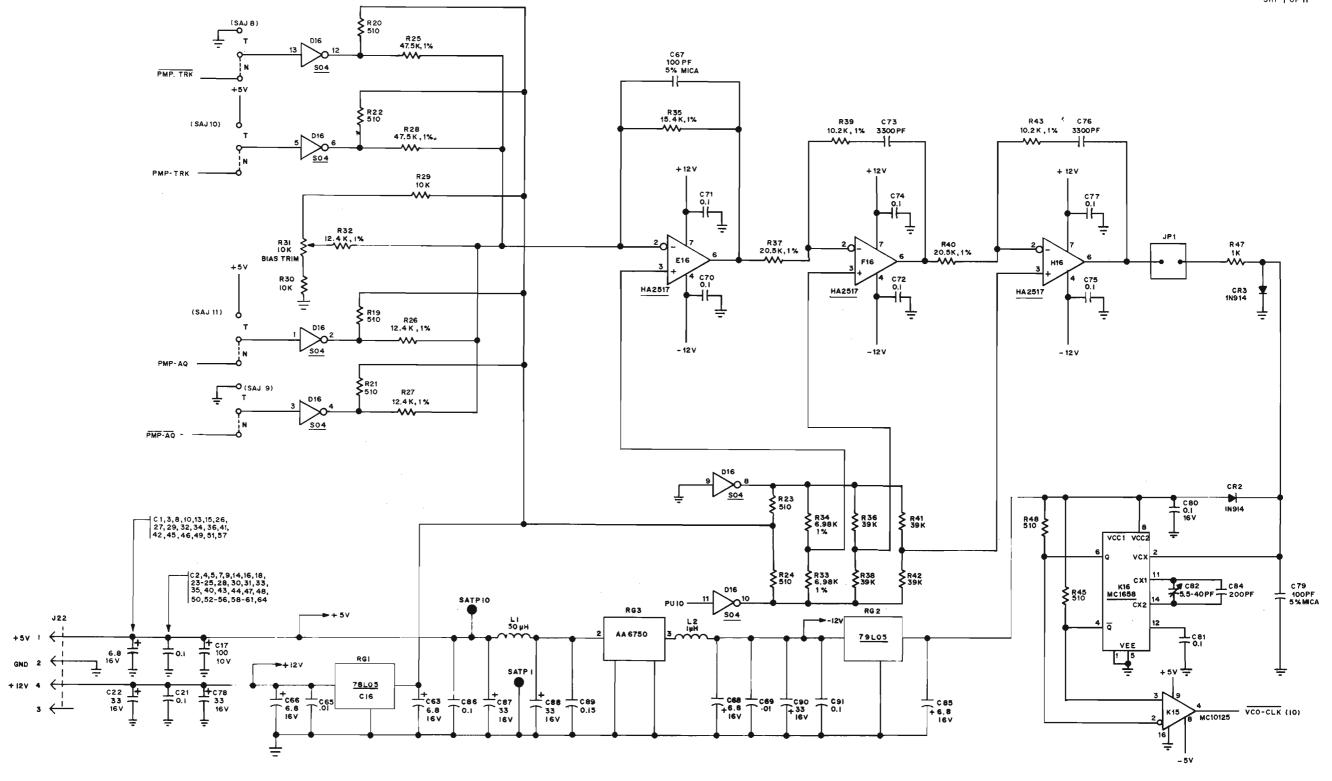

#### 2.2.7 TAPE INTERFACE

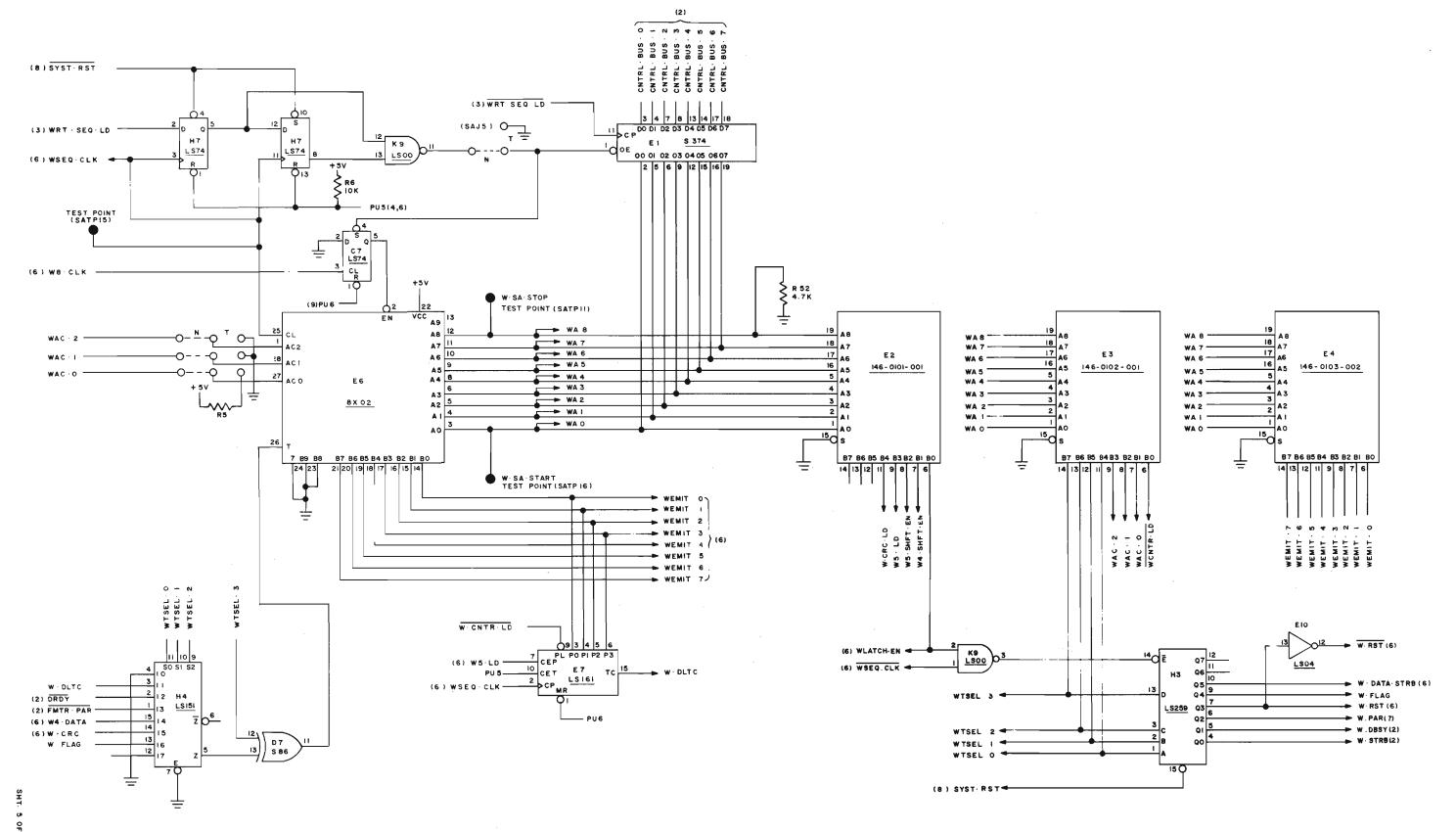

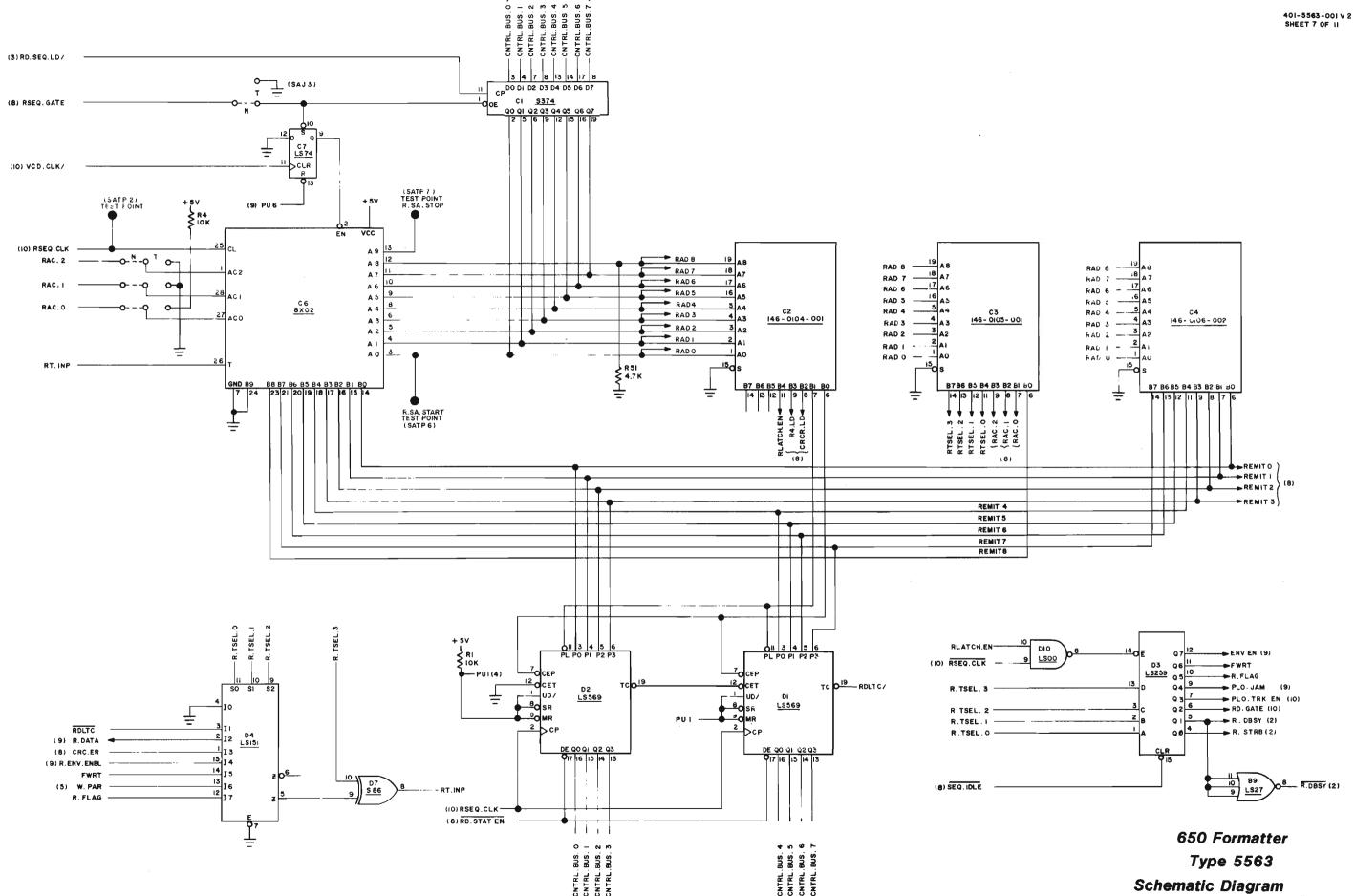

The controller provides an interface to Kennedy Model 6455 and 6470 Cartridge Tape Units, both of which consist of a cartridge formatter and a tape drive. The formatter controls read and write operations in a self-clocking mode complete with serial error detection (CRC). It executes 19 commands, including generation of file marks and space one record in either forward or reverse direction.

Interface to the tape unit is provided by the Kennedy Pico Bus Interface which consists of a bidirectional 8-bit data bus using odd parity, write and read parity bits, four handshaking control signals, a data strobe and a cable monitor signal. Any information sent to the controller begins with a command and is followed either by data or the tape unit's response to the command. The tape unit determines whether it is receiving a command or data when it receives either CREQ (Command Request) or DRDY (Data Ready). /CMON (Cable Monitor) indicates whether the cable between the slave and tape unit is connected. When the cable is disconnected, /CMON is high.

The slave CPU initiates all transfers to and from the controller by issuing one of 19 possible commands. /OUT06 sets the Command Request (CREQ) control signal and, after a time delay, the controller responds with CBSY (Command Busy). CBSY remains active until the tape unit is through processing the present command. Commands must NOT be sent while CBSY is active. The controller's course of action after CBSY is set depends upon the particular command. It can return one or two status bytes and latch them into separate registers, it can write a track address to the tape unit, or it can transfer tape read or write data. Fig 2-6 displays a block diagram of the control signal generating logic. Fig 2-7 and 2-8 display block diagrams of the Tape Interface receive and transmit data paths.

During tape data read or write operations, an /INO5 or /OUTO5 command sets Data Ready (DRDY), a control signal which is acknowledged by Data Busy (DBSY). The actual data transfer does not take place until DBSY goes active. /OUTO5 also latches the next byte of data to be written to the tape unit. /INO5 reads the tape read data latch. Each byte of data (whether command, status, or data) is either clocked in by or acknowledged by a STROBE signal from the tape unit.

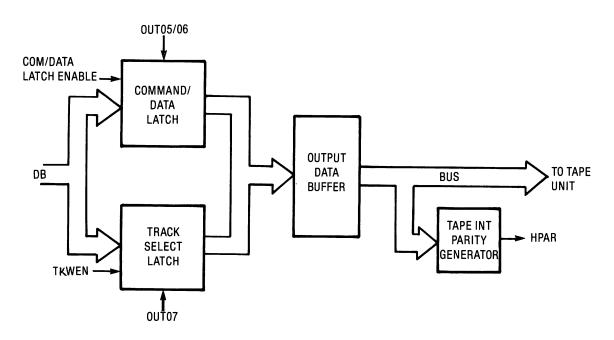

Figure 2-6 Tape Interface Control Block Diagram. Control signals for tape unit-tape interface interaction are generated by Tape Interface Command Decoder and associated logic. Logic decodes commands to issue appropriate control signals to tape unit and within the controller. Diagnostics Control Latch issues signals to control testing of the controller. Formatter Clear logic issues FCLR to clear tape unit via /OUTO4 command.

Figure 2-7 Tape Interface Receive Data Path Block Diagram. Data is read from memory into Input Data Buffer and through to Status Latches. All single-byte command data is read through Status Latch Two. Status Latch One is used only for SENSE STATUS Command where two bytes of data are requested. Data is passed from Status Latch to DB Data Bus upon receipt of ported input commands.

Figure 2-8 Tape Interface Transmit Data Path Block Diagram. Data from DB Data Bus is passed into Command/Data or Track Select Latch. Data is sent to tape unit in appropriate sequence via Output Data Buffer. Control of this operation depends on signals generated from Tape Interface Control logic. See Figure 2-6.

#### 2.2.7.1 Tape Commands

Tape commands are performed by an /OUT06 command with data set to the corresponding function code. Model 6455 has 19 valid function codes in the range of 00-12H. All other function codes are illegal and result in Command Errors. Table 2-3 lists current function codes. (Additional function codes will support Model 6470.)

All motion commands used by the Model 6455 can take advantage of the command "on the fly" feature available in the drive formatter software. When the same command is executed within 300 us of the Command Completion interrupt (CBSY goes off), the new command is executed without the drive beginning its standard ramp to a stop procedure. As a result, command execution overhead delay is reduced from 50 ms (25 ms to ramp down plus 25 ms to ramp back up) to 25 ms. The command "on the fly" does a standard ramp to a stop if the next command is in the opposite direction.

#### Table 2-3 Command Function Codes

CODE OOH - SENSE IDENTITY. Requests an identity byte from the tape unit. A value of OlH identifies the device as a cartridge tape unit. After the Command Completion interrupt, /INO6 reads the identity byte.

CODE Olh - SENSE CONFIGURATION. Requests a Software Revision Level Byte from the tape unit. After the Command Completion interrupt, /INO6 reads the Software Revision Level Byte. The present value of the Software Revision Level Byte is OAH.

CODE 02H - SENSE STATUS. Requests two status bytes from the tape unit. After the Command Completion interrupt, /IN09 reads the first status byte (Summary Status) and /IN06 reads the second status byte (Position Status). The tape unit resets the Error Status Bits after status has been sensed.

CODE 03H - REWIND. Causes tape unit to rewind at maximum speed (70 ips) and position the tape at the Logical Load Point (LLP) of Track 0.

CODE 04H - LOAD. Loads a tape cartridge into the tape unit. After the operator inserts the tape cartridge into the tape unit, Summary Status Bit 5 (No Cartridge) goes false to indicate proper insertion. Summary Status Bit 7 (Not Ready) remains active until the LOAD operation is successfully completed. Prior to execution of the LOAD sequence, the tape unit performs a self-test of formatter electronics. Successful completion of this self-test is required to proceed; otherwise, Summary Status Bit 4 (Formatter Error) is set. Finally, the tape is positioned at the Logical Load Point (Track 0) of the tape cartridge.

## Table 2-3 Command Function Codes (continued)

CODE 05H - UNLOAD. Causes tape unit to rewind at maximum speed (70 ips) and position the tape at End of Tape (EOT). Summary Status Bit 7 (Not Ready) goes active upon successful completion of the UNLOAD operation, allowing proper removal of the tape cartridge.

CODE 06H - TRACK SELECT. In combination with Track Address/Placement Byte, causes tape unit to select the indicated track and reposition the tape to the Logical Load Point or Logical End of Tape (LEOT) at maximum tape speed (90 ips). Before TRACK SELECT is executed, /OUT07 must be issued to write the Track Address/Placement Byte Register.

CODE 07H - ERASE. Causes tape unit to erase tape in the forward direction at maximum tape speed (70 ips). Tape unit senses the Logical End of Tape and stops automatically.

Code O8H - SPACE FORWARD. Causes tape drive to proceed forward from an Inter-Block Gap (IBG) to the next IBG at normal speed. One record on tape is traversed. SPACE FORWARD is constrained to the current track address.

(In the special case in which records are written past the LEOT of track 3, the READ command must be used to move beyond the LEOT.)

CODE 09H - SPACE REVERSE. Causes tape drive to proceed in the reverse direction from an Inter-Block Gap (IBG) to the previous IBG at normal speed. One record on tape is traversed. SPACE REVERSE is constrained to the current track address.

CODE OAH - SPACE FORWARD FM. Causes tape drive to proceed forward from an IBG at normal speed until it senses a File Mark (FM) record. The drive then ramps to a stop in the IBG following the File Mark. The Position Status Byte indicates that the File Mark has been found. If the drive does not find a File Mark record, it stops at the Logical End of Track. SPACE FORWARD is constrained to the current track address.

(For the special case in which a File Mark is written past the LEOT of track 3, the Read command must be used to move beyond the LEOT.)

CODE OBH - SPACE REVERSE FM. Causes tape drive to proceed from an IBG in the reverse direction at normal speed until it senses a File Mark record. The drive then ramps to a stop in the IBG following the File Mark. The Position Status Byte indicates that a File Mark has been found. If no File Mark is found, the drive stops at the Logical Load Point. SPACE REVERSE is constrained to the current track address.

CODE OCH - READ. Causes the tape unit to read one tape record in the forward direction. Before READ is issued, the DMA Controller Chip must be programmed and enabled. It then issues an /INO5 command that reads in data from the tape and transfers it to memory. The tape unit checks the integrity of the data as it is read off the tape via a CRC check and indicates a Data Error in bit 0 of the Summary Status Byte.

## Table 2-3 Command Function Codes (continued)

To read a partial record or if the record being read is longer than anticipated (data overrum), the read byte counter in the DMA Controller Chip must be set to the desired record length (which must be greater than 1). When the read operation occurs, the DMA Controller Chip inputs into memory only the number of bytes programmed into the byte counter. The tape unit, however, continues the read operation until the record has been read completely. When the tape unit has read the entire record, it sets the Tape Command Completion interrupt and the Tape Data Overrun Error Bit (D6), which can be read via an /INOB command). No error condition is indicated in the Summary Status Byte.

When a data underrun situation occurs (in which the length of the record being read is less than that programmed in the read byte counter in the DMA Controller Chip), the read operation terminates normally with no error conditions set in the Summary Status Byte. However, the byte counter in the DMA Controller Chip indicates that less than the desired length has been transferred.

CODE ODH - WRITE. Causes tape unit to write one tape record in the forward direction with standard IBGs. Before WRITE is issued, the DMA Controller Chip must be programmed and enabled. It then issues the /OUTO5 command which reads in data from memory and transfers it to the tape unit. The tape unit performs a read-after-write as the record is written and indicates any data errors in bit 0 of the Summary Status Byte. If the record being written is longer than 17k bytes, the tape unit terminates the operation at 17k bytes and sets the Length Error Bit in the Summary Status Byte.

Any attempt to issue a write command past the LEOT of track 0, 1, or 2 asserts the Command Error Bit in the Summary Status Byte. Records can be written past the LEOT of track 3. However, if the record is written past the physical EOT, the tape unit terminates the operation and sets the Drive Fault Error Bit in the Summary Status Byte.

Before a WRITE is attempted, the Write Protect Bit of the Position Status Byte must be checked. The Command Error Bit of the Summary Status Byte will be set if the tape cartridge is Write Protected.

CODE OEH - WRITE EXTENDED. Causes tape unit to erase approximately three inches on the tape prior to writing the tape record. This procedure lowers the risk of encountering a physical failure area on the tape that may have caused a Data Error when a previous WRITE was attempted. WRITE EXTENDED should be used after a WRITE operation with a read-after-write error and a subsequent SPACE REVERSE command. This function assumes that blank tape exits beyond the record being written.

The Command Error and LEOT bits of the Status Byte will be set, preventing WRITE EXTENDED from being used when the record to be rewritten had passed the LEOT of track 0, 1, or 2.

## Table 2-3 Command Function Codes (continued)

WRITE EXTENDED can write records past the LEOT of track 3. However, if the record is written past the physical EOT, the tape unit terminates the operation and sets the Drive Fault Error Bit in the Summary Status Byte.

#### NOTE

WRITE EXTENDED should not be used for tape editing as loss of position will result.

CODE OFH - WRITE FM. Causes tape unit to write a special coded field on the tape to be used as a tape File Mark (FM). Standard IBGs will be placed on either side of the FM.

WRITE FM has the same restrictions as WRITE when it encounters an LEOT.

CODE 10H - WRITE FM EXTENDED. Causes tape unit to erase approximately three inches on the tape prior to writing the File Mark. This procedure lowers the risk of encountering a physical failure area on the tape that may have caused a Data Error when a previous WRITE FM was attempted. WRITE FM EXTENDED should be used after a WRITE FM operation with a read-after-write error and a subsequent SPACE REVERSE command. WRITE FM EXTENDED assumes that blank tape exits beyond the record being written.

WRITE FM EXTENDED has the same restrictions as WRITE EXTENDED when it encounters an LEOT.

CODE 11H - EDIT. Allows the controller CPU to rewrite a previously written record on the tape. The tape must be positioned in the IBG before the record to be edited. EDIT causes the record to be rewritten in the same way as the WRITE command.

CODE 12H - FIXED THREE INCH ERASE. Erases a fixed three inches of tape.

FIXED THREE INCH ERASE can be used to pass over bad spots in tape or to erase separate records on tape.

#### 2.2.7.2 Status Latches

During tape read operations, a buffer inverts the tape unit's outgoing signals, which then proceed through the buffer to one of the two Status Byte Latches. In a SENSE STATUS Command, the first Status Byte (Summary Status) contains status information and the second Status Byte (Position Status) provides tape positional information. The Tape Command Sequencer routes the Summary Status Byte into Status Latch One and the Position Status Byte into Status Latch Two. The tape unit resets the error bits of the Summary Status Byte as it is read. Operations other then SENSE STATUS use only Status Latch Two.

To clock Status Latch Two, the STRB signal is asserted when a data/status word is read. Status Latch Two is enabled by either /IN05 (Read Tape Data) or /IN06 (Read Tape Status Byte 2).

To read the Summary Status Byte, a signal from the Tape Command Sequencer clocks Status Latch One. This clocking signal is generated by the second STRB signal as the command is passed through a gate. Receipt of /IN09 (Read Tape Status Byte 1) enables Status Latch One. (/IN09 is generated only during the SENSE STATUS command operation.) The last STRB signal is prevented from clocking Status Latch One.

Summary Status Byte and Positional Status Byte bit assignments that are read with the SENSE STATUS Command are shown in Tables 2-4 and 2-5.

Table 2-4 Summary Status Byte

| D0 | DE - Data Error      | Tape record with either a CRC or format error has been detected during a read or write operation. Faulty erase also issues a Data Error.                        |

|----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1 | LE - Length Error    | Tape record larger than 17k bytes (maximum record size) has been written to tape unit.                                                                          |

| D2 | PE - Parity Error    | Tape unit has detected a receive parity error on a command, write data, or track address byte transferred during the last operation.                            |

| D3 | CE - Command Error   | Signals receipt of an illegal function code. Check for parity error (D2).                                                                                       |

| D4 | FE - Formatter Error | Either formatter has failed its self-test or noise has been detected in a gap region during a write operation.                                                  |

| D5 | NC - No Cartridge    | Tape cartridge is not inserted in the cartridge tape drive.                                                                                                     |

| D6 | DF - Drive Fault     | Either a physical or electrical fault<br>has occurred in the tape unit, a tape<br>is broken, or the tape has illegally<br>gone beyond the physical end of tape. |

| D7 | NR - Not Ready       | Tape drive is not ready because a tape cartridge is not properly loaded.                                                                                        |

Table 2-5 Positional Status Byte

| DO | TKBO - Track Bit 0            | Track Address Bit 0 of presently selected track        |

|----|-------------------------------|--------------------------------------------------------|

| D1 | TKB1 - Track Bit 1            | Track Address Bit 1 of presently selected track        |

| D2 | TKB2 - Track Bit 2            | Track Address Bit 2 of presently selected track        |

| D3 | EOT - End of Tape             | Indicates physical end of tape                         |

| D4 | WP - Write Protect            | Write protect plug on tape cartridge has been detected |

| D5 | FM - File Mark                | Special file mark record has been detected on tape     |

| D6 | LEOT - Logical<br>End of Tape | Logical End of Tape has been detected                  |

| D7 | LLP - Logical<br>Load Point   | Logical Load Point has been detected                   |

#### 2.3 THE 2200 INTERFACE ASSEMBLY

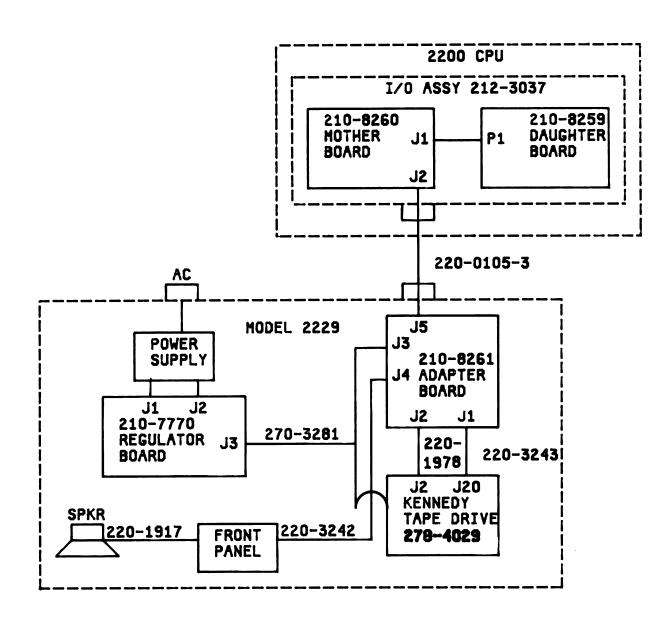

The 2200 Interface Assembly (WLI #212-3037) provides the interface between the Model 2229 Cartridge Tape Drive and the 2200 CPU. The assembly consists of a Motherboard (210-8260) and Daughterboard (210-8259).

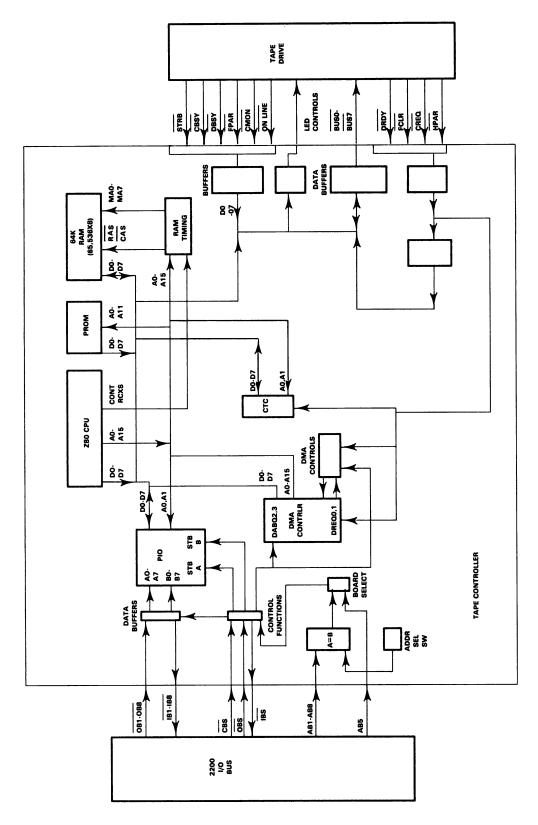

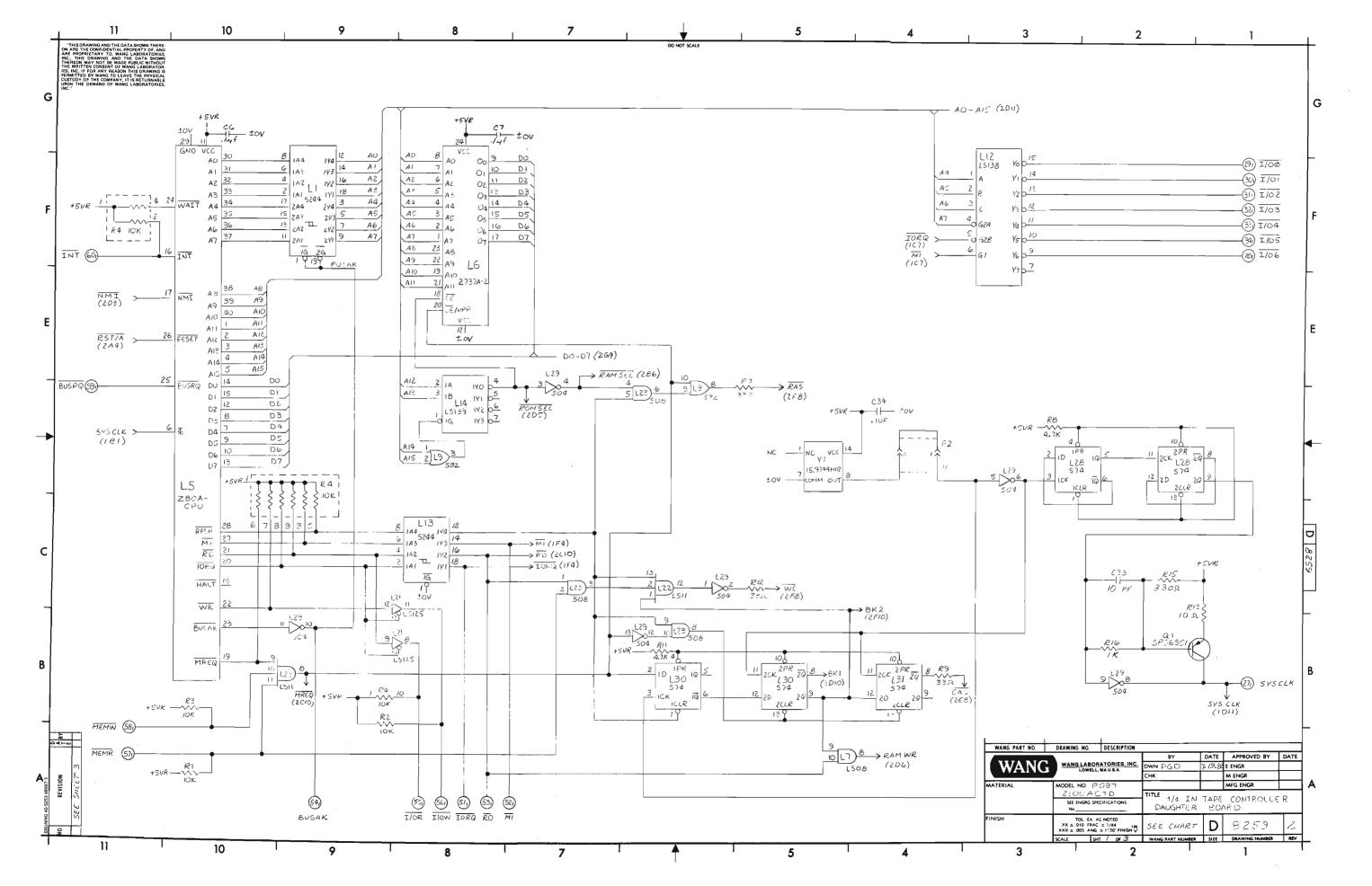

The mother/daughterboard controller interface is plugged into the 2200 system and connected by cable to the Kennedy 1/4" tape drive. The controller contains a Z80A 4MHZ CPU, 64K of RAM with parity, 4K of PROM, Z80A CTC, 9517A-4 DMA, Z80A PIO, and interface logic. Figure 2-9 is a block diagram of the interface assembly circuitry.

PROM occupies the first 4K of memory addressing (0000-0FFF). The RAM occupies the upper 60K of RAM (1000-FFFF). Odd parity is maintained on the 60K array of RAM.

The DMA chip has a total of four transfer channels available. Two channels are dedicated to data transfers between the 2200 and the tape controller while the remaining two channels handle data transfers between the tape controller and the tape drive.

The PIO is used either with or without the DMA to handle command and data transfers between the tape controller and the 2200.

Figure 2-9 Block Diagram of 2200 Interface Assembly

### 2.3.1 2200/CONTROLLER INTERFACE

Communication between the 2200 and the controller is handled by the PIO. The PIO's A Port is dedicated to CBS byte transfers to the controller. Data transfers to and from the 2200 are handled through the B Port.

The Controller can use either of two methods to handle B Port data transfers to and from the 2200. In one method, the PIO is used to transfer data to the Z80 on an interrupt basis. In the second method, the PIO is used with the DMA to transfer bytes directly to RAM without interrupting the CPU until the end of the transfer.

When the controller receives a command byte which specifies the use of a block data transfer from the 2200, it can set up the DMA to handle the transfer. From that point the DMA chip will handle the block data transfer to or from the 2200 while the CPU is free for other processing. When the transfer is complete the DMA will interrupt the CPU.

## 2.3.1.1 Port B Data Transfers (DMA mode)

The PIO is used for a holding register during DMA transfers. The PIO receives the OBS strobe and latches the data. The Ready line from the B Port is used to generate a DMA transfer request. The DMA reads the PIO B port and moves the data to RAM. The PIO does not generate an interrupt of the CPU.

# 2.3.1.2 2200/Controller Data Transfers (Interrupt Mode)

In the interrupt mode, the A Port is set up for CBS characters and the B Port is used to interrupt the CPU when a byte is sent or received.

The CPU sets up the A port and enables interrupts on the A port only. The B Port is not allowed to interrupt the CPU until after being set up for the correct sequence.

### 2.3.2 TAPE INTERFACE

The Kennedy 6455 Tape Drive assembly consists of a Model 640 Tape Drive and a Model 650 Formatter. The Model 640 Tape drive is the mechanical tape transport and support electronics. The Model 650 Formatter is the microprocessor based electronics board to control the drive. The formatter handles the interfacing of signals and data between the host system and the tape drive system.

The tape drive configured for 2200 systems contains a small interface board (210-8261). This board supplies the power and ground signals for the front panel, separates the signals on the cable from the controller board into the group of signals going to and from the front panel and the tape drive. The board also contains the interface logic for the "On Line" Switch.

## 2.3.2.1 Control Signals

CREQ Signal -

The CREQ signal (Control Request) is used to indicate to the tape drive that a command or parameter byte transfer is being executed.

CBSY Signal -

The CBSY signal is used by the tape drive to indicate to the controller that the drive is executing a command sequence. This signal will remain active until completion of the command. In cases of one byte operations where no tape motion is involved, CBSY goes inactive shortly after STRB goes inactive. In cases where tape motion is involved, CBSY will not go inactive until after tape motion has stopped. This may be a time period of up to 90 seconds or more depending on the command. During read/write commands, CBSY will stay active after DBSY has gone inactive because tape motion will continue after data transfers are completed.

DBSY -

The DBSY signal is used by the tape drive to indicate to the controller that a transfer of data either to or from the tape drive is in progress. This signal will go active after CBSY to indicate a command sequence in progress. DBSY indicates data transfers within that command sequence.

STRB -

The STRB signal is used by the tape drive to acknowledge receipt of a command or parameter byte from the host, to acknowledge data byte transfers during write operations and as a strobe to transfer data to the controller during read operations.

### 2.3.2.2 Commmand Transfers to the Formatter

Signals -

CREQ - (Control Request)

CBSY - (Controller Busy)

STRB - (Strobe)

FCLR - (Formatter Clear)

Commands are sent to the formatter as part of an instruction sequence. The CBSY signal is active for the entire duration of an instruction. When the controller sends a command byte to the formatter, the CBSY line from the formatter goes active. If the command requires additional byte transfers or some activity by the drive, the CBSY line stays active until the last transfer or drive activity is completed. The total number of byte transfers, the direction of each byte, and type of drive activity is determined by the individual instruction.

When CBSY is inactive, the controller sets up the command byte on the data bus to the formatter, waits 150ns to allow for settling of the bus, and asserts CREQ to initiate the transfer to the formatter. The formatter accepts the command (if valid) and turns on CBSY to the controller. When the controller sees CBSY go active, it drops CREQ.

If additional bytes are to be transferred to or from the tape unit, the controller sets up the data bus for correct direction (input or output). If an output (to the formatter) is required, the controller sets up the byte on the bus to the formatter and asserts CREQ. The formatter sees STRB and drops CREQ. If a second byte is to be sent, the sequence repeats. If no additional transfers are required, the formatter turns off CBSY after completing the operation to indicate the end of the instruction. If STRB is not received from the formatter in less than 500us, the host disables CREQ and the sequence terminates.

### 2.3.2.3 Parameter Transfers to the Host

```

Signals -

CREQ - (Control Request)

CBSY - (Controller Busy)

STRB - (Strobe)

```

After the command byte has been sent, the controller sets the data bus to input mode (to the controller) and again asserts CREQ. The formatter places it's data byte on the bus and asserts STRB. The controller acknowledges receipt of the data by turning off CREQ. On seeing CREQ turn off, the formatter turns off the data on the bus and drops STRB.

### 2.3.2.4 Data Transfers to the Formatter (Write)

```

Signals -

DRBY - (Data Ready)

DBSY - (Data Busy)

CBSY - (Controller Busy)

STRB - (Strobe)

```

The host places the first data byte on the bus, waits 150ns, and asserts DRDY to the formatter. When the formatter sees the DRDY line go active, it asserts DBSY to indicate that it is busy with a data transfer, and 1.5us later asserts STRB to acknowledge receipt of the byte. After this, the formatter sends STRB pulses to the controller every 42us. The STRB pulse causes the controller to set up the next data byte on the bus. When the last byte has been transferred, the controller turns off DRDY to indicate the end of transfer to the formatter. The formatter responds by turning off DBSY. After the formatter completes the write operation including writing the gap, CBSY is turned off.

# 2.3.2.5 Data Transfers to the Host (Read)

Signals -

DRDY - (Data Ready) DBSY - (Data Busy)

CBSY - (Controller Busy)

STRB - (Strobe)