# 2200 MVP COMPUTER ARCHITECTURE

Author: Bruce M. Patterson

November 30, 1979

#### System Architecture

Wang 2200 computer systems employ a direction execution high-level-language (HLL) architecture. With direct execution HLL systems the HLL is effectively the machine language of the computer. Unlike more conventional architectures where the source code is transformed into a distinct object code before processing, the direct execution system processes the source code directly.

The direct execution system provides a number of advantages over more traditional architectures, not the least of which is its conceptual simplicity. The more conventional layers of software including assemblers, linkage editors, compilers, and loaders are eliminated. The inherent conversational nature of the system facilitates programming and debugging. The debug run and execution run are identical. Error messages can easily include a listing of the actual source code. Program execution can be halted, single stepped, and restarted. Since there is no compilation phase, the system responds immediately to program entries and modifications. Programmers can understand the language semantics by observing the direct response of the system.

The 2200 provides the user with a single HLL, BASIC-2, which is used for all programming. Proficiency in system use is easily achieved since there is only one language to learn. A fundamental design criterion in the development of BASIC-2 was to provide a self-sufficient language that would be as flexible as conventional general purpose computer instruction sets. I/O and data handling language extensions provide the user with flexibility not usually found in a high-level-language.

The 2200 is not a pure direct execution machine since the source code is preprocessed into a form more memory conservative and more efficiently interpreted. However, source and object differences are such that the preprocessor transformation is nearly completely reversible. As a result, only the condensed code is stored in the machine. The preprocessing function eliminates gross inefficiencies in memory, timing, and logic requirements.

#### 2200 Hardware

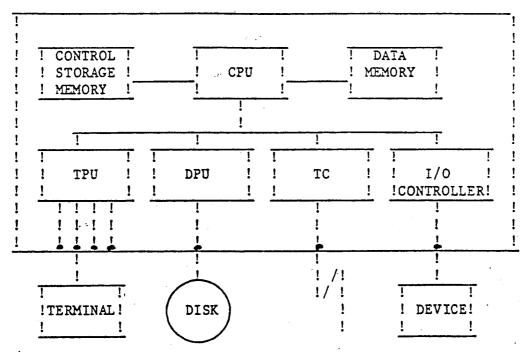

2200 computers consist of a microprogrammed MSI processor coupled with a number of special purpose LSI I/O processors and controllers. The OS and language interpreter reside in a large control storage memory which is independent from user data memory; this microprogram directs the execution of the CPU and coordinates communication with the I/O processors. The independent I/O processors permit the overlap of the CPU and I/O processing. The CPU is relieved of the responsibility for controlling peripherals that would otherwise require frequent or dedicated CPU attention.

Figure 1 2200 System Block Diagram

The 2200 CPU is a pseudo 16-bit processor using a 3-bus architecture for interconnecting a bank of general purpose, status, and I/O 8-bit registers and the ALU. A microinstruction can address these registers as double, single, or half registers for performing 16, 8 or 4-bit operations. In addition, a bank of 16-bit registers that can be exchanged with the data memory address pointer provides quick access to major system pointers. The extensive microinstruction set consisting of 24-bit words provides decimal and binary arithematic, logical operations, and a wide variety of conditional branching instructions.

In a single CPU cycle, a 24-bit microinstruction can be fetched, 16-bits of data memory can be fetched, and a 16-bit operation can be performed. The wide memory path, 600 nsec. cycle time, and rich microinstruction set provides a highly effective processor for implementing direct execution languages.

User programs and system controllers are kept in data memory, of which 256K can be installed. Since the CPU's address space is limited to 64K, however, data memory is divided into 64K banks. In order to provide the microprogram with access to control tables without switching memory banks, the lower 8K of the address space always refers to bank 1. The lower 8K of banks 2, 3, and 4 is not used.

13353

#### MVP Operating System

The 2200 MVP multiprogramming operating system allows several users to share a single computer effectively. To accomplish this, the operating system divides the resources of the computer -- memory, peripherals, and CPU time, -- among the users. Once each user has been allocated a share of the computer resources, the operating system acts as a monitor, allowing each user to utilize the system in turn while preventing the various users from interfering with each other's computations.

The MVP employs a fixed partition memory scheme. User memory is divided into a number of sections or "partitions", each of which can store a separate program. From the user's point of view, each partition functions independently from the other partitions in the system. Each user may LOAD and RUN BASIC software, compose a program, or perform Immediate Mode operations. As in a single-user environment, the user has complete control over his or her partition. No user on the system may halt execution in, or change the program text of, a partition controlled by another user.

Each terminal may control several partitions executing independent jobs. At any given time, however, only one of these partitions is in control of the terminal and thus capable of interacting with the operator. The partition in control of the terminal is said to be in the "foreground." Other partitions assigned to the terminal may continue to execute in the "background" until operator intervention becomes necessary.

Although partitions in general function independently of one another, there are situations in which it is useful for two or more partitions to cooperate. Cooperating partitions may share program text and/or data. The sharing of commonly used programs and data by several partitions eliminates needless duplication and produces more efficient use of available memory. The integrity and independence of a partition which contains shared programs or data are maintained by requiring the partition to explicitly declare itself to be global (sharable) before it can be accessed by other partitions. Correspondingly, a partition wishing to access shared text or data in a global partition must identify the desired global partition.

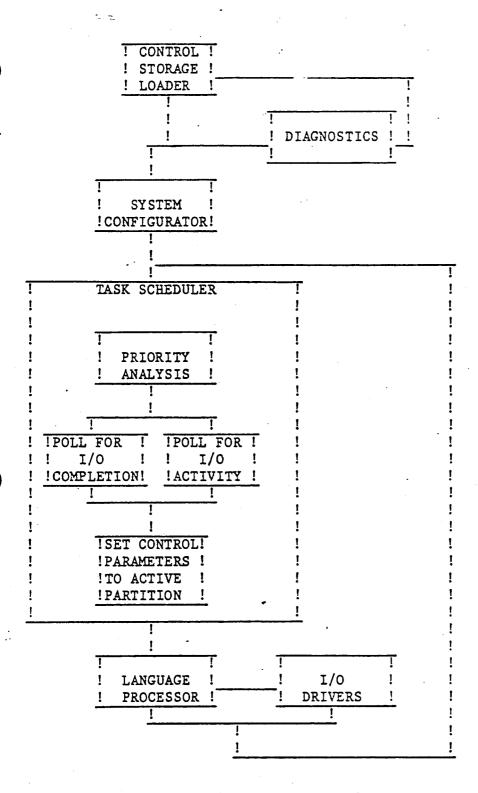

Figure 2 Block Diagram of 2200 MVP OS

To the programmer who regards the MVP system as a whole, it appears that all partitions are executing simultaneously. Because all partitions share a single CPU, however, only one partition can be executing at any given moment. The operating system creates the illusion of simultaneous execution of several programs by rapidly switching from one to the other in turn.

Partitions in the 2200 MVP are serviced by the CPU in a "round-robin" fashion, with priority given to I/O operations. Each partition in turn is given a "timeslice" 33 milliseconds (ms) in duration. The CPU has a 30 ms timer which is set at the beginning of the timeslice; at the completion of each BASIC statement (and at various points in the middle of long statements and I/O operations), the clock is checked to see whether the 30 ms timeslice has been exhausted. When a partition's timeslice has expired, the operating system saves the status of that partition so that it may be restored later when that partition's turn comes around again. The operating system then loads the status of the next partition in line and begins its 30 ms timeslice. The process of halting execution of a partition at the end of its timeslice is called a "breakpoint".

Timeslices do not always last exactly 30 ms. Unlike many operating systems, the MVP switches users (breakpoints) whenever it is convenient rather than strictly by the clock. This technique reduces the amount of status information that must be saved, giving the MVP low operating system overhead when compared with most other multiuser systems. More importantly, breakpoints may occur in the middle of BASIC I/O statements. If, for instance, the current partition attempts a disk access and the disk is hogged by another partition, this condition is quickly detected and a breakpoint occurs. I/O breakpoints differ from program breakpoints in that the partition is specifically marked as "waiting for I/O". When the partition's turn comes around again, the system takes only a few microseconds to decide whether processing may proceed or whether the partition is still waiting for the I/O device and may be bypassed. Thus, if a printer goes "busy" while it performs some mechanical function or if a partition that does not currently control the terminal attempts to write to the CRT, the system bypasses that partition almost as effectively as if it were removed entirely from the system until the I/O device becomes available.

#### MEHORANDUM

TO:

2600 Distribution

FROM:

F. Vine, B. Patterson

DATE:

August 27, 1975, Revised September 12, 1975

SUBJECT:

Revisions to 2600 Hardware Structure

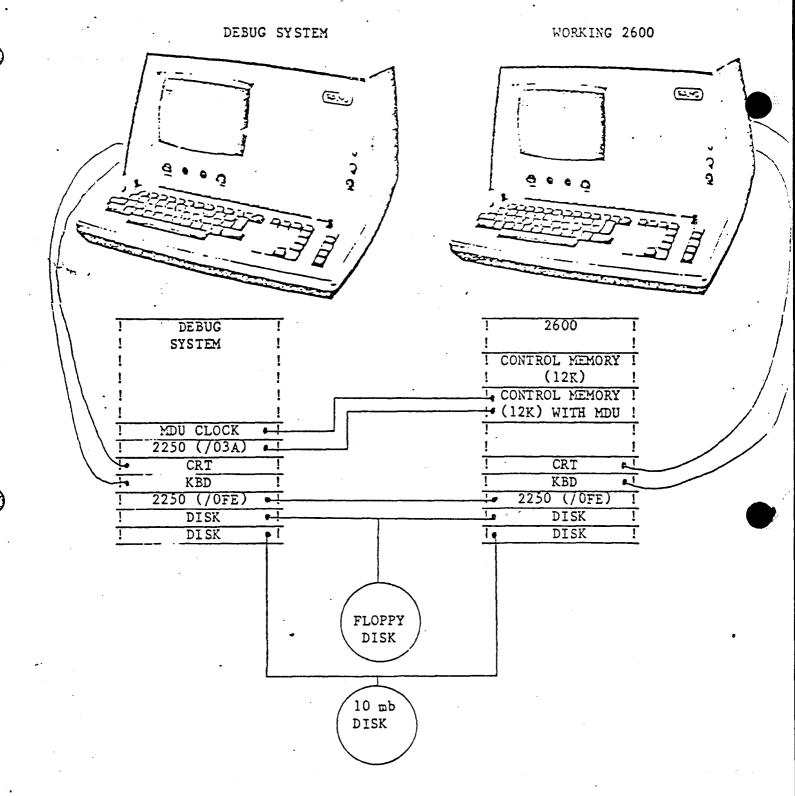

This memo describes changes, as understood by 2600 microcoding groups, to the 2600 CPU specifications described in the document "2600 Calculator Structure" dated December 6, 1974, Revised February 14, 1975. Additional specifications are also provided. Updated pages for the specifications document are included. If any specifications are incorrect, please provide corrected specification A.S.A.P.

1. Deletion of binary add (A) instruction

The register instruction binary add (A) has been eliminated from the micro-instruction repertoire. The binary add with carry (AC) instruction suffices since carry can be set off at the beginning of the instruction. Note, that the AI and ACI instructions have not been eliminated.

2. Addition of binary subtract with carry (SC) instruction

The register instruction binary subtract with carry (SC) replaces the A instruction.

3. Write control memory (SR, WCM) instruction

The SR, WCM instruction requires that the high 8-bits of the instruction being written (K register) be complemented; PH, PL remain as originally specified (true, uncomplemented).

The data read by a SR, RCM instruction is true in K, PH, and PL.

Write to data memory on an extended register instruction

In an extended register operation with write to data memory specified, the high order byte of the result is written (i.e., the result of the 2nd half of the operation).

#### Instruction timings 5.

The cycle time is 600 nanoseconds for all instructions except for the following 3 that execute in 800 nanoseconds:

BLERX BLRX SR

and the following 2 instructions that execute in 1.6 microseconds.

and the following instruction that execution in 1.1 microsecond LPI. SR, WCM

Trap addresses (located in PROM/ROM bootstrap area) 6.

8000 - PECM (parity error in control memory)

8001 - RESET

8002 — PEDM (parity error in data memory)

8003 - POWER ON

8004 — 800F (spares)

Load PC's immediate instruction extention 7.

> Write to data memory (W1, W2) are legal on LPI instructions; however, the data written is always zero since there are no extra bits available to specify what is to be written. In previous specifications write was illegal on LPI instructions.

Parity specifications

Page 14 describes instruction and data parity and parity errors.

#### MEMORANDUM

TO:

2600 FILE

FROM:

Bruce Patterson

DATE:

December 6, 1974, Revised February 14, 1975, Revised Sept. 12, 1975

SUBJECT:

2600 Calculator Structure

The following memo describes the 2600 structure as of December 1, 1974. I/O specification will be described in another document. The following list summarizes the major changes to the specifications presented in the memo "2600 Calculator Structure" dated October 11, 1974:

- 1. Due to timing considerations, instructions that reference data memory will use the contents of PH and PL at the beginning of the instruction as the memory address. Previously, the contents of PH and PL at the end of the instructions were to be used. The LPI instruction is the only exception to the rule; if an LPI instruction specifies a read or write, the new contents of PH and PL will be used as the memory address.

- 2. The codes for the Mini Instructions and SHFT instruction have been slightly changed for easier decoding.

- 3. The instructions that Read and Write control memory (RCM, WCM) have been replaced by 2 new instructions (SR, RCM and SR, WCM).

Note, that the SHFT instruction has been modified so that either the high or low 4-bits of both the A and B BUS registers can be specified. Also, A-BUS specification of PC incrementing and decrementing is disabled during extended operations.

#### MEMORANDUH

TO:

2600 File

FROM:

Norman Lourie, Bob Kolk, Bruce Patterson

DATE:

October 11, 1974, REVISED December 5, 1974, REVISED February 14, 1975,

REVISED September 12, 1975

SÜBJECT:

2600 Calculator Structure

This memo will specify in detail the register structure, instruction set and memory referencing structure for a 24-bit micro-programmed processor which is planned for the 2600. Although maintaining the A, B, C bus structure of the 800 micro-processor, it has a number of features which will significantly improve speed, code efficiency, and capacity.

## A. Register Structure

Figure 1 illustrates the tentative register structure for the processor.

The processor will contain 15 8-bit registers which can be read and/or written by micro-program instructions, an arithmetic logic unit and registers for holding the current 24-bit micro-program instruction and 16-bit address, and 32 16-bit auxiliary registers which back up the Data Memory Program Counter. In addition, an 8-bit dummy register exists, the dummy register cannot hold data; its value is always zero. Also, a 95 level subroutine stack is provided to allow efficient subroutine calling.

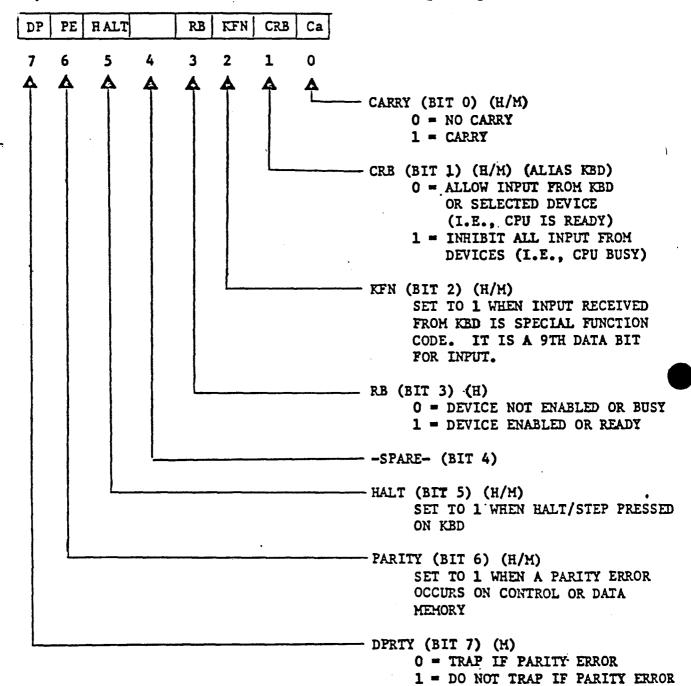

## (1) SH - Status Register High

An 8-bit register used to sense or set various arithemtic, I/O, and keyboard status conditions. It has the following assignments:

NOTE: (M) = Set by microprogram only.

(H) = Set by hardware only (D. C. level).

(M/H) = Set by microprogram or hardware.

# (2) SL - Status Register Low

An 3-bit status register used by the micro-program to indicate phase of processing, mode, and other conditions. This register is set only by the micro-program.

## (3) PH, PL - Data Memory Program Counters (PC's)

These 2 registers are used to hold the 16-bit current address of data words which are read from and written into Data Memory or Control Memory.

Data memory reads and writes are specified in the register instructions by use of the DD bits. For writes, 8-bit data is written from the C-bus to the Data memory location specified by the initial contents of the PC registers. For reads, 16-bits of data are read into the CH and CL registers. The details of memory addressing are described in a later section.

The PC's are also used for reading and writing the low 16-bits of a 24-bit instruction in control memory.

# (4) K - Keyboard Input and I/O Registers

This 8-bit register is used to receive keyboard input and to receive and send data to and from other I/O devices. The K register is also used to read or write data to Control Memory.

# (5) FO - F7 - File Registers

These eight 8-bit registers are general purpose registers which will be used to perform arithmetic computations and related calculator processing. The file registers can be both source and object registers for any of the register transfer micro instructions.

# (6) ALU - Arithmetic Logic Unit (5-bit path)

This unit is used to perform the addition, subtraction, and Boolean functions specified by the micro-program instructions.

Eight-bit data paths are input from the A and B bus and output to the C-bus. For add instructions, a carry bit is also transferred between the ALU and status register bit  $SH_0$ , if specified.

#### (7) AUX 0 - 1F - Auxiliary PC Save Registers

There are up to 32 16-bit registers which are used to temporarily save and restore the contents to the Data memory program counters (PH, PL). Sixteen bit transfers of PC's  $\rightarrow$  AUX and AUX  $\rightarrow$  PC's and a sixteen bit exchange are provided. These operations are extremely useful when Data is being moved, or when two sets of data are being operated on at the same time. When the address is transferred (or exchanged) to the Auxiliary registers, a 16-bit incrementing or decrementing of  $\pm$  1,  $\pm$  2, or  $\pm$  3 can be specified on the data received by the auxiliary register by certain mini-instructions.

The AUX registers are selected by the five Ax bits of the mini-instructions which specify the transfers and exchange.

## (8) CH, CL - Data Memory Read Buffers

These two 8-bit registers are used to receive the 16-bits of data read from data memory. CH will always receive the 8-bits of data from RAM that is exactly specified by the 16-bit address in PH, PL. CL will receive the 8-bit word located at the address specified in PH, PL but with the low order bit of the address complemented. (i.e., the address in PC's  $\pm$  1).

## (9) IC1, IC2, IC3, IC4 - Instruction Program Counter

The four 4-bit registers contain the current micro-program instruction address. Although these registers are not addressable by register instructions, they are reset by Branch, Subroutine Branch and Subroutine Return Instructions. A 96 level circular subroutine address save stack is available to save and restore the IC register. In addition, commands are available to transfer the PC registers (Data Memory program counter) to and from the stack.

## B. Hemory Addressing Structure

The processor can be considered to have two separate memories:

(1) Control Memory (24-bit RAN)

This RAM memory contains up to 64K of 24-bit words. It holds the micro-instructions. Instructions fetched and executed under control of the Instruction Program Counter, (IC1, IC2, IC3, IC4), which is indexed for sequential instruction execution and reset for branch, subroutine branch and return micro instructions.

Control Memory is available in increments of 4K words, up to 64K words. Since only 10 bits are referenced by some branch instructions, instruction memory can be thought of as paged memory with 1024 24-bit words per page for these instructions and an in-page jump is performed. Other instructions allow full 16-bit (64K) transfers.

(2) Data Memory (8/16-Bit RAM)

Data Memory is the memory which is read and written by the micro instruction. Up to 64K of 8-bit RAM (Random Access Memory) can be addressed.

The memory is addressed by the Data memory program counters (PH, PL). The program counter contains a 16-bit address which addresses a location in RAM.

Reads and writes are done by having non-zero data in the DD bits of register instructions. (00 = no read or write, 01 = read, 10 = write 1, 11 = write 2). For a read, 16-bits are read from Data memory. CH receives the 8-bits of data specified by the address in the PC's. CL receives the 8-bit word located at the address in the PC's but with the low order bit of the address (PL $_0$ ) complemented (i.e., the address in PC's  $\pm$  1).

For a write 1, 8-bits are written from the C-Bus (final result of a register instruction) to the address specified by the initial contents of the PC's. For a write 2, 8-bits are written from the C-Bus to the address in the PC's but with the low order bit of the address complemented. (i.e., the address is PC's  $\pm$ 1).

| •           |                                                              | 13.        | ,        |       | . 1 4          |          |            | 14            | 15 )            | . 13    | 12     |          | 37.         | _            | _        | -        |           |             |          |          |              |

|-------------|--------------------------------------------------------------|------------|----------|-------|----------------|----------|------------|---------------|-----------------|---------|--------|----------|-------------|--------------|----------|----------|-----------|-------------|----------|----------|--------------|

| 1.          | PEGISTER INSTRUCTIONS                                        | :          |          | טיינט | tii.           |          | · ½        | <del></del> - | Carr            |         | 1)     | ***      | iii         | . y          | -        |          | 6<br>1-EĽ |             | <u> </u> | J-1      | 1            |

| -           |                                                              |            |          |       | τ              |          | -          | 1             | <del>!</del>    |         |        | <u> </u> |             |              |          | <u> </u> |           |             | <u>.</u> | _ ,,-,,  | 11.5         |

| I           | 0% - Or                                                      | .0         | 0        | 0     | ٥              | Ü        | ×          |               | Ca C            |         | D      | ç        | C           | C            |          |          |           | A A         |          |          |              |

| 1           | MOR - Exclusive Or                                           | :0         | 0        | 0     | 0              | 1        |            | 0             | Ca Ca           |         | D<br>D | C        | C           | C            | C        | ٨        |           | A A         | . !      |          |              |

| 1           |                                                              | :0         | Ü        | ö     | li             | ï        |            |               | CA C            |         | ט      | C        | C           | C            | C        |          |           | ۸ ۸         | · (1 -   |          | В            |

|             | SC = Binary Subtract with Carry DAC = Decimal Add with Carry | Ô          | ō        | ì     | İō             | Ĉ        | ÿ          |               | Ca Ca           |         | n      | c        | č           | Č            | č        | À        | ٨         | A A         |          | -        | В            |

| }           | PSC - Decimal Subtract with Carry                            | ō          | Ü        | ī     | 10             | ì        | x          | 0             | Ca Ca           |         | b      | c        | č           | C            | č        | À        |           | A A         | 15       |          | E            |

| Ì           | AC - Einary Aud with Carry                                   | C          | 0        | ī     | 1              | ō        |            | Ō             | Ca C            |         | b      | c        | č           | č            | Č        | ۱        |           | Â           | I D      |          | נו           |

| 1           | H - Binary Multiply                                          | į0         | 0        | 1     | 1              | _ 1_     | _ ::       | 0             | 115 114         | , )     | D      | c        | С           | C            | Č        | A        |           | Ä Ä         | 1,       | B        |              |

|             | SUFT - Shift                                                 | ·0         | 0        | 0     | iib            | H.a      | _ ::       |               |                 | _ 1>    | p      | c        | С           | С            | Ċ        | ٨        |           | Å Å         | В        | _        | 3            |

| 11.         | INSTRUCTIONS                                                 | i          | -        | )rco  | b::            |          | 15         | 5.1           | TATE            | ; })    | 1)     | -        | C-Di        | l'S          |          | 12       | 2 2:0     | IATE        | 7        | B-DI     |              |

|             |                                                              | <u> </u>   |          |       | <u> </u>       |          | · (        | 111(          | <del>i</del> i) | 1       |        | <u> </u> |             |              |          |          | (LO       |             |          |          |              |

| 1           | ORI - Or Immediate                                           | 0          | 1        | 0     | ١,             | ٥        | : <b>1</b> | 1             | ļ, ,            |         | מ      | c        | С           | С            | С        | ١.       | 1         |             |          |          |              |

| 1           | XORI - Exclusive Or Immediate                                | 0          | î        | Ö     | ŏ              | ì        | 1          | ī             | i i             | D       | נו     | c        | C           | Č            | Č        | ī        | _         | II          | B        |          | 3            |

| i           | A'DI - And Imediate                                          | 10         | ī        | ŏ     | li             |          | :î         | î             | li i            | D       | D      | ľċ       | č           | c            | _        | i        | -         | l I         | 13       | 3        | . B          |

| 1           | AI - Binary Add Immediate                                    | 10         | ī        | ō     | ļī             | ĭ        |            |               | ii              | . D     | D      | c        | Č           | č            |          |          | i         | † †         | 1.       | B        | -            |

| I           | DACI - Decimal Add with Carry Immediate                      | ٥          | ī        | ì     | lō             | ō        | 1          | ī             | li i            | D       | D      | c        | č           | Č            | č        | i        |           | ii          | 1:       | R        | 7            |

|             | DSCI - Decimal Subtract with Carry Irmed                     |            | 1        | 1     | 0              |          | I          | Ī             | i i             | ם       | D      | c        | č           | č            | č        |          | _         | ii          | B        | R        | R            |

|             | ACI - Binery Add with Carry Immediate                        | ;O         | 1        | 1     | 1              | 0        | I          | I             | III             | ת       | D      | c        | С           | C            | Ċ        |          | ī         | īī          |          | -        | , n          |

| L           | HI - Binary Hultiply lunediate                               | <u>`0</u>  | 1        | 1     | 1              | 1        | 0          |               | 11°p -          | ' D     | D      | С        | C           | C            | С        | I        | I         | 1 1         |          | B        | В            |

| III.        | MINI INSTRUCTIONS                                            | -          |          | PCO   | <del> -</del>  |          |            |               |                 | ı D     | D      |          |             |              |          |          |           |             | 1        |          | _            |

| 1111        | .II.II INSINGIAGO                                            | +          |          | -     | ٢              |          |            | _             |                 | ٣_      | ַ      | _        |             |              |          | _        |           |             | 丄        | b-ei     | .s           |

| 1           |                                                              | 0          | 0        | 0     | 1              | 0        | 0          | 1             | 1               |         |        | ŀ        |             |              |          | l        |           |             |          |          |              |

| 1           | TAP - Transfer Aux to PC's                                   | lo         | 0        | 0     | 1              | 0        | 1          | 1             | 1 -             | 'n      | D      | 0        | •           | _            | λx       | Λx       | λx        | Ax. A       | . d 8    | В        | В            |

| 1           | TPA - Transfer PC's to Aux                                   | P          | 0        | 0     | 0              | 0        | 0          | 1             | 1 ±             | D       | D      | 0        | In          | In           | Αx       | Ax       | Ax        | Ax A        | хB       | . 3      | В            |

| ŀ           | XFA - Exchange PC's to Aux                                   | Ю          | 0        | -     | 0              | 0        | 1          | 1             | 1 +             | ย       | ν      | 0        |             |              |          | Ax.      | Αx        | Ax A        | x B      | В        | E            |

| į .         | TPS - Transfer PC's to Stack                                 | 0          | . 0      | 0     | 0              | 1        | 0          | 1             |                 | D       | D      | 0        | In          | ·In          | -        | -        | -         |             | ם        | В        | В            |

| 1           | TSP - Transfer Stack to PC's                                 | р          | 0        |       | 1              | 1        | 0          | 1             | 1 =             | ם       | D      | -        |             | -            | -        | -        | -         |             | В        | . 3      | В            |

| 1           | SR, RCi - Read Control Monory + SR                           | ю          | 0        | -     | 0              | 1        | 1          | 1             | 1 -             | j =     | -      | 0        |             | 1            | -        | -        | -         |             | -        | -        | -            |

|             | SR, WCH - Write Control Henory + SR SR - Subrouting Return   | 9          | 0        | 0     | 0              | 1        | 1          | 1             | 1 -             | -<br> - | -<br>D | 9        | 1           | 0            | -        | -        | -         |             | -        | <u>-</u> | -            |

| 1           | CIO - Control Input/Output                                   | K          | ٥        | i     | 10             | 1        | i          | i             | i               | 10      | -      | 0<br>S   |             | <del>-</del> | <u>-</u> |          |           | <del></del> | В        |          |              |

| i           | cio - comitai imput/output                                   | 6          | ٥        | ō     | lŏ             | ī        | î          | i             | li -            | ١٣      | ٦      | 2        | <del></del> | <u> </u>     | -        | <u> </u> | -         | <u> </u>    | - =      | -        |              |

| [           |                                                              | 6          | 0        | ō     | li             | î        | î          | ī             | i               | 1       |        |          |             |              |          | ŀ        |           |             | 1        |          |              |

| 1           | LPI - Load PC's Immediate                                    | 5          | ō        | ĭ     |                | Ť        | t          |               |                 | ط<br>ا  | ת      | I        | ī           | Ī            | ī        | ī        | ī         | I I         | ┪        | Ī        | <u> </u>     |

| <del></del> |                                                              |            |          |       |                |          |            |               |                 |         |        |          |             |              |          | <u> </u> |           |             | L        |          |              |

| Iv.         | MASK BEARCH INSTRUCTIONS                                     |            | 0        | PCO.  | pΞ             | Г        | ī          |               | BILATIC         | li F    | ITL    | <u> </u> |             |              | _        |          | 11/AS     | ĸ           | 7        |          | !            |

| <u> </u>    |                                                              | <u> </u>   |          |       | ╙              | <u> </u> | !          |               | (N):            | 10-     | nit    | 5)       |             |              | _        |          |           |             | 1        | _        |              |

| 1           | BT - Branch if True .                                        | 1          | 1        | 0     | 0              | ж        | 12         | R             | R R             | P       | R      | R        | R           |              | R        | H        | M         | н н         | ١.       |          |              |

| 1           | BF - Branch 1f Faise                                         | li         | ì        |       | ľi             | רוו      |            | R             | RR              | R       | R      | R        | R.          | R            | R        |          |           | п л<br>К Н  |          | B        | B            |

| 1           | BEQ - Branch 1f - Nask                                       | i          | ī        | 1     | lô             | in.      | 122        | R             | RR              | R       | R      | R        |             |              | R        | H        |           | n n<br>M M  |          | _        | 2            |

|             | BIE - Branch 1f y Mask                                       | i          | ī        |       | 1 -            | 11Ъ      | 13         | R             |                 |         |        |          | R           |              |          | M_       | у.        | <u>K</u> 11 |          |          | В            |

| 1           |                                                              | _          |          |       |                |          |            |               |                 |         |        |          |             |              |          |          |           |             |          |          |              |

| ν.          | REGISTER BRANCH INSTRUCTIONS                                 |            |          | rω    | DE             |          | 1          |               | DUY:            |         |        |          | •           |              |          |          | A-B       | ĽS          |          | B-2      | üS           |

|             |                                                              | 1.         |          |       |                | V        |            | _ [           |                 |         |        | _        |             | _            |          |          |           | •           | Т        |          | _            |

| 1           | BLR - Branch if < Register                                   | 1          | 0        | 0     | ļ              | l X      | ス          | R             | R R<br>R R      | · K     | R      | R        | R           | R            | R        | ۸        | Ÿ         | , ,         | B        | B        | В            |

| 1           | BLER - Branch if - Register BER - Branch if - Register       | +          | Ç        | י     | Ţ              | <u></u>  |            | K             | KR              | II.     | R      | , i      | E .         | K            | E P      | ^        | ۸         | , ,         | B        | _ B      | 5            |

| 1           | BER - Branch if = Register  BUR - Branch if # Register       | 1,         | 0        | 1     | 1,             | 0        | -          | -             | R R<br>R R      | 1.      | -      | <u>۳</u> | T.          | κ<br>υ       | 7        |          | ^·        | ^ ^         | 1.5      | . 5      | 5            |

|             | DOWN - DO MAINT TO T WASTAFEE                                |            | <u> </u> | -     | <del>: *</del> | -\'      |            |               | , N A           |         | -      | ۳        |             |              | ^        | <u> </u> |           | <u>^ ^</u>  | +        |          | _ <b>-</b> = |

| vi.         | BRANCH INSTRUCTIONS                                          | 1          | C        | PCO   | 25             |          | 1          | اريالا        | KGI FI          | ELD     | (1     | ow.      | 10-2        | 11:          | :)       | (1:1     | r,h       | 6-Li        | : [ ]    |          |              |

| i           |                                                              | i.         | _        |       | 1_             |          | 1          | - 1           |                 |         |        |          |             |              |          |          |           |             | Т        |          | ΓI           |

| I           | SB - Subroutine Branch                                       | 11         | ō        | 1     | 0              | 1        | 7          | K             | RR              | R       | R      | R        | R           | R            | R        | R        | R         | RR          | R        | R        | -            |

| L           | B - Unconditional branch                                     | <u>: 1</u> | U        | 1     | 17             | 1        | * !:       | K             | 7 7             | - 11    | K      | LK.      | ĸ           | K            | ĸ        | K        | Ľ         | r R         | I R      | R        | -            |

#### KEY

AAA: A-BUS Register Address

BBB: B-BUS Register Address

CCCC: C-BUS Register Address

DD: Read/Write Specification

00 = no read/write

01 = read

10 = write 1

11 = write 2

Hb, Hs: High/low 4-bits of register

0 = low 4-bits

1 = high 4-bits

II...I: Immediate operand

III.III.

AXAMOMAX: Address of auxiliary register

+ In In: Increment/decrement specification

000 - PC's

001 - PC's + 1

010 - PC's + 2

011 - PC's + 3

100 - PC's

101 - PC's - 1

110 - PC's - 2

111 - PC's - 3

CaCs: Set carry (SH<sub>0</sub>) specification

00 - do not set carry

10 - set carry to 0

11 - set carry to 1

X: Extended operation if X = 1

RR...R: Branch address

S: Set 10B flip-flows if S = 1

# 1. D D - Data Hemory Read and Write Selection Bits

- D D = 00 Null (No read or write)

- D D = 01 Read; 16 bits read from memory into CH, CL where C(PC's) + CH C(PC's with PL<sub>S</sub>) + CL

: :

- D D = 10 Write 1; 8-bit write to memory C-BUS + C(PC's)

- D D = 11 Write 2; 8-bit switched write into memory C-BUS + C(PC's with PL<sub>0</sub>)

## 2. A, B, and C-Bus Register Addressing

| A-BUS E                                                                                                                          | -BUS                       | C-BUS                                     | BINARY ADDRESS                                                      |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------|---------------------------------------------------------------------|

| CL with PC's = PC's - 1 CH with PC's = PC's - 1 CL CH CL with PC's = PC's + 1 CH with PC's = PC's + 1 Dummy with PC's = PC's + 1 | PL PH CL CH SL SH K Duramy | FO-F7 PL PH illegal illegal SL SH K Dummy | 0000 - 0111<br>1000<br>1001<br>1010<br>1011<br>1100<br>1101<br>1110 |

- 1. The B-BUS and C-BUS registers are identical except that CL and CH are illegal on the C-BUS.

- 2. The A-BUS field can specify that the PC address bits be incremented or decremented by 1 at the completion of the instruction.

- 3. When the D D bits specify a read or write and the A-BUS field specifies a PCl = PCl + 1, the read or write is executed before the PC's are incremented or decremented.

- 4. For mini commands with write selected, the B-BUS register will be written (before PC's are incremented or decremented, if applicable).

- 5. The "contents" of the dummy register is always zero.

# 3. X - Extended Operation Bit

Normally, a register instruction performs an 8-bit operation on the specified A-BUS and B-BUS registers and puts the result in the C-BUS register. A BLR (branch less than) or BLER (branch less than or equal) instruction compares two 8-bit registers and branches if the relation is true. In these cases, the extended operation bit is not set (i.e., X = 0).

If the extended operation bit is set (i.e., X=1), a register instruction performs a 16-bit operation on a pair of A-BUS registers with a pair of B-BUS registers and puts the result in a pair of C-BUS registers. A BLR (branch less than) or BLER (branch less than or equal) instruction compares a pair of A-BUS registers with a pair of B-BUS registers and branches if the relation is true.

For extended operations, the register pair is treated as a single 16-bit register. The registers used are determined as follows. The low half of the pair is the register whose address is specified in the instruction. The high half of the pair is the register whose address is one more than the address specified.

#### EXTENDED OPERATION REGISTER PAIRS

| A-BUS        | B-BUS      | C-BUS     | BINARY ADDRESC |

|--------------|------------|-----------|----------------|

| F1, F0       | F1, F0     | F1, F0    | 0000           |

| F2, F1       | F2, F1     | F2, F1    | 0001           |

| F3, F2       | F3, F2     | F3, F2    | 0010           |

| F4, F3       | F4, F3     | F4, F3    | 0011           |

| F5. F4       | F5, F4     | F5, F4    | 0100           |

| F6. F5       | F6, F5     | F6, F5    | 0101           |

| F7. F6       | F7, F6     | F7, F6    | 0110.          |

| CL, F7       | PL, F7     | PL, F7    | 0111           |

| CH, CL       | PH, PL     | PH, PL    | 1000           |

| CL, CH       | CL, PH     | illegal   | 1001           |

|              | CH, CL     | illegal   | 1010           |

| CH, CL       | SL, CH     | illegal   | 1011           |

| CL, CH       | SH, SL     | SH, SL    | 1100           |

| CH, CL       | <b>1</b> - | •         | 1101           |

| Durmy, CH    | K, SH      | K, SH     | 1110           |

| Dummy, Dummy | Dummy, K   | Dummy, K  | 4              |

| FO, Dummy    | FO, Dummy  | FO, Dummy | 1111           |

#### NOTE:

- 1. On extended operations A-BUS specification of PC incrementing or decrementing is disabled.

- 2. On an extended operation, if write is specified the value written is the high order result.

#### 4. CaCa - Set Carry Field

All register instructions except !! and SHFT can set the carry bit (SHO) to 0 or 1 at the beginning of the instruction execution. The set carry options are:

CaCa = 00 -- Do not set carry CaCa = 10 -- Set carry to 0 CaCa = 11 -- Set carry to 1

(NOTE: 01 reserved for SHFT)

#### 5. Ha, Hb - High/Low 4-Bit Selection

The Mask Branch, M, and MI instructions operate on either the high or low 4 bits of the A and/or B registers. The Ha bit specifies the high or low 4 bits of the A-Bus register; the Hb bit specifies the high or low 4 bits of the B-Bus register.

Ha = 0 Low 4-bits of A-Bus register

Ha = 1 High 4-bits of A-Bus register

Hb = 0 Low 4-bits of B-Bus register

Hb = 1 High 4-bits of B-Bus register

#### 6. II...I — Immediate Operand

For Immediate Register Instructions, the actual 8 bits contained in the Immediate Operand Field (IIII) are gated directly to the A-Bus. For the LPI (load PC's immediate) instruction, the PC's are set equal to the 16-bit immediate field.

#### 7. RR...R — Branch Addresses

The R field is the branch address specified by the micro-instruction. The 10-bit address branches are treated as in-page branching for theoretical pages of 1024 steps. (i.e., the upper 6 bits of the branch address are the same as that of the current instruction).

#### 8. MARM — Branch Mask

For the mask branch instructions, these 4 bits in the instruction have the following meaning:

Branch True, Branch False -- 12121 specifies what bits in the specified B-bus register are to be tested.

M = 1, test the corresponding bit; if

M = 0, do not test the corresponding

bit.

Branch Equal, Branch Not Equal -- ITTM is the 4-bit pattern to which the high or low 4 bits of the specified B-Bus register is to be compared.

## 9. AxAxAxAx - Auxiliary Register Field

This field specifies which of the 32 Auxiliary registers is to be used in the Auxiliary -- PC Mini-Instruction. Three mini-instructions (TPA, TAP, and XPA) transfer 16 bits between the program counter (PH, PL) and the specified Aux register (0 - 1F).

# 10. ± In In — Increment/Decrement Field

The + In In field specifies whether or not the 16-bit value in the PC's is to be incremented or decremented (by 1, 2, or 3) as it is being transferred to the Auxiliary register (TPA, XPA) or subroutine return stack (TPS).

| + In In | = | 000 | PC's     | <b>→</b> | Aux | or | stack |

|---------|---|-----|----------|----------|-----|----|-------|

| + In In | = | 001 | PC's + 1 | +        | Aux | or | stack |

| + In In | = | 010 | PC's + 2 | +        | Aux | or | stack |

| + In In | = | 011 | PC's + 3 | +        | Aux | or | stack |

| + In In | = | 100 | PC's     |          |     |    |       |

| + In In | = | 101 | PC's - 1 |          |     |    |       |

| + In In | = | 110 | PC's - 2 | +        | Aux | OT | stack |

| + In In | - | 111 | PC's - 3 | +        | Aux | OT | stack |

## E. <u>Timing Sequence</u>

The following timing sequence of events takes place for the 2600 micro-instructions:

## Register and Mini-Instruction Timing Sequence

- 1. For LPI instructions, the PC registers are loaded with the specified value.

- 2. If DD bits specify a Read or Write, the contents of the Data Memory Program Counter (PH, PL) are transferred to the memory control logic to select the address.

- 3. The <u>initial</u> contents of the registers selected by the A-Bus (or Immediate Operand), and the B-Bus fields, and carry bit are gated to the Buses and into the ALU.

- 4. If set carry is specified (CaCa field of Register Instructions), the carry (SH<sub>O</sub>) is set as specified.

- 5. The arithmetic or logical operation is performed in the ALU.

- 6. The results of the arithmetic or logical operation in the ALU is stored in the register specified by the C-Bus field.

- 7. If PC, stack, and Auxiliary Register transfers or exchanges are specified by the instruction, they are done. (TPA, TAP, XPA, TPS, TSP).

- 8. If Auxiliary register  $\pm 1$ ,  $\pm 2$ , or  $\pm 3$  incrementing or decrementing is specified, (e.g., TP+1, XPA-3, XPA+2)  $\pm 1$ ,  $\pm 2$ , or  $\pm 3$  is added with 16-bit of data received by the Auxiliary PC register.

- 9. If a Read or Write is specified, data is read into CH, CL or written from C-Bus (result of ALU operation) to memory.

- 10. If PC incrementing or decrementing is specified by the A-field, PC's are incremented or decremented by 1.

- 11. The Instruction Program Counter (IC's) is incremented by 1.

## Branch Instruction Timing S' quence

- 1. For Conditional Branches, the test is made to branch or not branch based on the contents of the B-Bus Register.

- 2. If the test is valid, the branch is made by replacing the low order 10 or full 16-bits of the IC registers with the R instruction operands.

- 3. If the test is not valid, the IC counters are incremented by 1 to get the next instruction.

- (Note For Subroutine Branches and Subroutine Returns, the address saved in the subroutine stack is the current instruction address + 1. The stack is circular.

- 4. If PC incrementing or decrementing is specified by the A-field, PC's are incremented or decremented by 1 after the branch test is performed. The incrementing will occur whether the test is true or false.

#### F. 2600 Trap Locations

16 control memory locations are reserved as traps (address 8000 through 800F). When a trap condition occurs, normal processing is immediately terminated and an automatic branch is made to the appropriate trap location. At the trap location is a branch instruction which transfers control to the specified microcode routine so that appropriate action can be taken. Presently, the following trap locations are defined:

8000 - PECM (parity error in control memory)

8001 - RESET

8002 - PEDM (parity error in data memory)

8003 - POR (power on - MASTER INITIALIZE)

#### G. Memory Parity

The 2600 uses odd parity on both control memory and data memory.

#### 1. Control Memory Parity

The high order bit of each instruction in control memory is the parity bit; parity is odd. The parity bit of each instruction is generated by software; the SR, WCM instruction writes the 24 bits in the  $\overline{K}$ , PH, and PL (parity and instruction). The WCM instruction does not generate parity.

Instruction parity is checked when fetching an instruction for execution. If there is a parity error, the system will set parity error status bit  $(SH_6) = 1$  and trap to location  $8000_{16}$  in control memory. The address +1 of the instruction with bad parity is pushed into the subroutine return stack.

If the instruction (data) read by a SR, RCM instruction has bad parity, the parity error status bit (SH<sub>6</sub>) is set to 1. No trap is made and the address of the instruction with bad parity is not saved in the stack.

#### 2. Data Memory Parity

Odd parity is generated and written by the hardware at the time of a write to data memory.

On a read from data memory, parity is checked on the 16 bits read. If there is a parity error, the parity error status bits  $(SH_6)$  is set to 1. If the parity trap control status bit  $(SH_7)$  is set to 0, the system will trap to location  $8002_{16}$  in control memory. If  $SH_7 = 1$ , the trap is inhibited. The address of the data with bad parity is not saved in the stack regardless of whether the system traps or not. Also, the PC's may not be the address of the data with bad parity (e.g., XPA, R).

#### 3. Parity Status Bits

- SH<sub>6</sub> parity error. Set to 1 whenever bad parity is detected when fetching instructions or reading data.

- SH<sub>7</sub> parity trap control. (Data Memory)

- 0 = parity error trap for data memory enabled.

- parity error trap for data memory inhibited.

# APPENDIX A

DETAILED DESCRIPTION

OF THE

INSTRUCTION SET

|         | T-T- |       | 1  |     | i  |      | 1 1        |

|---------|------|-------|----|-----|----|------|------------|

| 0,0,0,0 | x 0  | Ca Ca | DD | CCC | CA | AAAA | B, B, B, B |

If X = 0, the OR of the registers specified by the A and B fields is formed and the result is stored in the register specified by the C field. If X = 1, the OR of the register pair specified by the A field is OR'ed with the register pair specified by the B field and the result is stored in the register pair specified by the C field.

Register use in the A, B, and C fields:

Carry (Sh) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

DD = 00: no read or write

D D = 01: read

D D = 10: Write 1

D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

| A  |    |   | - | Dummy |   |    | В | +        | С | [Memory] |

|----|----|---|---|-------|---|----|---|----------|---|----------|

| В  |    |   | - | Dummy | • |    | A | <b>→</b> | C | [Memory] |

| C  |    |   | = | Dummy | A | OT | В | +        |   | [Memory] |

| A, | В  |   | = | Dumny |   |    | 0 | +        | C | [Memory] |

| A, |    |   | - | Dummy |   |    | В | +        |   | [Memory] |

| В, |    |   | - | Dummy |   |    | A | +        |   | [Memory] |

| •  | В, | C | = | Dummy |   |    | 0 | +        |   | [Memory] |

|           | F - T               | 1     |     | 1     |     |    |     | Í |          | l |

|-----------|---------------------|-------|-----|-------|-----|----|-----|---|----------|---|

| 0 0 0 0 1 | $\mathbf{x} \mid 0$ | Ca Ca | D D | C,C   | C C | AA | A A | B | ВВВ      | В |

|           | 1 1                 | 1     |     | 1 1 1 |     |    |     |   | <u>'</u> |   |

If X = 0, the exclusive OR of the registers specified by the A and B fields is formed. The results are stored in the register specified by the C field. If X = 1, the register pair specified by the A field is exclusive OR'ed with the register pair specified in the B field and the result is stored in the register pair specified by the C field.

Register use in the A, B, and C fields:

Carry (SH<sub>0</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

D D = 00: no read or write

D D = 01: read

D D = 10: Write 1

D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction..

The A field can specify that PC's be incremented or decremented at the end of the instruction.

| A       | = Dummy | В        | + | C | [Memory] |

|---------|---------|----------|---|---|----------|

| В       | = Dummy | A        | + | C | [Memory] |

| Ċ       | = Dummy | A 🕀 B    | + |   | [Memory] |

| A, B    | = Dummy | 0        | + | C | [Memory] |

| A, C    | = Dummy | <b>B</b> | + |   | [Memory] |

| В, С    | = Dummy | A        | + |   | [Memory] |

| A, B, C | = Dummy | 0        | + |   | [Memory] |

| 0 0   |     | • | _ | v | Λ . | ~~ | C- | ח | n | ~ | ~   | ^   | ~   | l a | A | A |   | 22  | 10 | 20 | 10    |

|-------|-----|---|---|---|-----|----|----|---|---|---|-----|-----|-----|-----|---|---|---|-----|----|----|-------|

| 10 U  | , , |   | v |   | וטו |    | Ca | ע | ע |   | C   | · · | - U |     | ^ | • |   | ש   | Ð  | D. | . D ∖ |

| 1 1 1 |     |   |   |   |     | 1  |    |   | 1 |   | , , |     |     | ľ   |   |   | • | 1 1 |    |    |       |

If X = 0, the AND of the registers specified by the A and B fields is formed. The result is stored in the register specified by the C field. If X = 1, the register pair specified in the A field is AND'ed with the register pair specified in the B field and the result is stored in the register pair specified in the C field.

Register use in the A, B, and C fields:

```

A: F0 - F7, CL-, CH-, CL, CH, CL+, CH+, +, -

B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy

(if X = 0) C: F0 - F7, PL, PH, , SL, SH, K, dummy

(if X = 1) C: F0 - F7, PL, , SL, SH, K, dummy

```

Carry (SH<sub>1</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

```

D D = 00: no read or write

D D = 01: read

D D = 10: Write 1

D D = 11: Write 2

```

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

```

C

[Memory]

Dummy

C

0 →

[Memory]

В

- Durmy

C

Dummy

A . B

[Memory]

0

Dummy

[Memory]

A, B

0 +

A, C

Dummy

[Memory]

0 →

[Memory]

B, C

- Dumny

0 +

[Memory]

A, B, C

= Dummy

```

|           |                     | 7      |      | 1    |         |               |            |

|-----------|---------------------|--------|------|------|---------|---------------|------------|

| 0,0,0,1,1 | $\mathbf{x} \mid 0$ | Ca, Ca | D, D | C,C, | C, C  A | A , A , A , A | B, B, B, B |

If X=0, the 8-bit register specified by the B field is complemented and added, with carry, to the 8-bit register specified by the A field. The final result is stored in the register specified by the C field, and  $SH_0$  will receive the resultant carry. If X=1, the register pair specified by the B field is complemented and added, with carry, to the register pair specified by the A field. The result is stored in the register pair specified by the C field, and  $SH_0$  will receive the resultant carry.

Register use in the A, B, and C fields:

(if X = 1) C : F0 - F7, PL, , SL, SH, K, dumm

Carry (SH<sub>0</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction

CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If SH is specified in the C-field, the results are indeterminate.

```

- Dumny

- B - 1 + Carry

Carry

[Memory]

A

= Dummy A

- 1 + Carry

[Memory]

В

Carry

- 1 + Carry

[Memory]

Carry

A, B

Durmy

= Dummy A - B - 1 + Carry

[Memory]

Carry

-B-1+Carry

[Memory]

A, C

- Dummy

Carry

- Dummy A

- 1 + Carry

B, C

Carry

[Memory]

Dumma

- 1 + Carry

Carry

[Memory]

A, B, C

```

# 0,0,1,0,0 X 0 Ca, Ca D. D C. C, C. C A. A, A, A B, B. B. B

If X=0, the 8-bit registers specified by the A and B fields are the last resultant carry (SH<sub>0</sub>) are added together in decimal. The final sum is stored in the register specified by the C field and SH<sub>0</sub> will be set equal to the resultant carry. The addends must be decimal (0-9) or the sum will be indeterminent. If X=1, the register pair specified by the A field and the last resultant carry are added in decimal to the register pair specified by the B field; the result is stored in the register pair specified by the C field and SH<sub>0</sub> receives the resultant carry.

Register use in the A, B, and C fields:

Carry (SH<sub>0</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If A or B field registers contain non-decimal data, or if SH is specified in the C-field, the results are indeterminate.

# 0 0 1 0 1 X 0 Ca, Ca D, D C, C, C, C A, A, A, A B, B, B, B

If X=0, the 8-bit register specified by the B field plus the last resultant carry (SH<sub>0</sub>) is subtracted from the 8-bit register specified in the A field in decimal and the new carry is generated. (That is, the 9's complement of [the B register] and the carry are added to the A register and the new carry is generated). The result is stored in the C register.

Similarly, if X = 1, the register pair specified by the B field plus the last resultant carry is subtracted from the register pair specified by the A field in decimal and the new carry is generated. The result is stored in the register pair specified by the C field.

Register use in the A, B, and C fields:

A: F0 - F7, CL-, CH-, CL, CH, CL+, CH+, +, -B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy

(if X = 0) C: F0 - F7, PL, PH, , SL, SH, K, dummy

(if X = 1) C: FO - F7, PL, , SL, SH, K, dummy

Carry (SH<sub>0</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

D D = 00: no read or write

D D = 01: read

DD = 10: Write 1

D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

The A and B field registers must contain decimal data (0 - 9) or the results are indeterminate.

If SH is specified in the C field, the results are indeterminate.

| A       | <ul><li>Dummy</li></ul> | - B - Carry   | <b>+</b> ( | Carry | [Memory] |

|---------|-------------------------|---------------|------------|-------|----------|

| В       | - Dummy                 | A - Carry     | <b>+</b> ( | Carry | [Memory] |

| A, B    | = Dummy                 | - Carry       | <b>+</b> ( | Carry | [Memory] |

| C       | = Dummy                 | A - B - Carry | <b>→</b>   | Carry | [Memory] |

| A, C    | = Dummy                 | - B - Carry   | <b>+</b>   | Carry | [Memory] |

| B, C    | ■ Dummy                 | A - Carry     | <b>→</b>   | Carry | [Memory] |

| A. B. C | = Dummy                 | - Carry       | +          | Carry | [Memory] |

# 0 0 1 1 0 X 0 Ca Ca D D C C C C A A A A B B B B B

If X=0, the 8-bit registers specified by the A and B fields and the last resultant carry (SH 0) are added together in binary. The final sum is stored in the register specified by the C field, and SHO will receive the resultant carry. If X=1, the register pair specified by the A field is and the last resultant carry are added in binary to the register pair specified by the B field; the resultant is stored in the register pair specified by the C field, and SHO will receive the resultant carry.

Register use in the A, B, and C fields:

'(if X = 1) C : FO - F7, PL, , SL, SH, K, dummy

Carry (SH<sub>0</sub>) options: CaCa = 00, do not change carry

CaCa = 10, set carry to 0 at beginning of instruction CaCa = 11, set carry to 1 at beginning of instruction

Read/Write options:

p p = 00: no read or write

DD = 01: read

DD = 10: Write 1

D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If SH is specified in the C-field, the results are indeterminate.

0 0 1 1 1 X 0 Hb Ha D D C C C C A A A A B B B B

If X = 0, the low (or high) 4-bits of the register specified in the A field is multiplied in binary by the low (or high) 4-bits of the register specified in the B field; the product (8-bits) is stored in the register specified by the C field. If X = 1, the above operation is performed; the above operation is then repeated but on the registers whose addresses are one greater than those specified in the A, B, and C fields.

Selection of high/low 4-bits of A, B registers:

HbHa = 00, low 4-bits of A and low 4-bits of B

HbHa = 01, high 4-bits of A and low 4-bits of B

HbHa = 10, low 4-bits of A and high 4-bits of B

HbHa = 11, high 4-bits of A and high 4-bits of B

Register use in the A, B, and C fields:

A: F0 - F7, CL-, CH-, CL, CH, CL+, CH+, +, B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy

(if X = 0) C: F0 - F7, PL, PH, , SL, SH, K, dummy

(if X = 1) C: F0 - F7, PL, , SL, SH, K, dummy

Read/Write options:

D D = 00: no read or write D D = 01: read D D = 10: Write 1 D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If A and/or B and/or C are set to indicate the dummy register, the net result will be:

A Dummy C [Memory] 0 + C Dummy [Memory] В 0 + A, B Dummy [Memory] B Drimma [Memory] A, C 0 Dummy [Memory] B, C Dummy [Memory] Dummy [Memory] A, B, C

| - 1 |   |   |   |     |    |     |   |   |   |   |   |   |   |   |   |   |   |   |                                              |   |   |   |          |   |

|-----|---|---|---|-----|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|----------------------------------------------|---|---|---|----------|---|

| 1   | 0 | 0 | 0 | НЪ  | Ha | X   | 0 | 0 | 1 | ם | D | C | C | C | C | Α | A | A | A                                            | В | B | В | B 1      | ı |

| - 1 |   |   | , | i i |    | 1 1 | • |   |   | • | • | ( | 1 | 1 | • | ٠ |   | L | <u>.                                    </u> |   | L | 1 | <u> </u> | ı |

• • •

If X = 0, the SHFT instruction sets the low 4-bits of the register specified by the C field equal to the high (or low) 4-bits of the register specified by the A field, and sets the high 4-bits of the C register equal to the high (or low) 4-bits of the B register. If X = 1, the above operation is performed; the above operation is then repeated on the registers whose addresses are one more than those specified in the A, B, and C fields.

Selection of high/low 4-bits of A, B registers:

Hb Ha = 00, high 4-bits of C = low 4-bits of B low 4-bits of C = low 4-bits of A

Hb Ha = 01, high 4-bits of C = low 4-bits of B low 4-bits of C = high 4-bits of A

Hb Ha = 10, high 4-bits of C = high 4-bits of B low 4-bits of C = low 4-bits of A

Hb Ha = 11, high 4-bits of C = high 4-bits of B low 4-bits of C = high 4-bits of A

Register use in the A, B, and C fields:

A: F0 - F7, CL-, CH-, CL, CH, CL+, CH+, +, -B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy

(if X = 0) C: FO - F7, PL, PH, , SL, SH, K, dummy

(if X = 1) C: F0 - F7, PL, , SL, SH, K, dummy

Read/Write options:

D D = 00: no read or write

D D = 01: read

D D = 10: Write 1

D D = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the A or B fields, the previous contents of CH or CL will be used in the instruction.

The A field can specify that PC's be incremented or decremented at the end of the instruction.

If A and/or B and/or C are set to indicate the dummy register, the net result will be:

A = Dummy B 0 C [Memory] 0 A [Memory] В Dummy C Dummy BA [Memory]  $0 \rightarrow C$ A, B [Memory] Dummy B 0 + A, C [Memory] Dummy 0 A [Memory] B, C Dummy 0 A, B, C Dummy [Memory]

# 0,1,0,0,0 I,I,I,I D,D C,C,C,C I,I,I,I B,B,B,B

The OR of the register specified by the B field and the 8-bits in the I field are formed. The result is stored in the register specified by the C field.

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read

DD = 10: Write 1

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If B and/or C are set to indicate the dummy register, the net result is:

#### XORI - EXCLUSIVE OR IMMEDIATE

| 0,1,0,0,1   I, I, I   D, D   C, C, C, C   I, I, I, I   B, B, B, B |   |     |   |   |     |   |   |     |     |     |   |   |                                               |   |    |   |   |        |    |   |    |    |

|-------------------------------------------------------------------|---|-----|---|---|-----|---|---|-----|-----|-----|---|---|-----------------------------------------------|---|----|---|---|--------|----|---|----|----|

| I۸                                                                | 3 | n   | n | 1 | T   | T | Т | . Т | מ ו | ת   | C | С | C                                             | С | İΤ | T | T | T      | В. | В | В. | B  |

| 10                                                                |   | , • | 1 |   | 1 - |   | _ | i 👛 | 12  | 1 - |   | 1 | <u>,                                     </u> |   |    |   |   | نــــا |    |   |    | لت |

The exclusive OR of the register specified by the B field and the 8-bits in the I field are formed. The result is stored in the register specified by the C field.

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read

DD = 10: Write 1

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If the B and/or C are set to indicate the dummy register, the net result is:

B = Dummy

$$0 \rightarrow C$$

[Memory]

C = Dummy  $B \oplus I \rightarrow$  [Memory]

B, C = Dummy 0 + [Memory]

|          |   |     |   |          | _   |     |     |   |     |   | 1           |     |   |       |                |   |   |     | i   |   |      | 1   |

|----------|---|-----|---|----------|-----|-----|-----|---|-----|---|-------------|-----|---|-------|----------------|---|---|-----|-----|---|------|-----|

| 0        | _ | _   | _ | _        | 1 _ | _   | _   | _ | 1 _ | _ | 1 -         | _   | _ | _     |                | _ | _ | -   |     | - | ~    |     |

| ın       | 7 | n   | 1 | Λ        | ( T | т   | т   | T | ı n | n | ľ           | r   | r | - ( ) | 11             |   |   | - 1 | ( H | к | . 15 | M i |

| ı u      | 1 | . u |   | . U      |     |     | -   |   |     | ע |             | . • | • | . •   | , <del>-</del> |   |   | -   | , , |   |      |     |

| , -      |   |     |   |          | . – | . – | . – |   | -   |   | 1           | 1   | • | ì     |                |   | , | •   | ŧ   | 1 | 1    | , , |

| <u> </u> | 2 | i   |   | <u> </u> | 1   |     |     | 1 |     |   | <del></del> |     |   |       |                |   |   |     |     |   |      |     |

The AND of the register specified by the B field and the 8-bits in the I field are formed. The result is stored in the register specified by the C field.

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read

DD = 10: Write 1

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If B and C are set to indicate the dummy register, the net result is:

B = Dummy 0 + C [Memory]

C = Dummy B . I + [Memory]

B . C = Dummy 0 + [Memory]

#### AI -- BINARY ADD INTEDIATE

| 0,1,0,1,1,I,I,D,D,C,C,C,I,I,I,B,B,B,B | ,             |       |       |       |                  |       |       |         |         | 1     |      |      |

|---------------------------------------|---------------|-------|-------|-------|------------------|-------|-------|---------|---------|-------|------|------|

|                                       |               |       |       | -     | <del>-</del>   - | 2 0   |       |         | 7 7     | T D   | מ מ  | 10 G |

|                                       | 10.10.        | 1 1 1 | 1 . 1 |       | עוד              | שוע ע | U , U | . U i L | _ I . I | T   D | ם, ע | ום   |

|                                       | 1 - 1 - 1 - 1 |       | - 1 - | 1 - 1 | - 1 -            |       | ( 1   | 1 1     | , ,     | 1     |      | - 1  |

The 8-bit register specified by the B field and the 8-bits in the I field are added together in binary. The final sum is stored in the register specified by the C field.

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read

DD = 10: Write 1

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If B and/or C are set to indicate the dummy register, the net result is:

DACI - DECIMAL ADD INMEDIATE WI'LL CARRY

| 1 |     |         |     |   |    |     | 1 |     | : |     |       |   |   |     |     |   |   |   |     |   |

|---|-----|---------|-----|---|----|-----|---|-----|---|-----|-------|---|---|-----|-----|---|---|---|-----|---|

| 0 | . 1 | , 1 , 0 | 0,0 | I | I, | I,I | D | , D | С | , C | , C , | C | I | , I | , I | I | В | В | , В | В |

The 8-bit register specified by the B field and the 8-bits in the I field and the last resultant carry ( $SH_0$ ) are added together in decimal. The final sum is stored in the register specified by the C field. The resultant carry is stored in  $SH_0$ .

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read

DD = 10: Write 1

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If SH is specified in the C field, the results are indeterminate. The addends must be decimal (0 - 9) or the results are indeterminate.

If B and/or C are set to indicate the dummy register, the net result is:

B = Dummy I + Carry  $\rightarrow$  C Carry [Memory] C = Dummy B + I + Carry  $\rightarrow$  Carry [Memory] B, C = Dummy I + Carry  $\rightarrow$  Carry [Memory] DSCI -- DECIMAL SUBTRACT IMMEDIATE WITH CARRY

# 0,1,1,0,1 | I,I,I,I | D,D | C,C,C,C | I,I,I,I | B,B,B,B

The 8-bit register specified by the B field plus the last resultant carry ( $SH_O$ ) is subtracted in decimal from the 8-bits in the I field and the new carry is generated. (That is, the 9's complement of [the B register] and the carry are added to the immediate field and the new carry is generated). The result is stored in the register specified by the C field.

Register use in B and C fields:

B: F0 - F7, PL, PH, CL, CH, SL, SH, K, dummy C: F0 - F7, PL, PH, SL, SH, K, dummy

Read/Write options:

DD = 00: no read or write

DD = 01: read DD = 10: Write 1 DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

The I and B fields must contain decimal data (0 - 9) or the results are indeterminate.

If SH is specified in the C field, the results are indeterminate.

If B or C specify the dummy register, the results will be:

B = Dummy I - Carry  $\rightarrow$  C [Memory] C = Dummy I - B - Carry  $\rightarrow$  [Memory] B, C = Dummy I - Carry  $\rightarrow$  [Memory]

```

0,1,1,1,0 | I,I,I,I | D,D | C,C,C,C | I,I,I,I | B,B,B,B

```

The 8-bit register specified by the B field and the 8-bits in the I field and the last resultant carry (SH<sub>0</sub>) are added together in binary. The final sum is stored in the register specified by the C field. The resultant carry is stored in SH<sub>0</sub>.

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read

DD = 10: Write I

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If SH is specified in the C field, the results are indeterminate.

If B and/or C are set to indicate the dummy register, the net result is:

The low (or high) 4-bits of the register specified by the B field is multiplied in binary by the 4-bit I field. The 8-bit result is stored in the register specified by the C field.

If Hb = 0, the low 4-bits of the B register are used. If Hb = 1, the high 4-bits are used:

Register use in B and C fields:

Read/Write options:

DD = 00: no read or write

DD = 01: read DD = 10: Write 1

DD = 11: Write 2

For instructions that modify the PC registers, the read and write address will be the initial contents of the PC registers. If CH or CL is specified in the B field, the previous contents of the CH or CL will be used in the instruction.

If B or C specify the dummy register, the results will be:

B = Dummy  $0 \rightarrow C$  [Memory] C = Dummy I . B  $\rightarrow$  [Memory]

B, C = Dummy  $0 \rightarrow [Memory]$

TAP - TRANSFER AUX TO PC's

|                 | 0   0                 | Ax Ax Ax Ax Ax B B B B  |

|-----------------|-----------------------|-------------------------|

| 1 0,0,0,1,0,1,1 | 11, - 10, 010, -, - 1 | ו ען ען אאן אאן אאן אאן |

|                 | <u> </u>              | <u> </u>                |

The contents of the auxiliary register specified by the Ax field is transferred to the PC registers.