IV.A.3M

# Customer Engineering Division

J. Carter Thompson 326 Ilimano St. Kailua, HI 96734

DIAGNOSTICS 3.34

ADDRESSES

34

cpu RCB L9

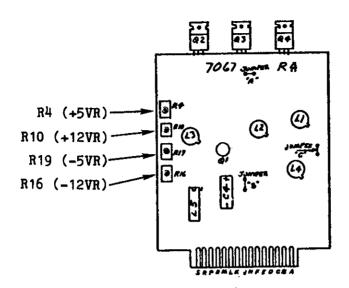

apu voltage adjust

7.5

2236DVOCTAGE ADJ.

7.7

CABLE 13

PCB UST 122

MELLORY 6.23 Power up DIAG

# Model 2200MVP

# Maintenance Manual J. Carton T

J. Carter Thompson 326 Himano St. Kailua, HI 96734

WANG

REORDER NUMBER 729-0584

J. Carter Thompson 326 Ilimano St. Kailua, HI 96734

# 2200 COMPUTER

Model: MVP

J. Carter Thompson 326 Ilimano St. Kailua, HJ 96734

#### COMPANY PROPRIETARY STATEMENT

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

Customer Engineering Product Maintenance Manual

#### PREFACE

This documentation package for the 2200MVP Computer consists of five separate publications including a basic Product Maintenance Manual (PMM), along with a Service Newsletter (SN) and three Product Service Notices (PSN's) inserted at the end of the PMM. The five publications are as follows:

- 1. PMM 729-0584: This version of the 2200MVP Computer PMM contains a new Illustrated Parts Breakdown (IPB) for the 2200MVP-A to replace the original Bill of Materials (BOM) in Appendix E

- 2. SN 729-0586: 2200VP/MVP Fan Replacement With Large I/O Controllers

- 3. PSN 729-0813: Model 2236MXD (WL# 177-3236-1) MUX/Controller

- 4. PSN 729-0814: Model 22C32 (WL# 212-3012) Triple Controller

- 5. PSN 729-1020: Installation of Option "C" Into 2200 MVP System

The scope of this documentation package reflects the type of maintenance philosophy selected for this product (swap unit, printed circuit assembly, chip level or any combination thereof). It's purpose is to provide the Wang-trained Customer Engineer (CE) with instructions to operate, troubleshoot and repair the 2200MVP Computer.

#### Second Edition (January 1984)

This edition of the 2200MVP PMM obsoletes document numbers 729-0584, 729-0586, 729-0813, 729-0814, and 729-1020. The material in this document may only be used for the purpose stated in the Preface. Updates and/or changes to this document will be published as PSN's or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

<sup>©</sup>Copyright WANG Labs., Inc. 1984

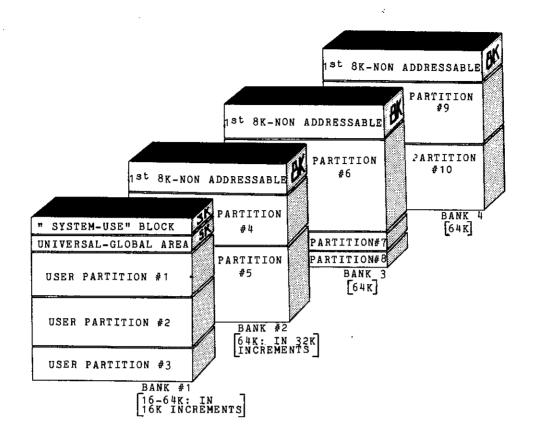

| 5.6     | ASSIGNMENT, ATTACHMENT, AND FOREGROUND/BACKGROUND PROCESSING5-9 5.6.1 ASSIGNMENT |

|---------|----------------------------------------------------------------------------------|

| 5.7     | "RELEASING" A TERMINAL5-11                                                       |

| 5.8     | "RELEASING" A PARTITION                                                          |

| 5.9     | "GLOBAL" PARTITIONS                                                              |

| 5.10    | "UNIVERSAL GLOBAL" PARTITIONS                                                    |

| 5.11    | USER PROGRAM EXECUTION                                                           |

| J • · · | 5.11.1 GENERAL                                                                   |

|         | 5.11.2 SUBROUTINES                                                               |

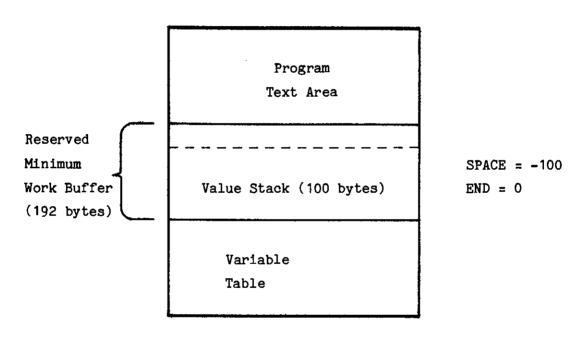

|         | 5.11.3 THE TEXT POINTER, THE POINTER TABLE, & INTERNAL STACKS                    |

| 5.12    | ALLOCATION AND HANDLING OF PERIPHERALS5-20                                       |

|         | 5.12.1 GENERAL5-20                                                               |

|         | 5.12.2 BACKGROUND PRINTING5-23                                                   |

|         |                                                                                  |

| SECTION |                                                                                  |

| 6.1     | GENERAL INTRODUCTION6-1                                                          |

| 6.2     | MICROCODE DIAGNOSTICS6-1                                                         |

|         | 6.2.1 LOADING SYSTEM FILES6-1                                                    |

|         | 6.2.1.1 BOOTSTRAP SPECIAL FUNCTION KEYS6-2                                       |

|         | 6.2.2 MICROCODE DIAGNOSTICS DESCRIPTION6-5                                       |

|         | 6.2.3 USER DIAGNOSTICS6-6                                                        |

|         | 6.2.4 FIELD SERVICE DIAGNOSTICS6-6                                               |

|         | 6.2.5 SPECIAL-FUNCTION KEY DEFINITIONS FOR BOOTSTRAP MENUS6-7                    |

| 6.3     | SYSTEM DIAGNOSTIC DISPLAYS6-9                                                    |

|         | 6.3.1 CPU DIAGNOSTIC6-9                                                          |

|         | 6.3.2 CONTROL MEMORY DIAGNOSTICS                                                 |

|         | 6.3.2.1 ADDRESSING                                                               |

|         | 6.3.2.2 MAT C&S                                                                  |

|         | 6.3.2.3 ROWPAT                                                                   |

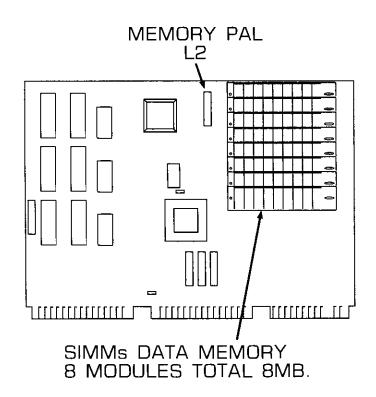

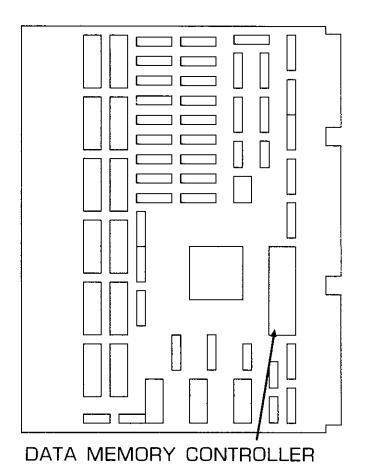

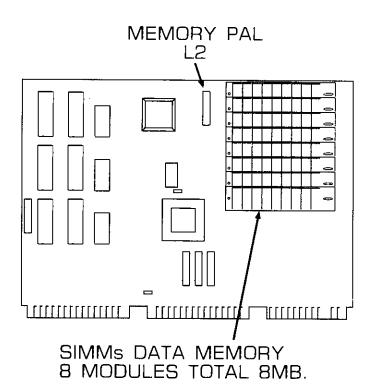

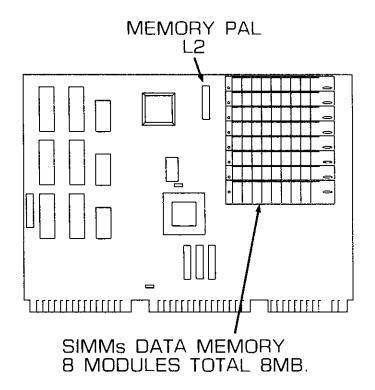

|         | 6.3.3 DATA MEMORY (USER MEMORY) DIAGNOSTICS                                      |

|         | 6.3.3.1 ADDRESSING                                                               |

|         | 6.3.3.3 ROWPAT                                                                   |

|         | 6.3.4 DIAGNOSTIC ERROR MESSAGE INFORMATION & IDENTIFICATION                      |

|         | OF FAULTY RAMS                                                                   |

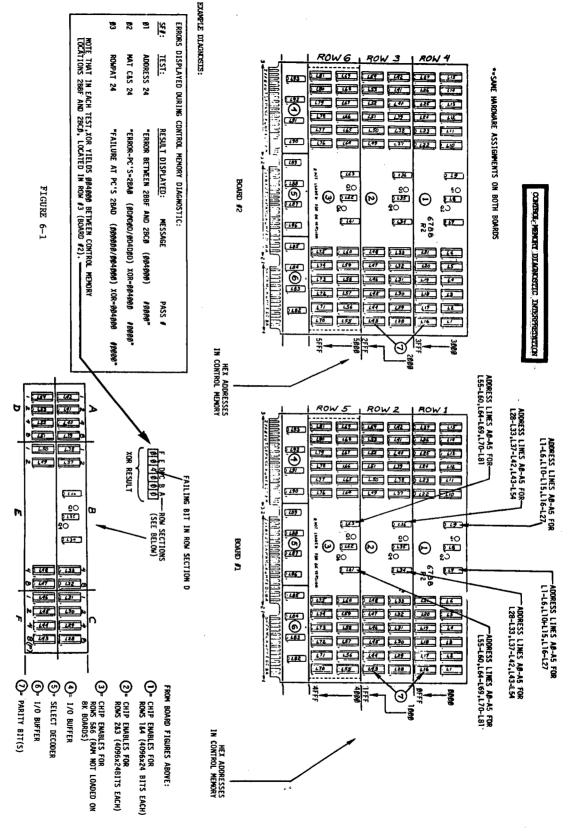

|         | 6.3.4.1 ERROR MESSAGE INFORMATION FOR CONTROL MEMORY TESTS                       |

|         | 6.3.4.2 ERROR MESSAGE INFORMATION FOR DATA MEMORY TESTS6-18                      |

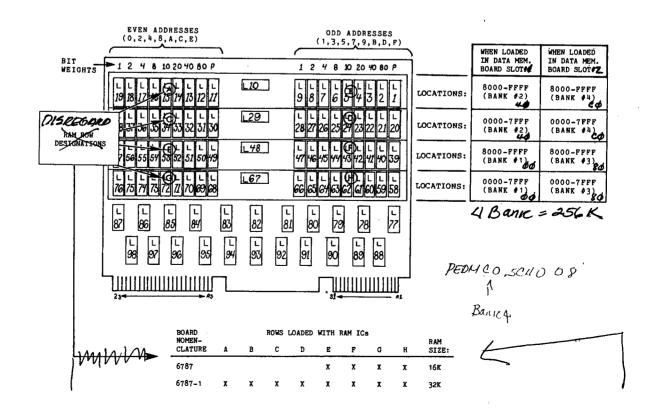

|         | 6.3.4.3 MEMORY DIAGNOSTIC INTERPRETATION USING THE                               |

|         | MEMORY ERROR CHIP IDENTIFICATION (MECI) PROGRAM6-2                               |

|         | 6.3.4.4 MEMORY DIAGNOSTIC INTERPRETATIONS BY DIAGRAM6-2                          |

|         | 6.3.5 REGISTER DIAGNOSTICS                                                       |

|         | 6.3.5.1 GENERAL PURPOSE REGISTERS                                                |

|         | 6.3.5.2 GENERAL REGISTERS ERROR DISPLAYS6-2                                      |

|         | 6.3.5.3 AUXILIARY/STACK                                                          |

|         | 6.3.5.4 AUXILIARY/STACK ERROR DISPLAYS6-2                                        |

|         | 6.3.5.5 STACK/AUXILIARY6-3                                                       |

|         | 6.3.5.6 STACK/AUXILIARY ERROR DISPLAYS6-3                                        |

| 6.4     | BASIC-2 LANGUAGE DIAGNOSTIC DISPLAYS                                             |

| 6.5     | 2236D AND 2236MXD DIAGNOSTIC PROCEDURES6-3                                       |

|         |                                                                                  |

| SECTION | 7 SYSTEM-LEVEL MAINTENANCE, ADJUSTMENTS, AND TROUBLESHOOTING                                                                                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1     | PREVENTIVE MAINTENANCE                                                                                                                                                                                                               |

| 7.2     | SYSTEM LEVEL PREVENTIVE MAINTENANCE                                                                                                                                                                                                  |

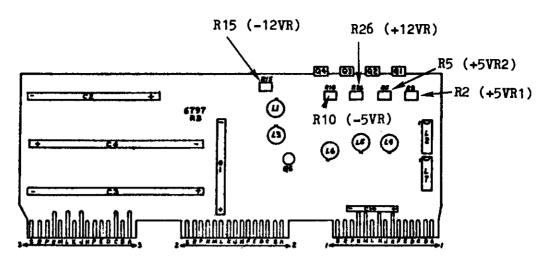

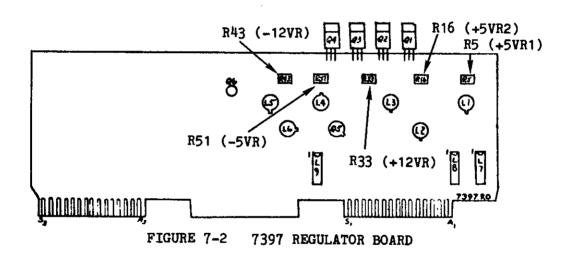

| 7.3     | ADJUSTMENTS                                                                                                                                                                                                                          |

| 7.4     | TROUBLESHOOTING THE 2200MVP                                                                                                                                                                                                          |

| SECTION | 8 UPGRADES/CONVERSIONS                                                                                                                                                                                                               |

| 8.2 MV  | TO MVP CONVERSIONS                                                                                                                                                                                                                   |

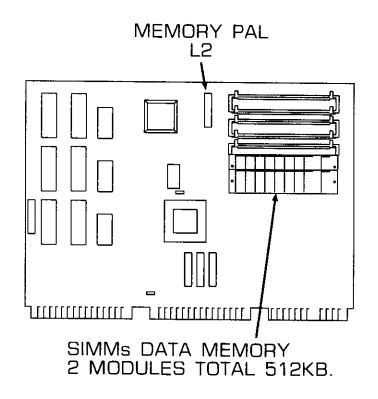

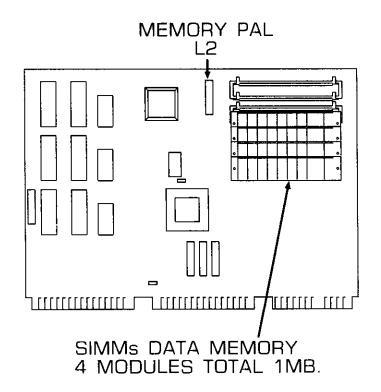

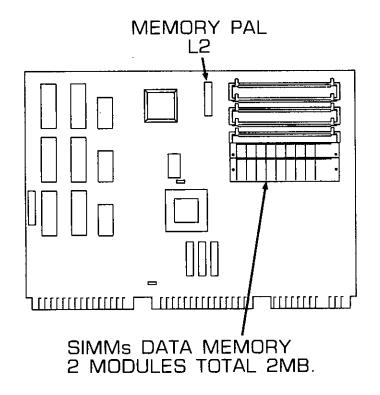

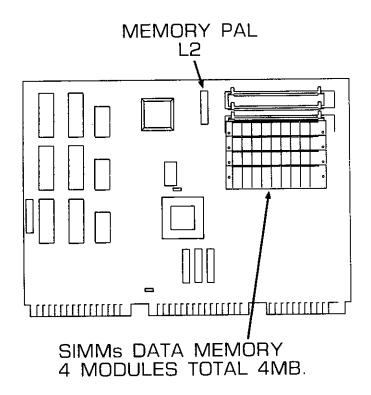

|         | 00MVP EXPANDED MEMORY       8-2         8.3.1 BOOTSTRAP PROMS       8-2         8.3.2 OPERATING SYSTEM       8-3         8.3.3 DIAGNOSTICS       8-3         8.3.4 HARDWARE CHANGE       8-3         8.3.5 CONVERSION KITS       8-6 |

|         | X A 2236D CHARACTER SET A-1                                                                                                                                                                                                          |

|         | X B 2200MVP ERROR CODES B-1                                                                                                                                                                                                          |

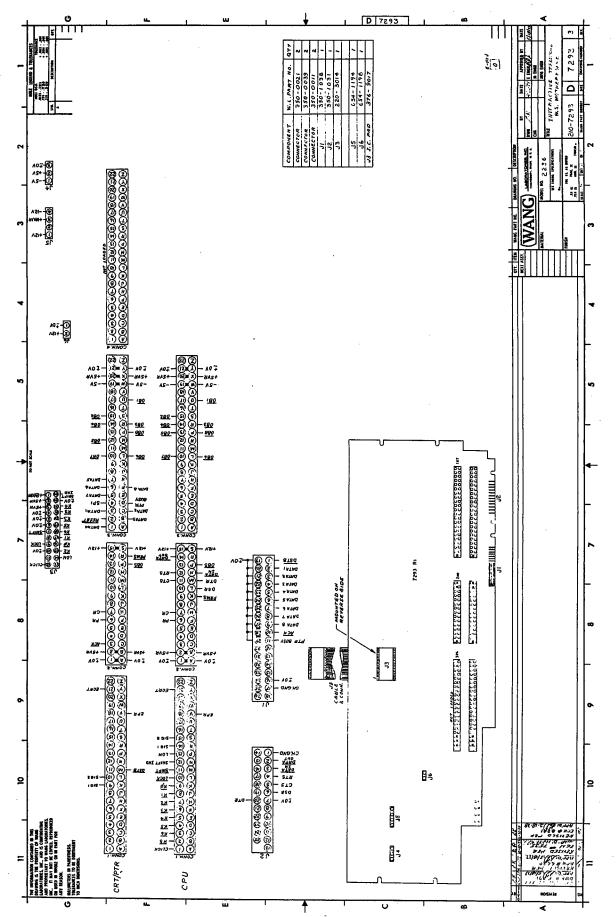

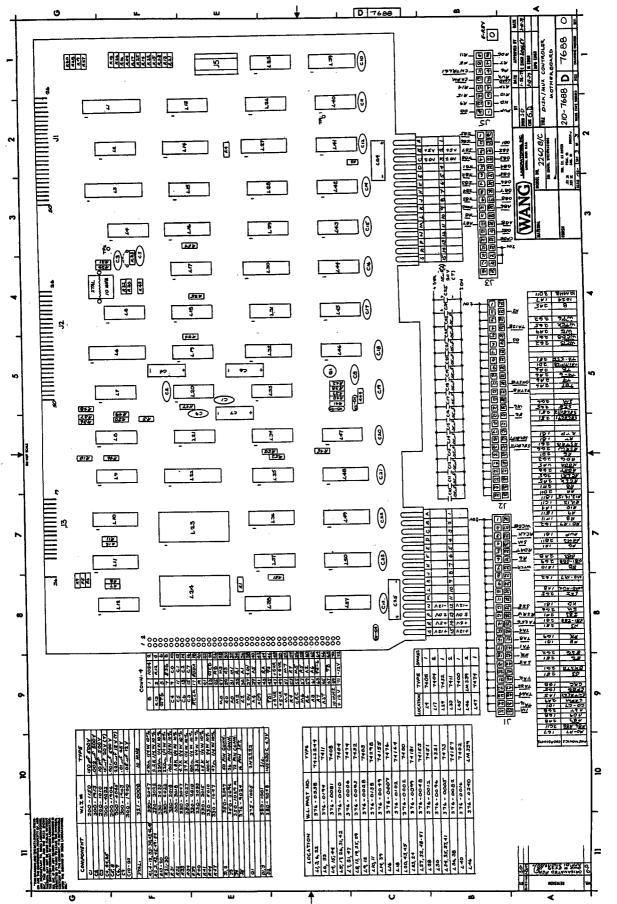

|         | X C CPU MOTHERBOARD (6798) MNEMONICS                                                                                                                                                                                                 |

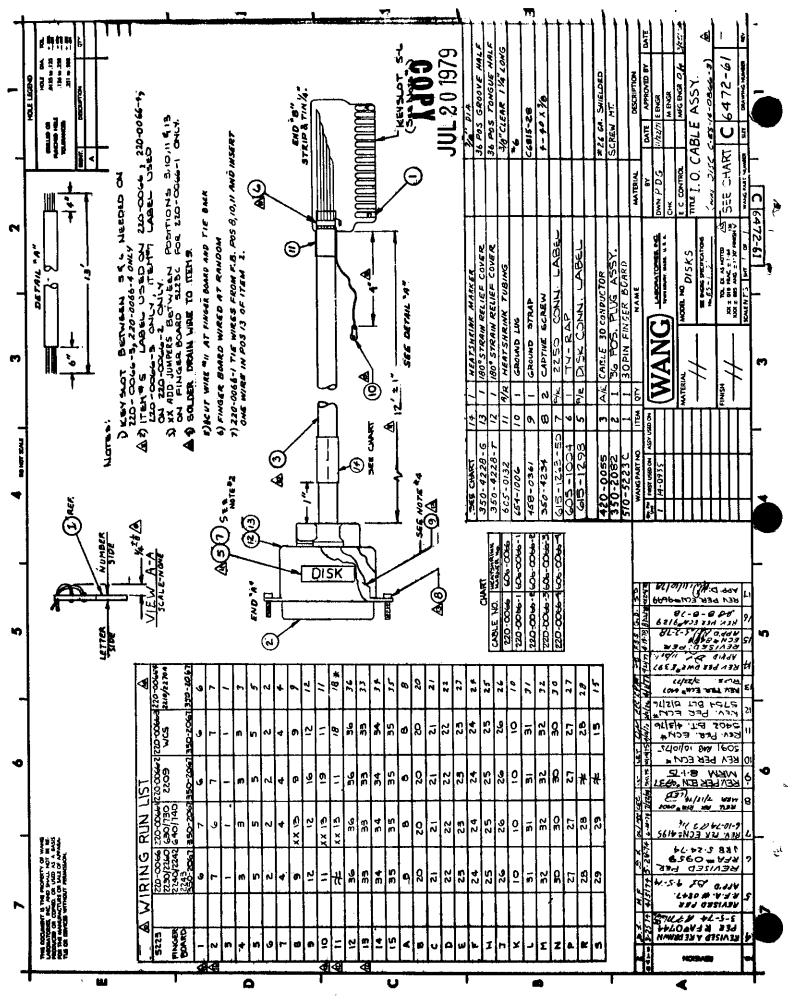

|         | XX D 2200MVP SIGNAL RUN LIST                                                                                                                                                                                                         |

|         | X E BILL OF MATERIALS E-1                                                                                                                                                                                                            |

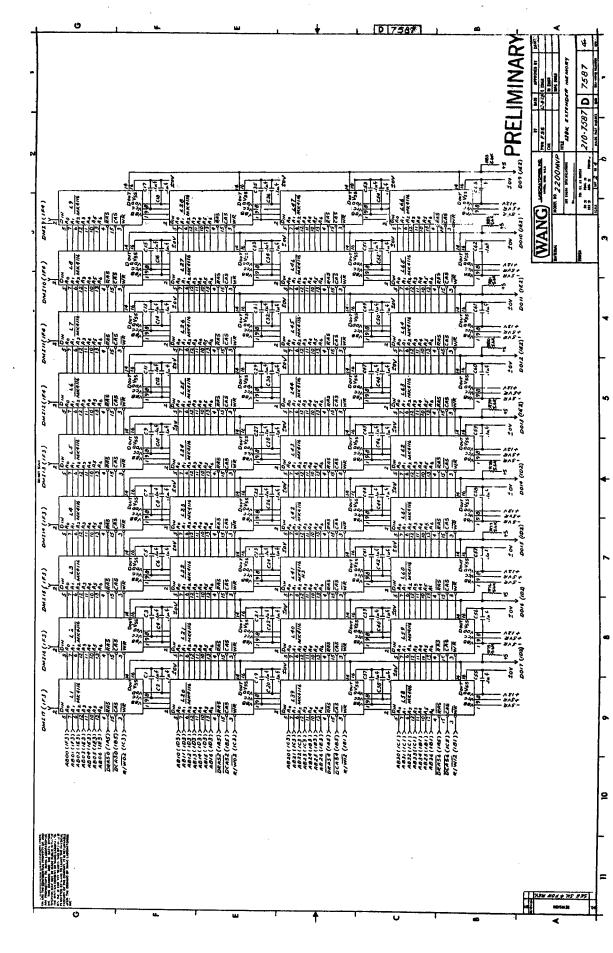

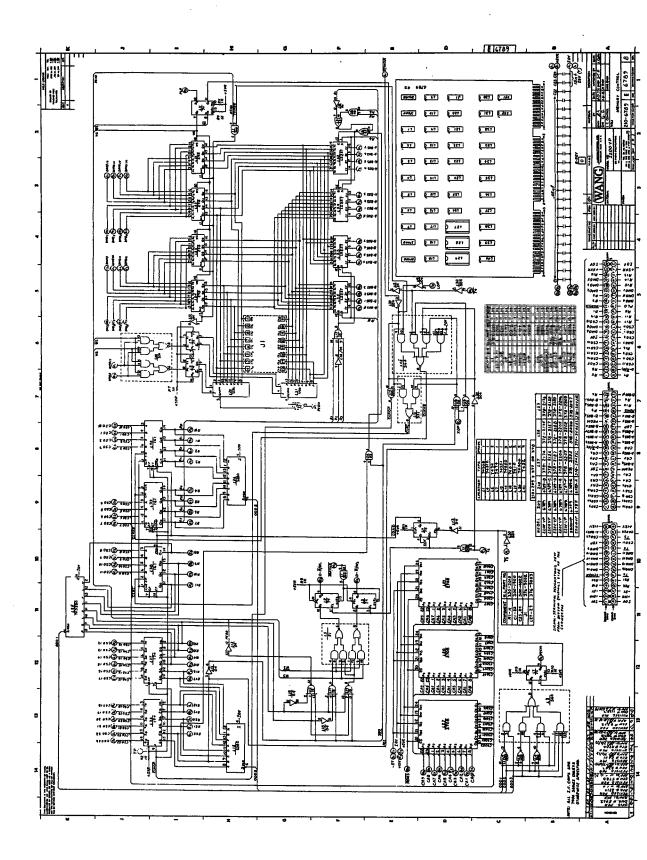

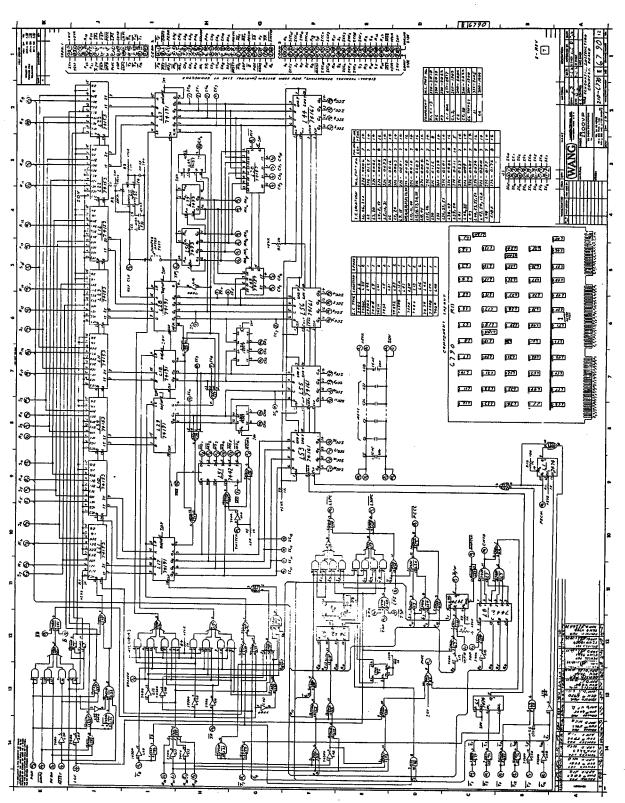

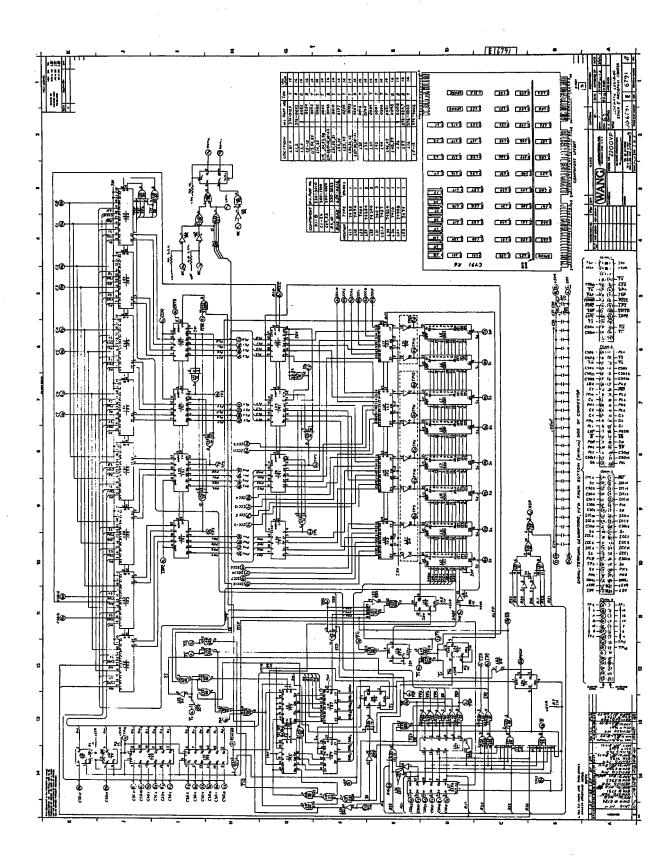

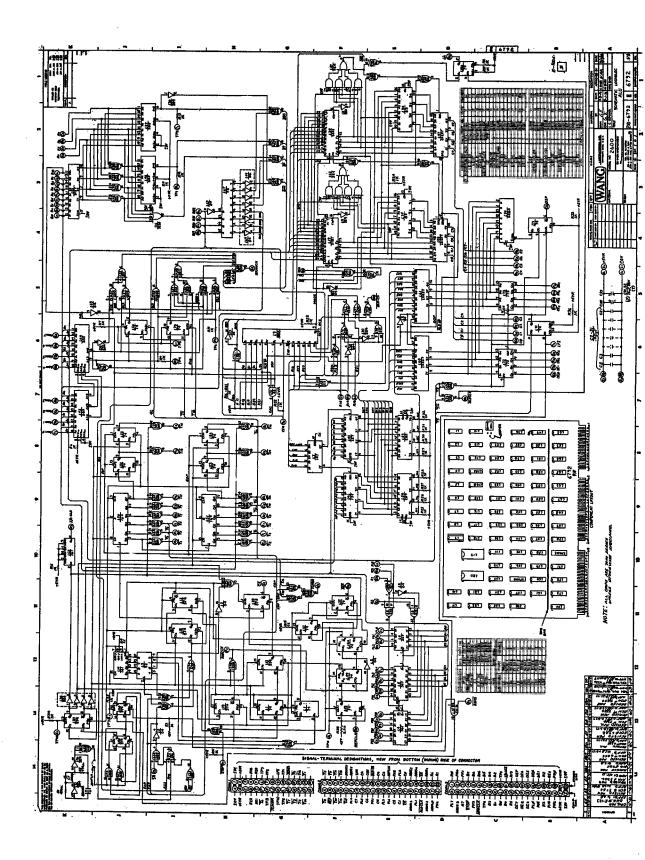

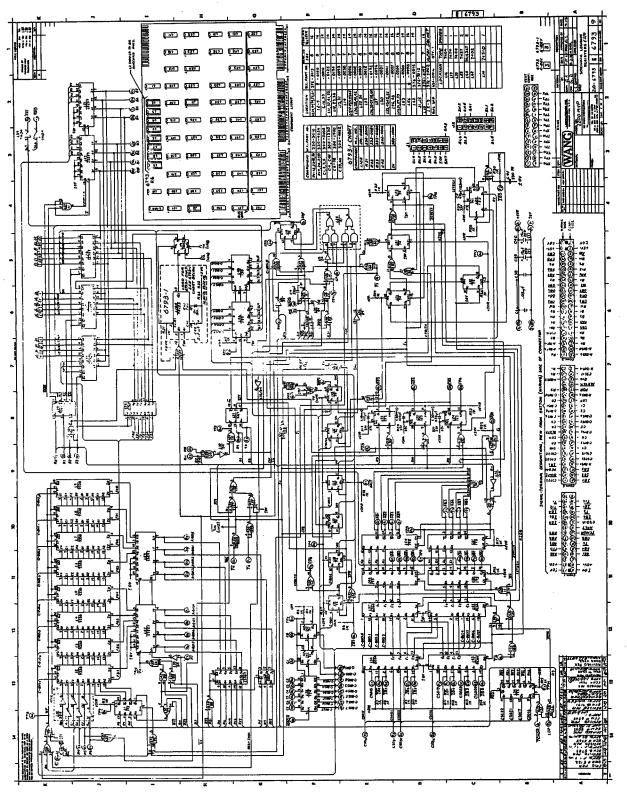

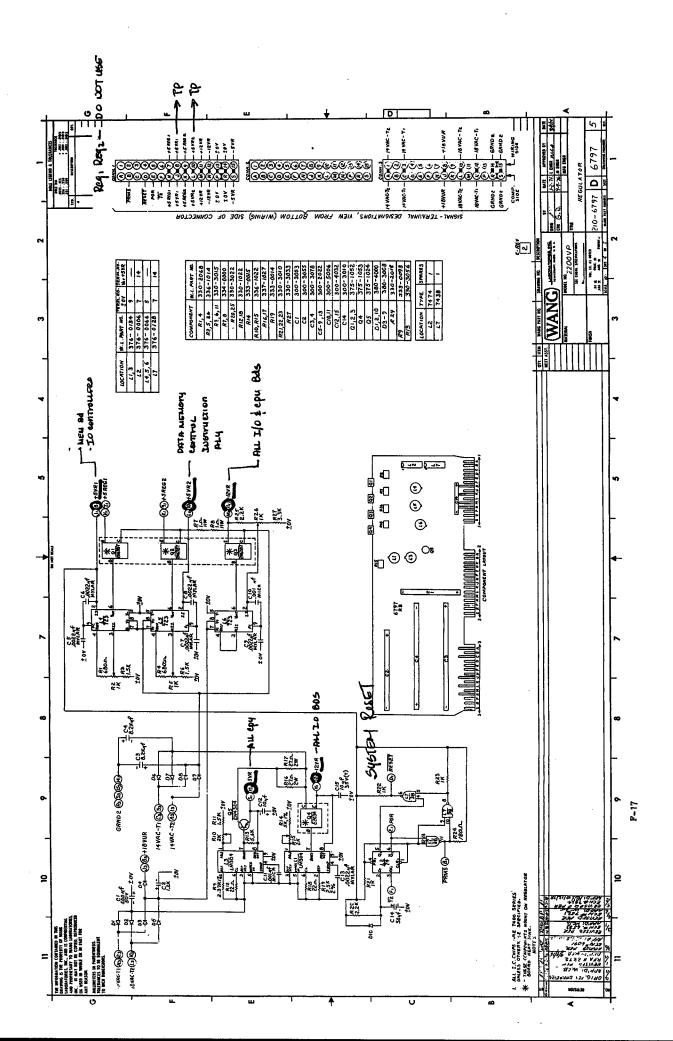

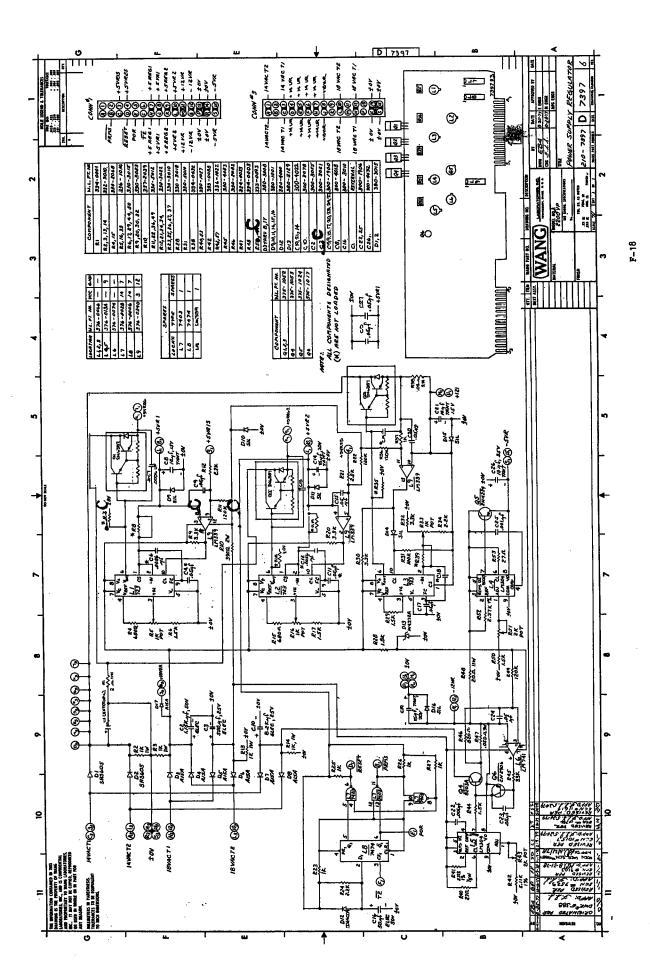

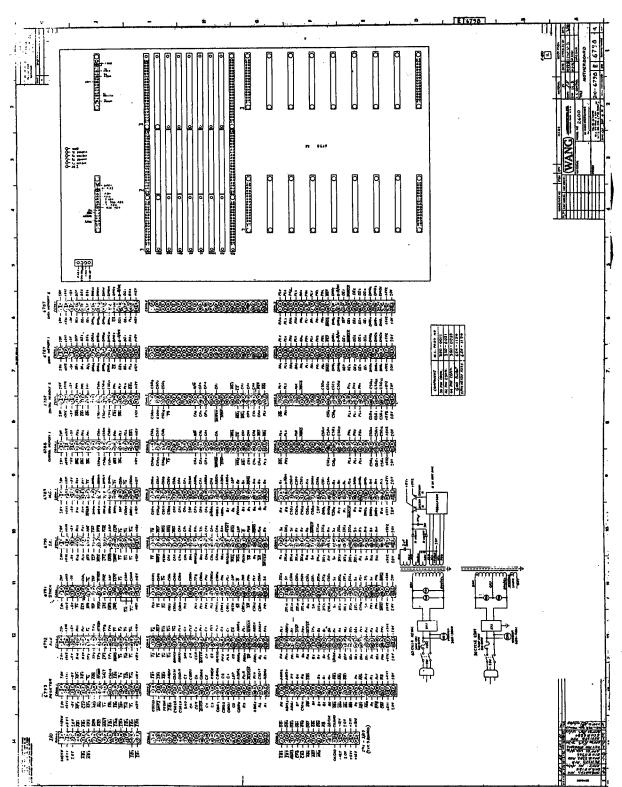

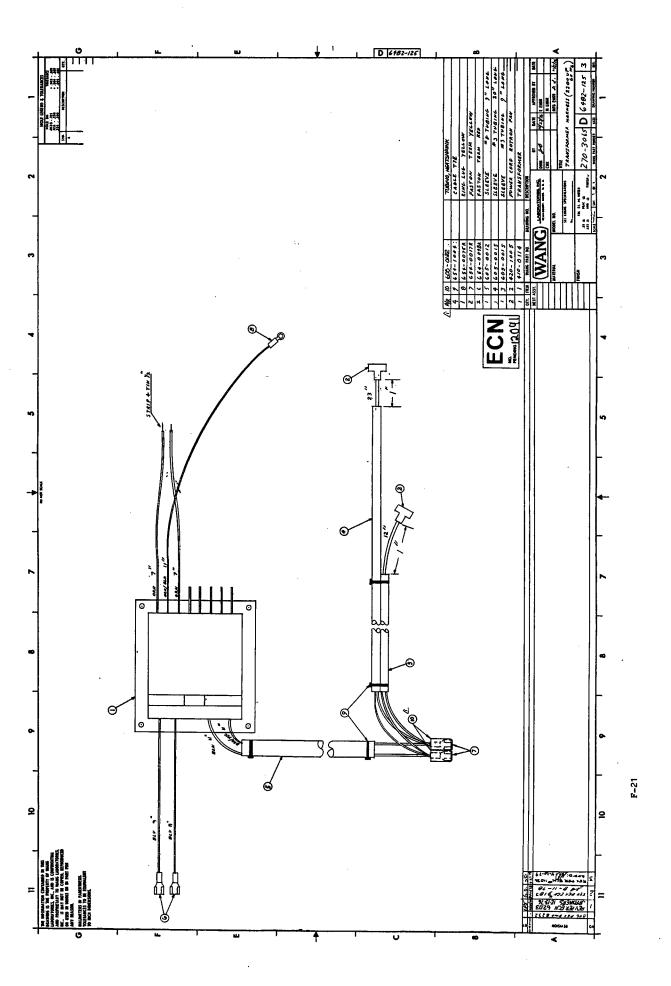

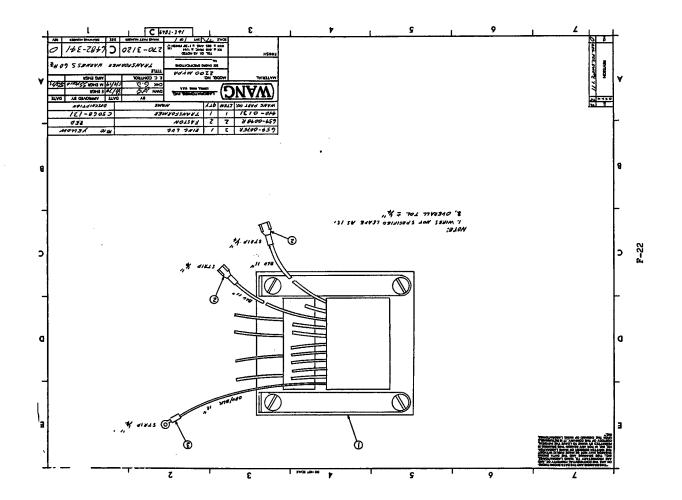

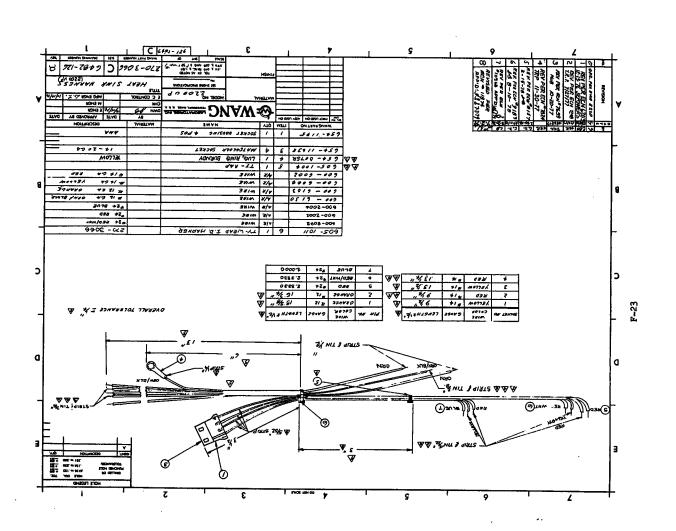

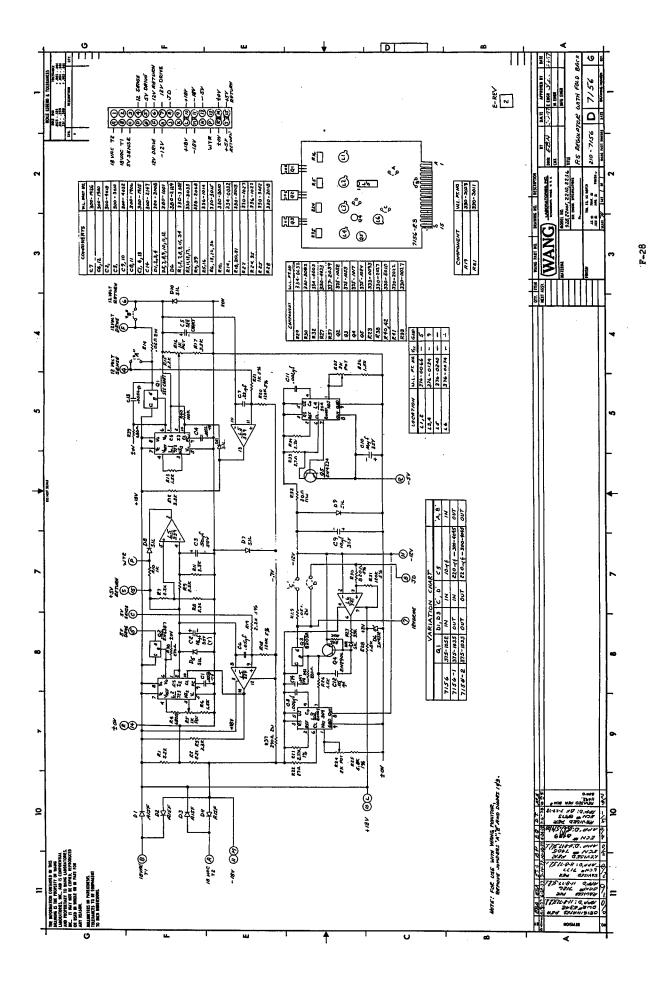

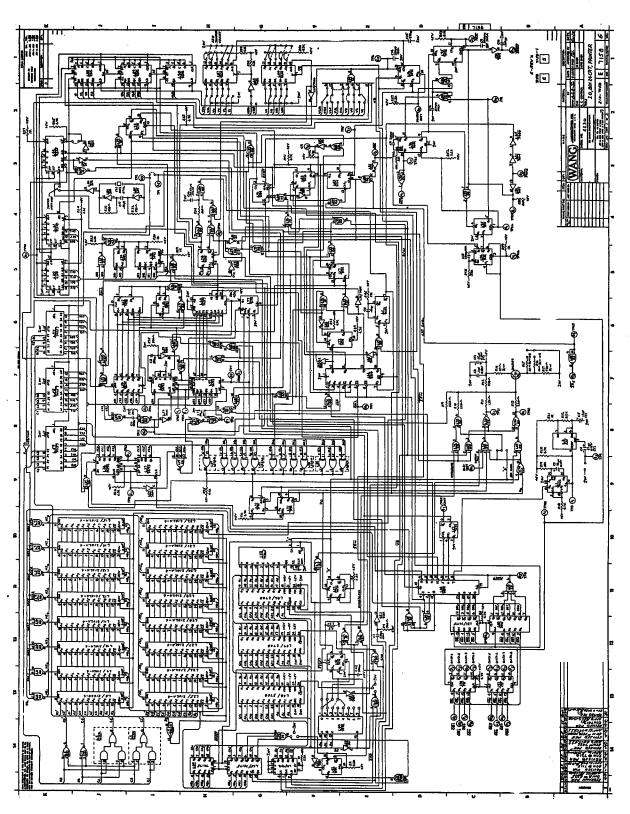

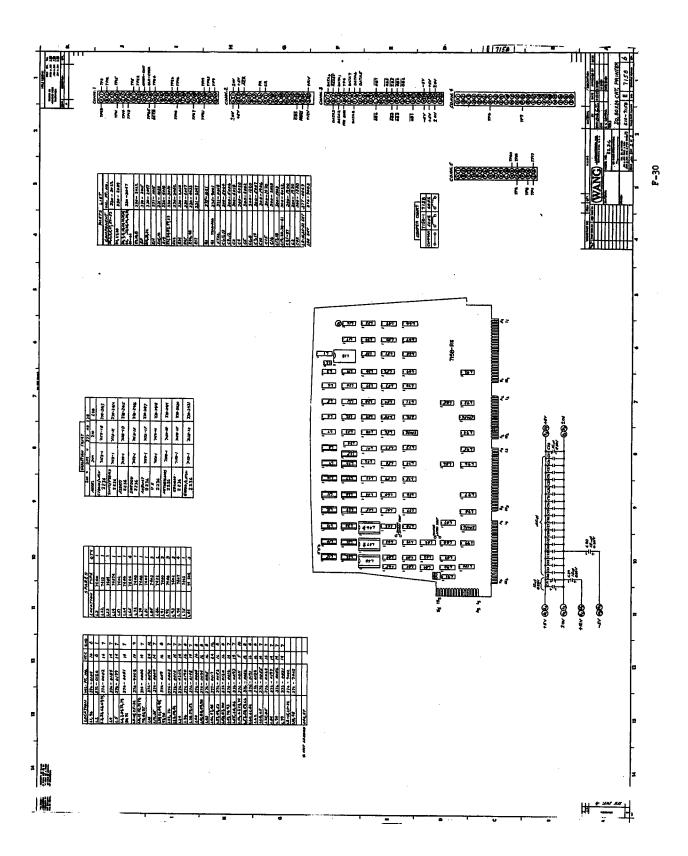

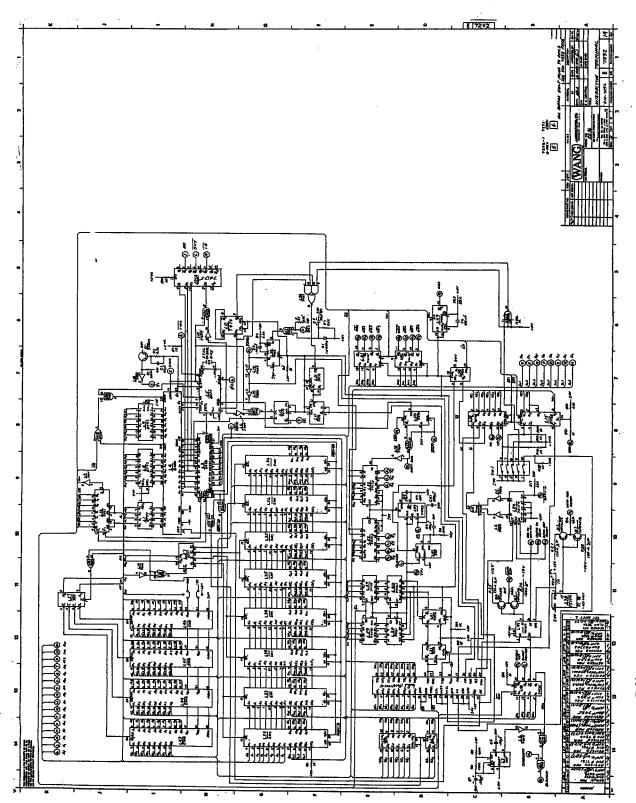

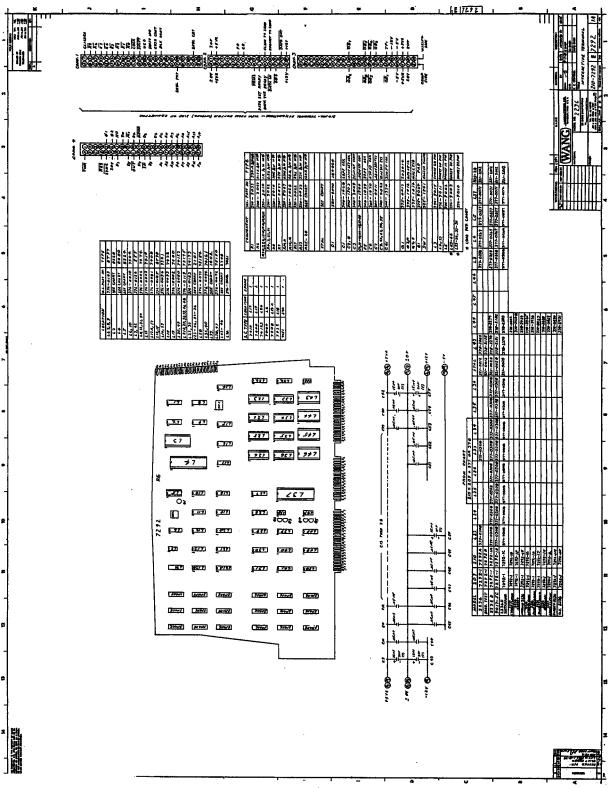

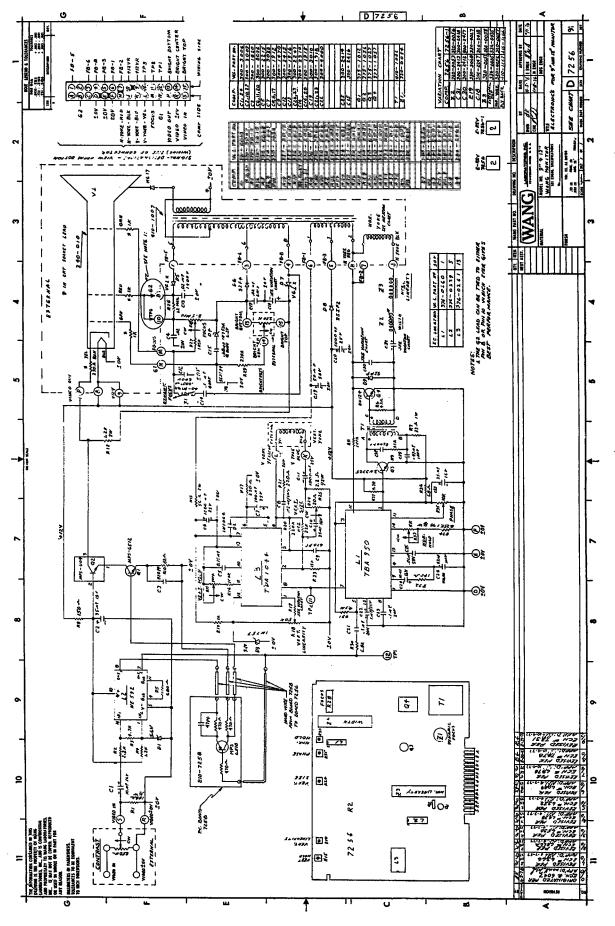

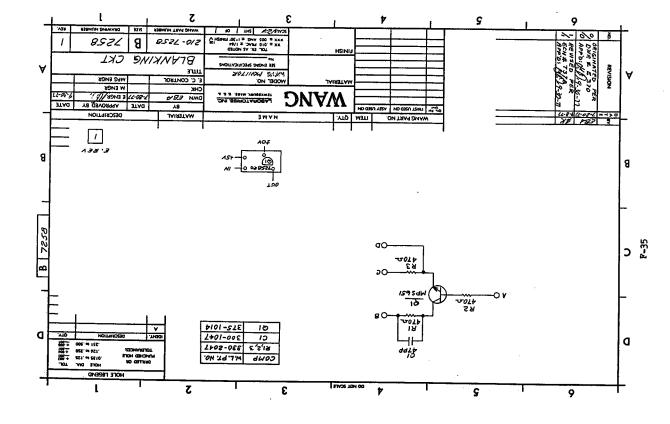

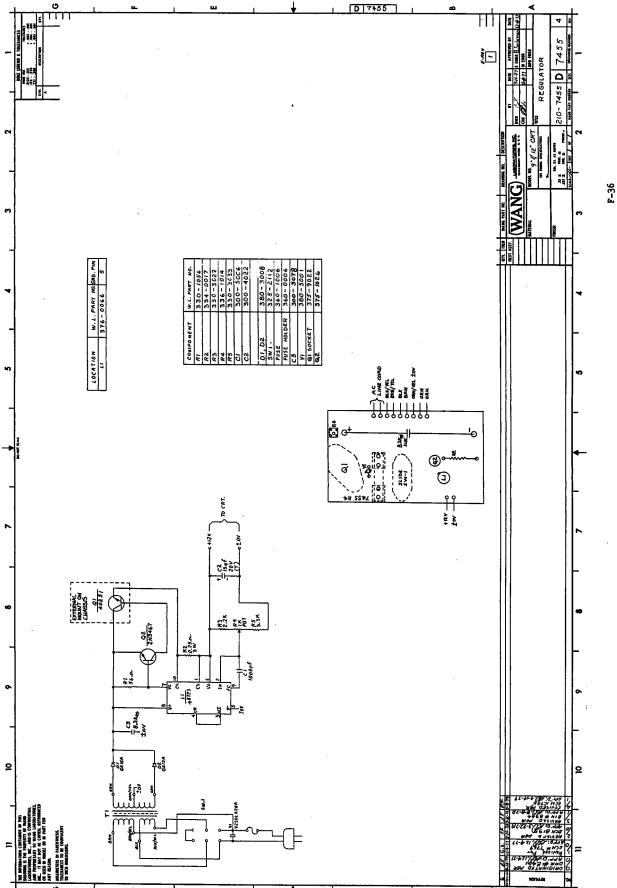

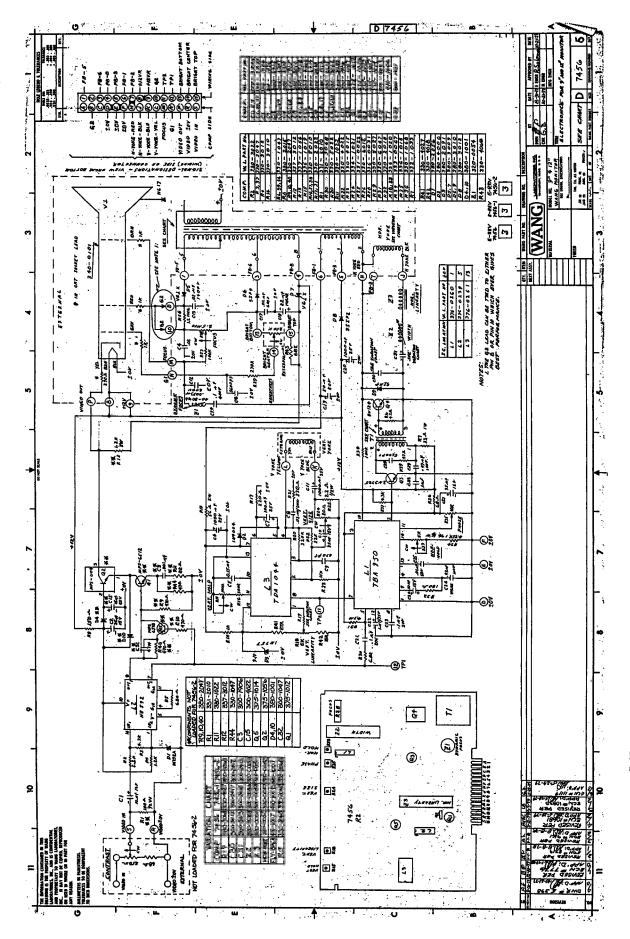

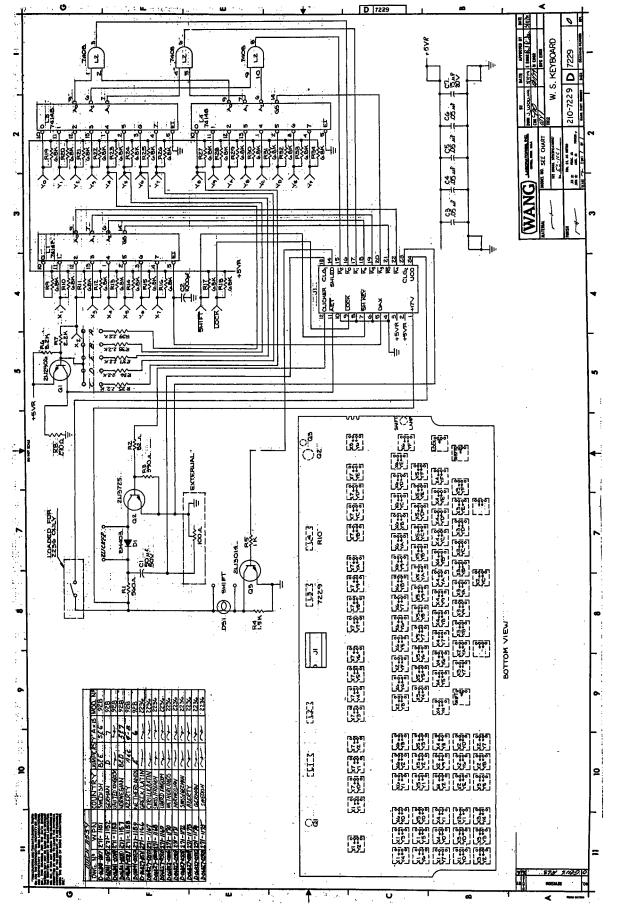

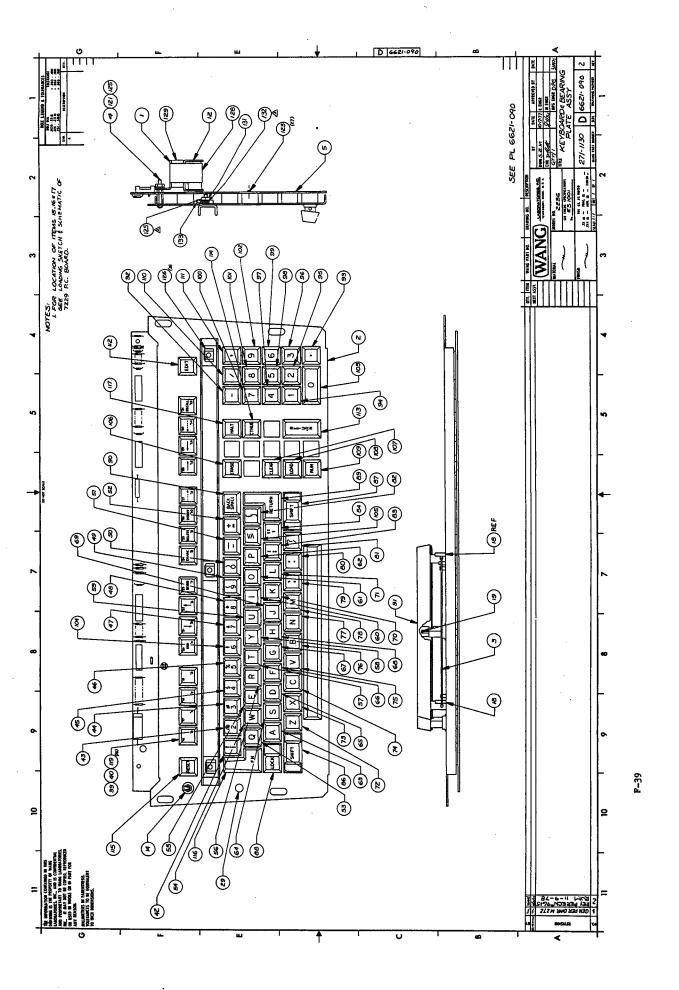

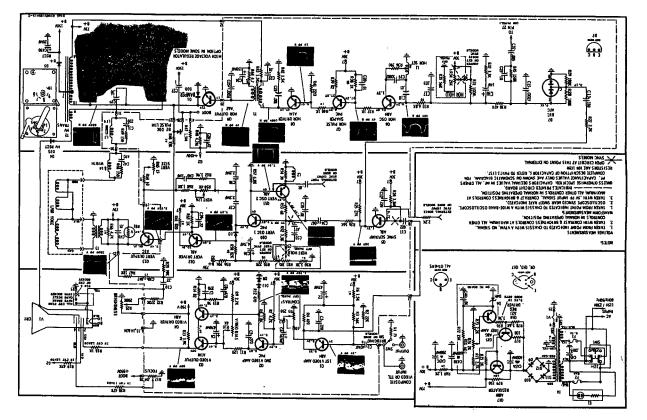

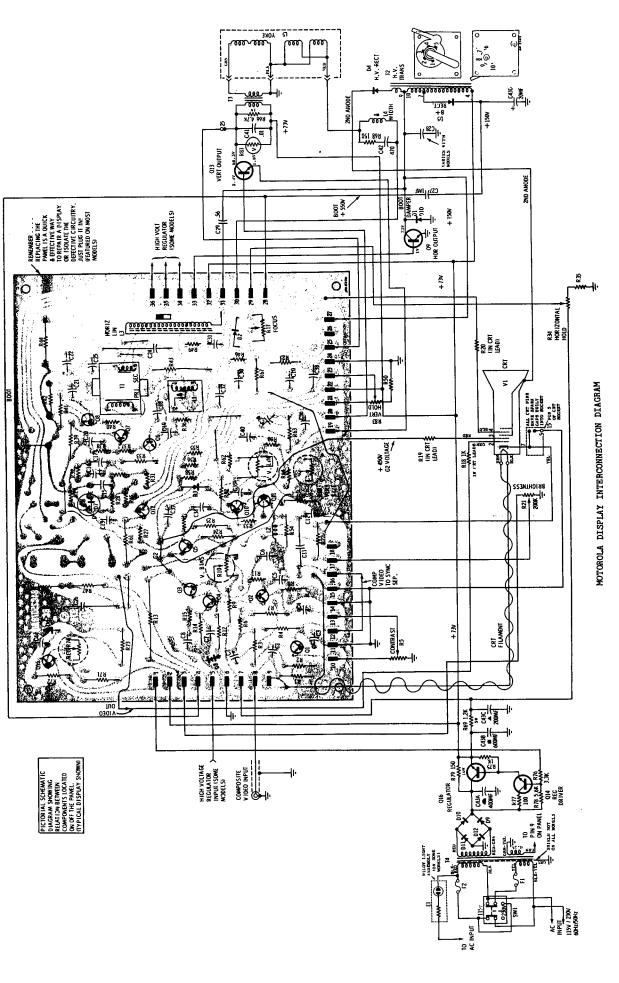

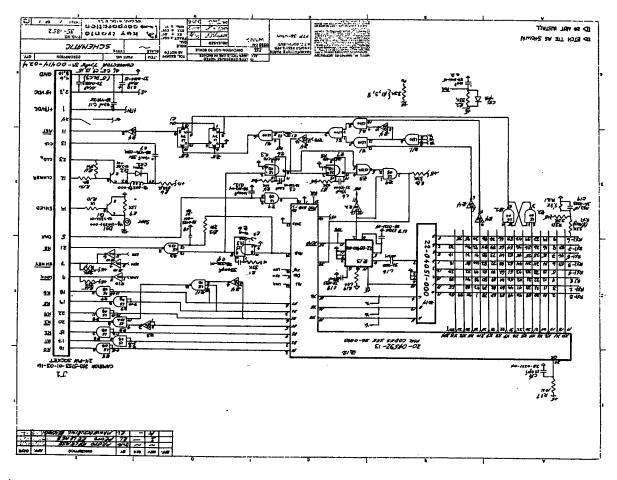

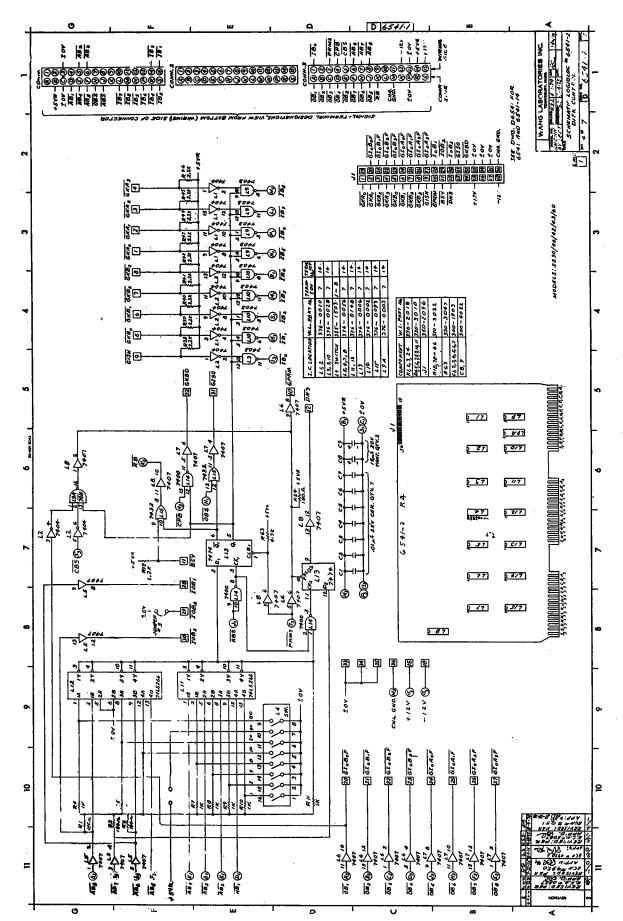

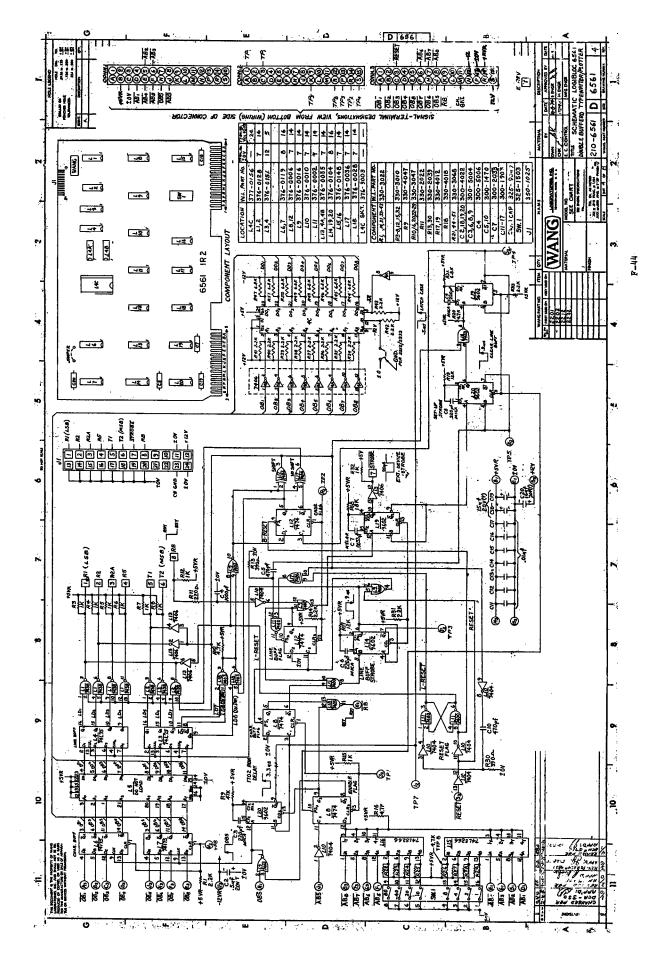

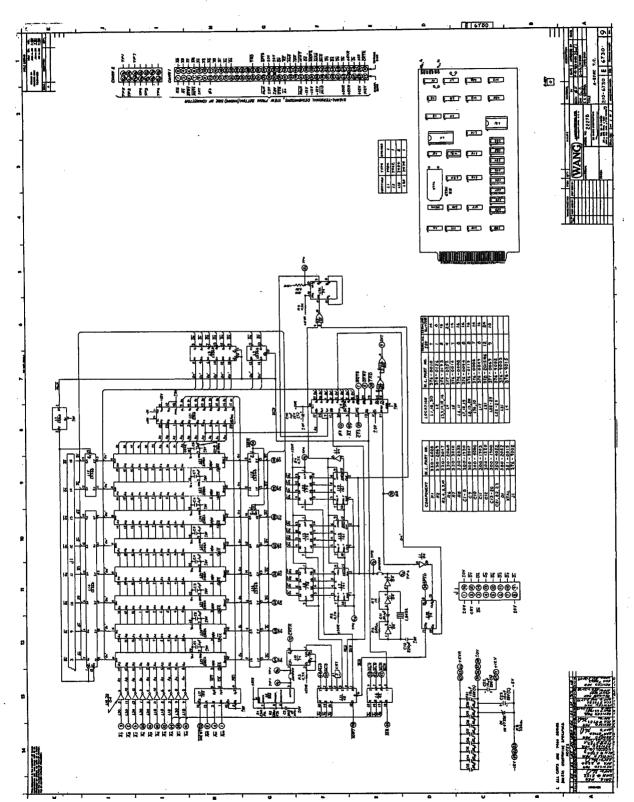

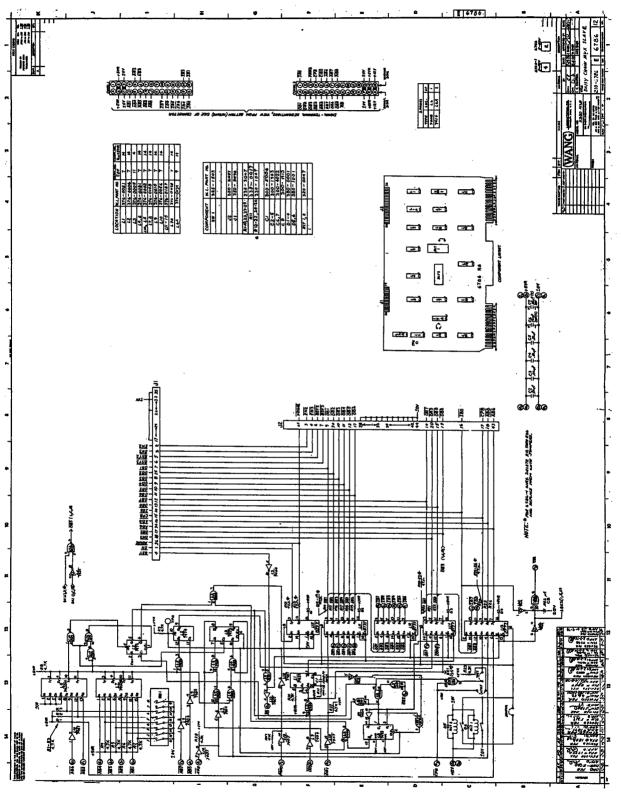

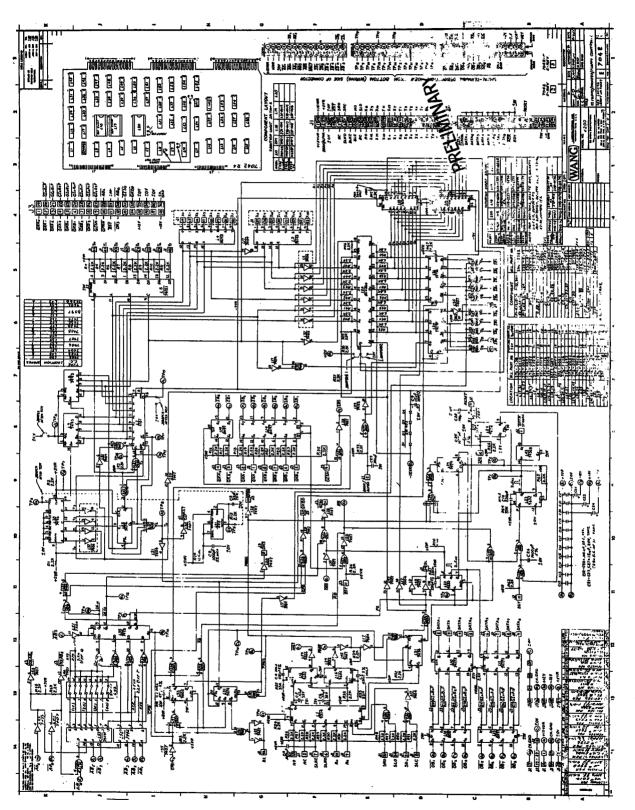

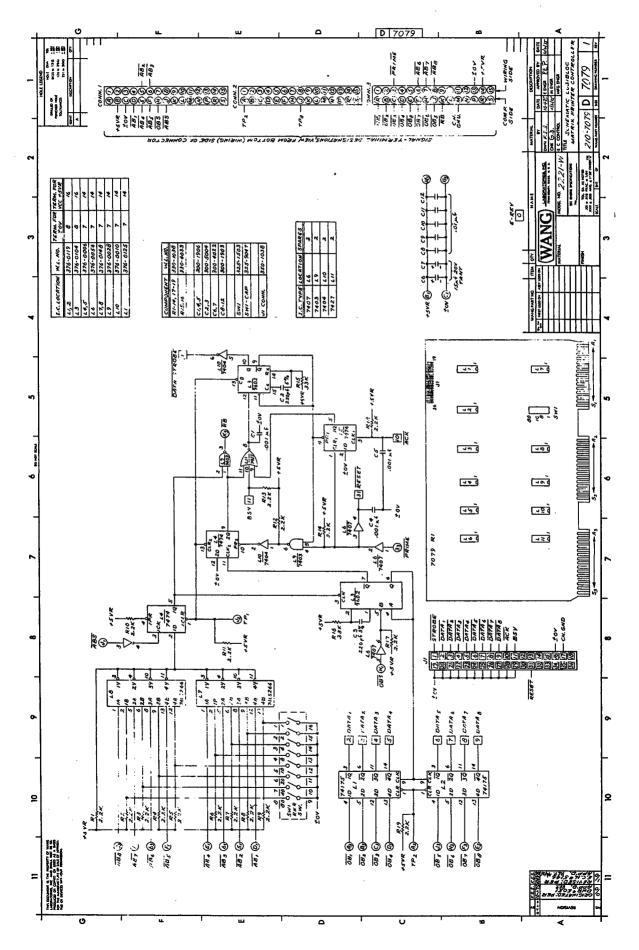

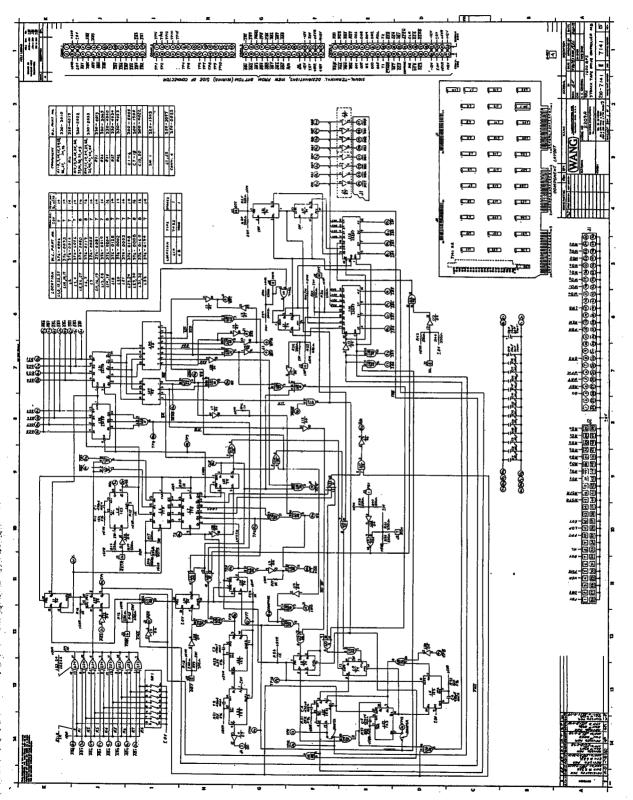

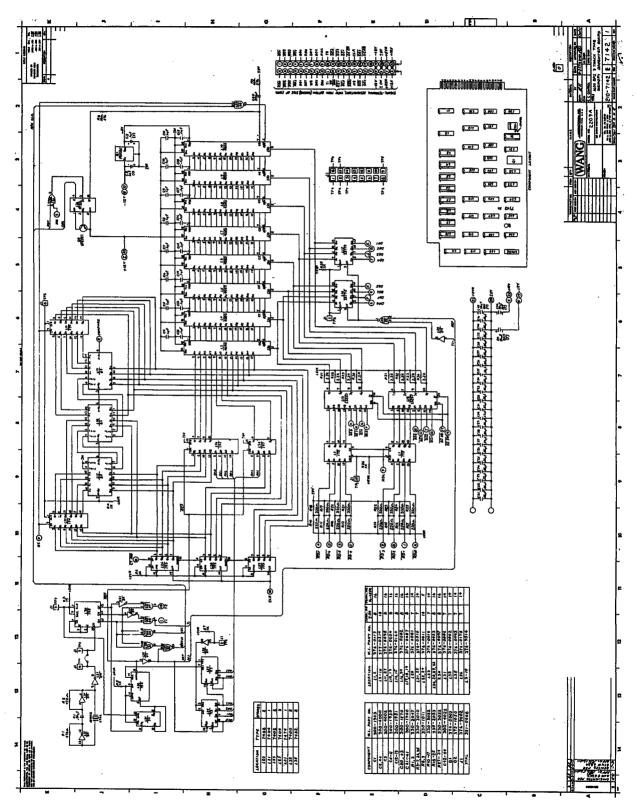

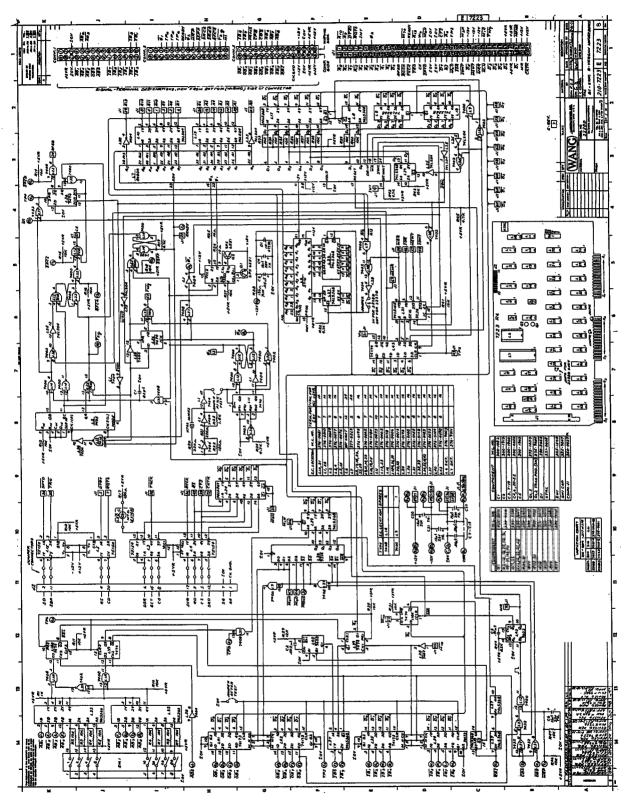

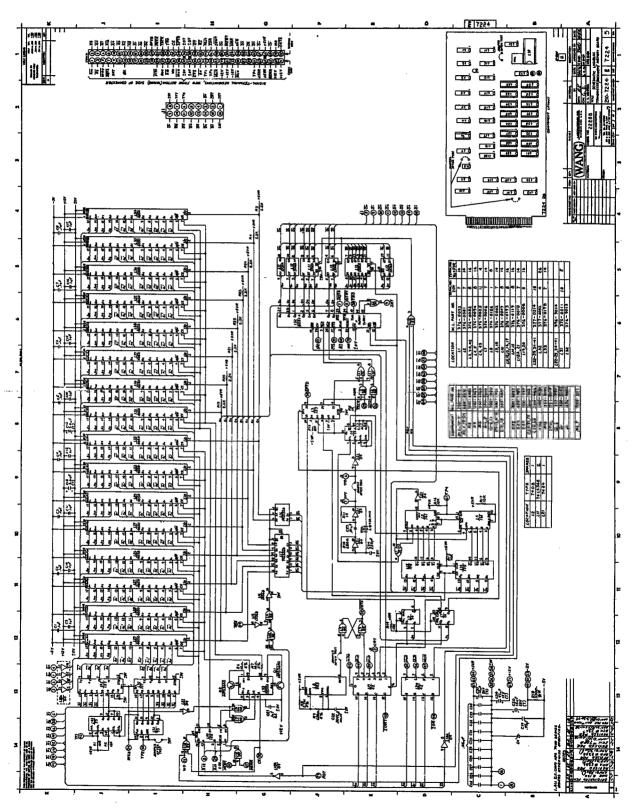

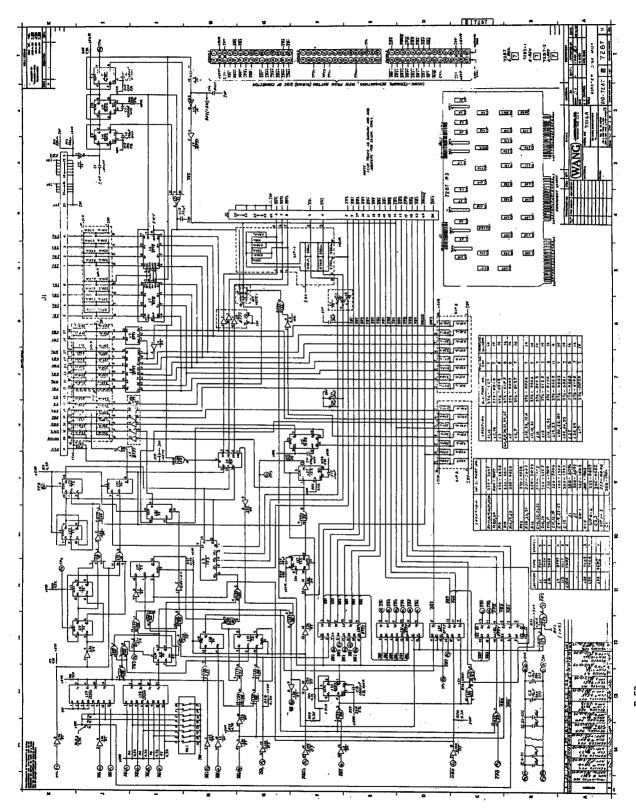

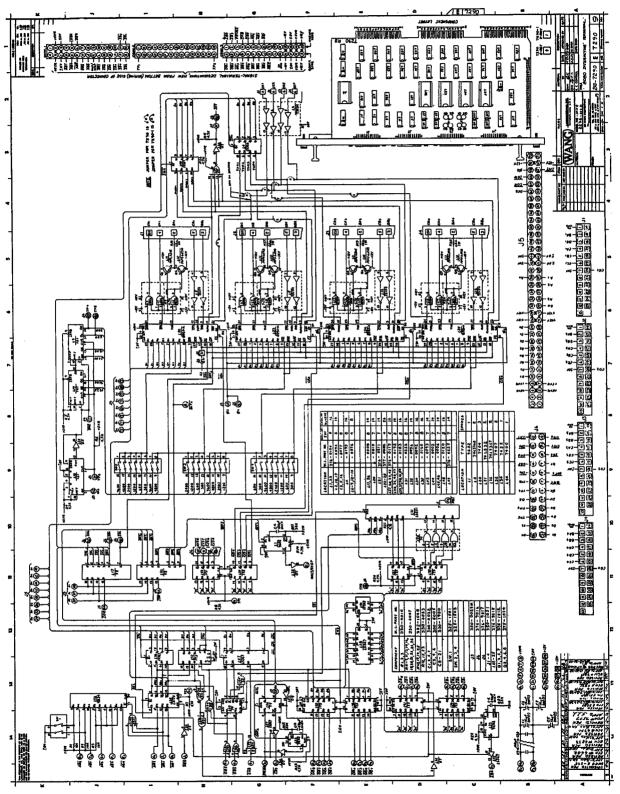

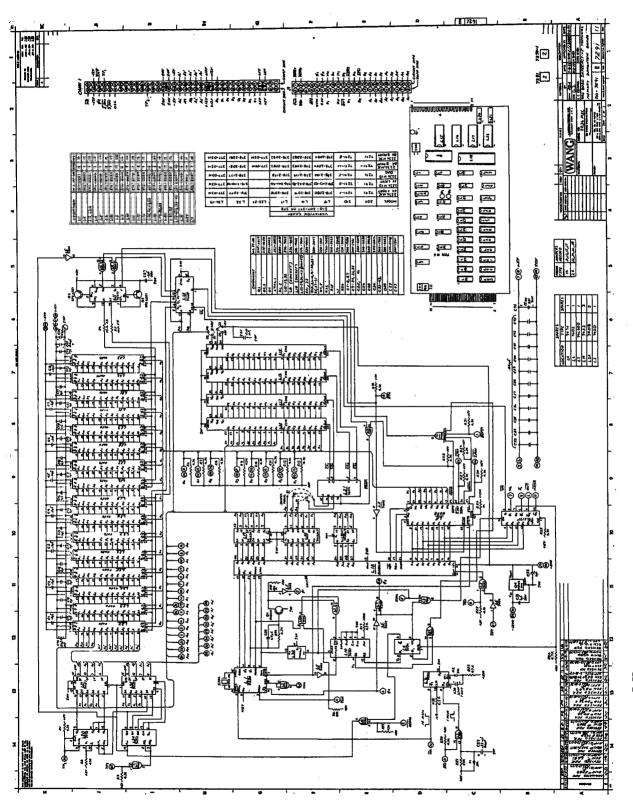

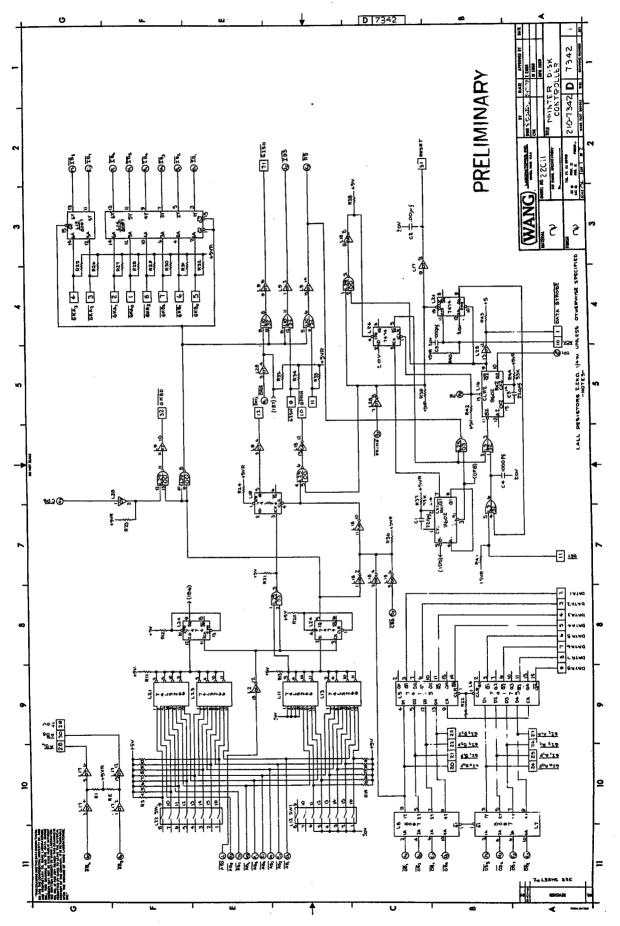

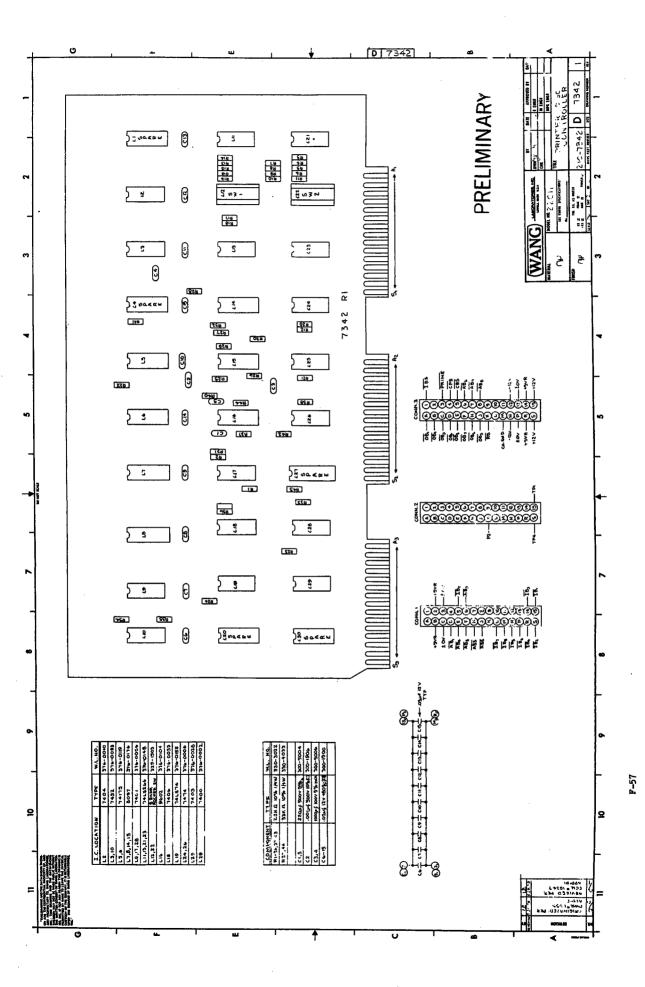

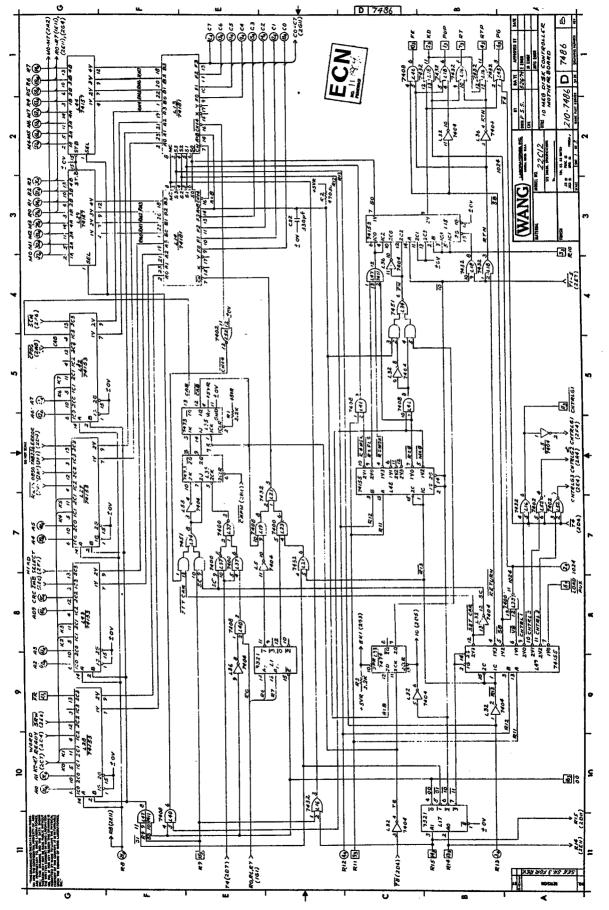

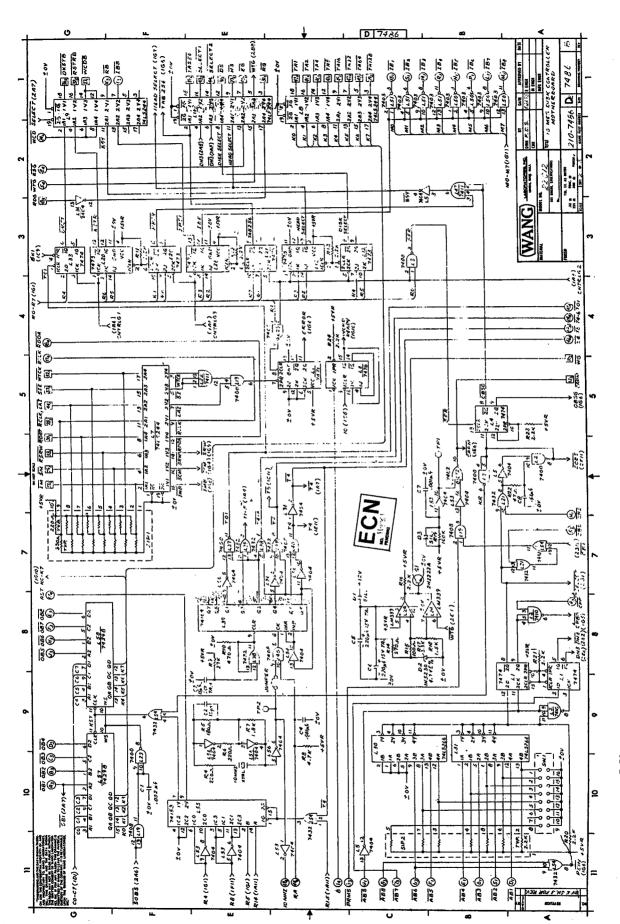

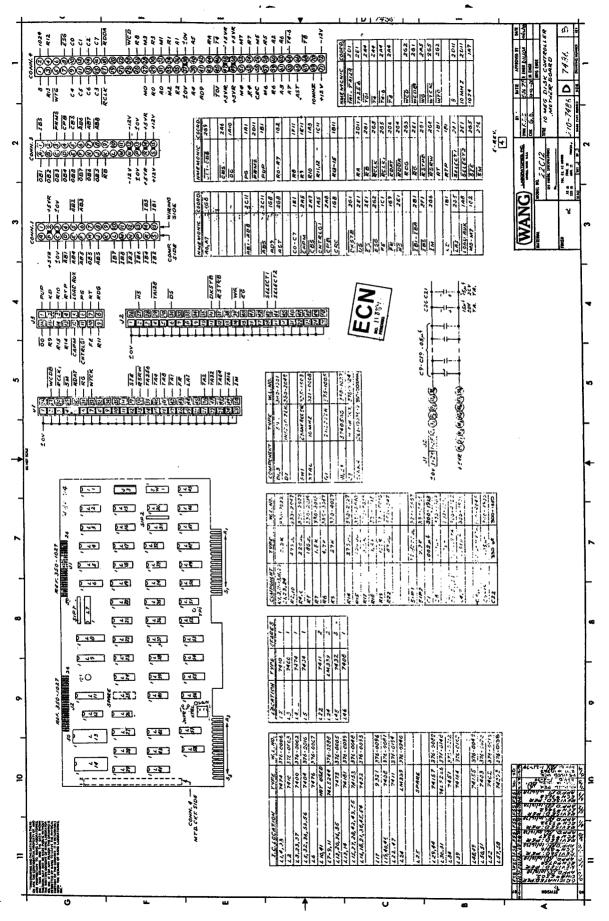

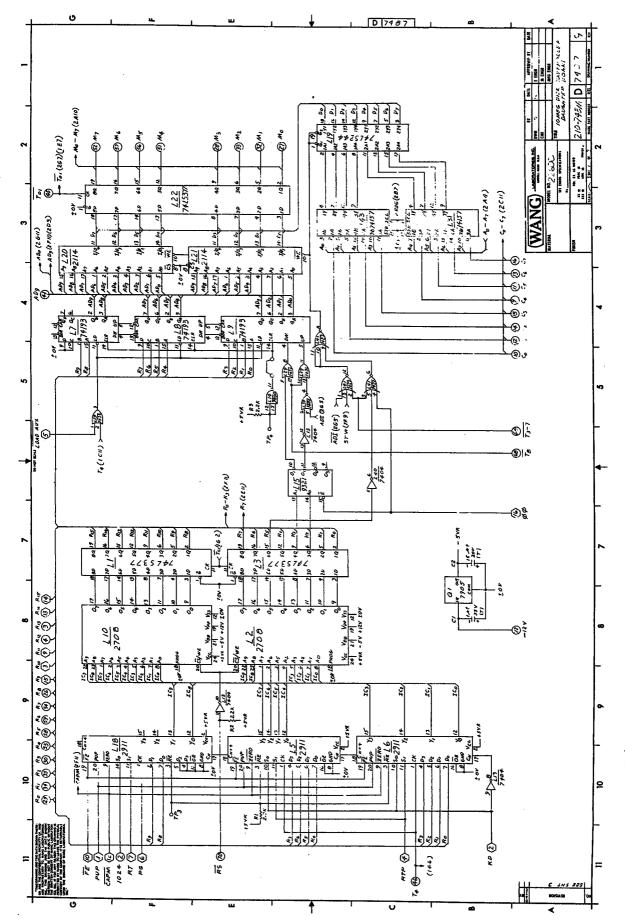

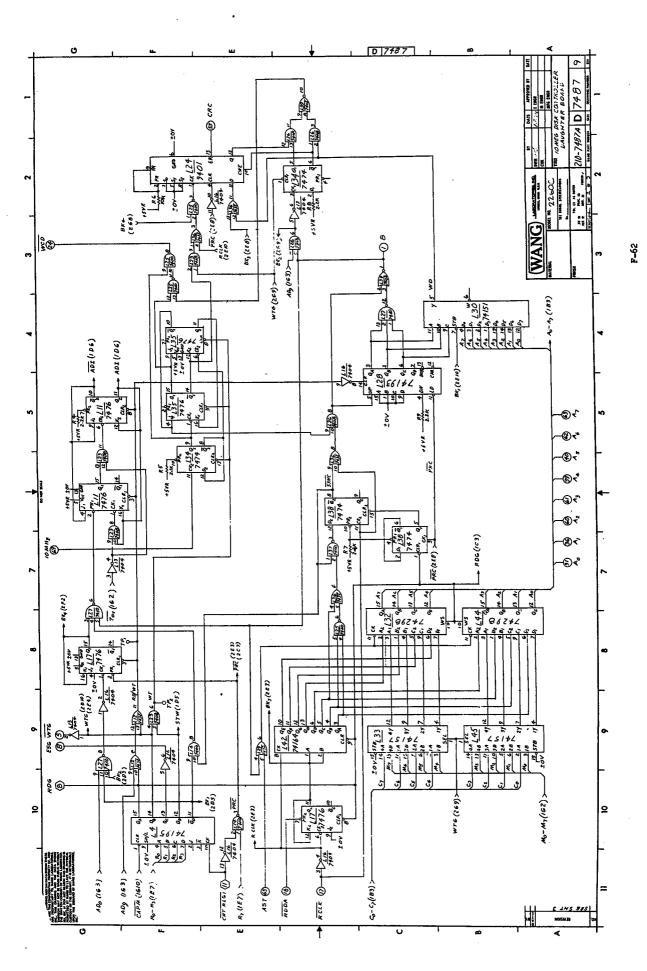

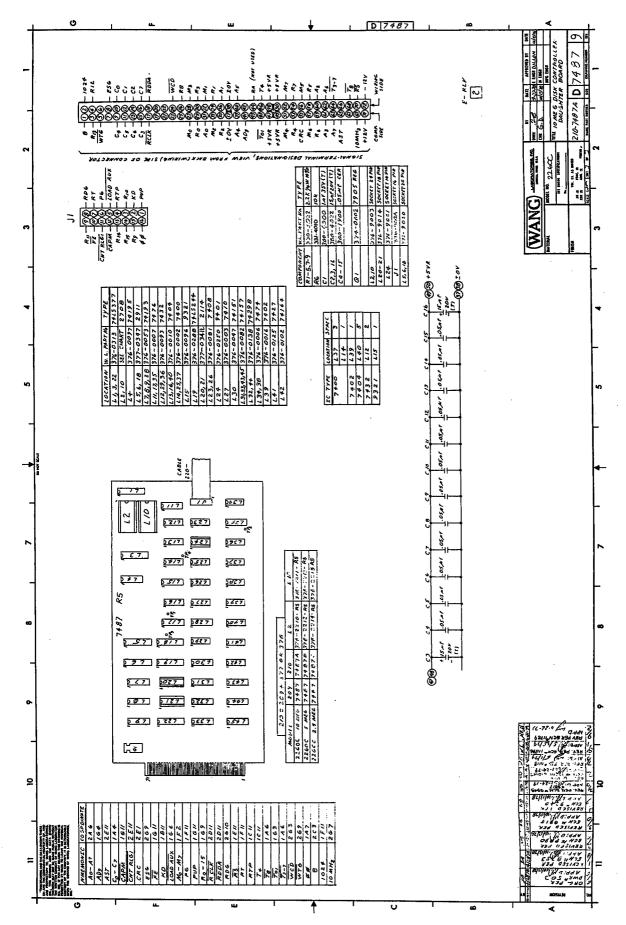

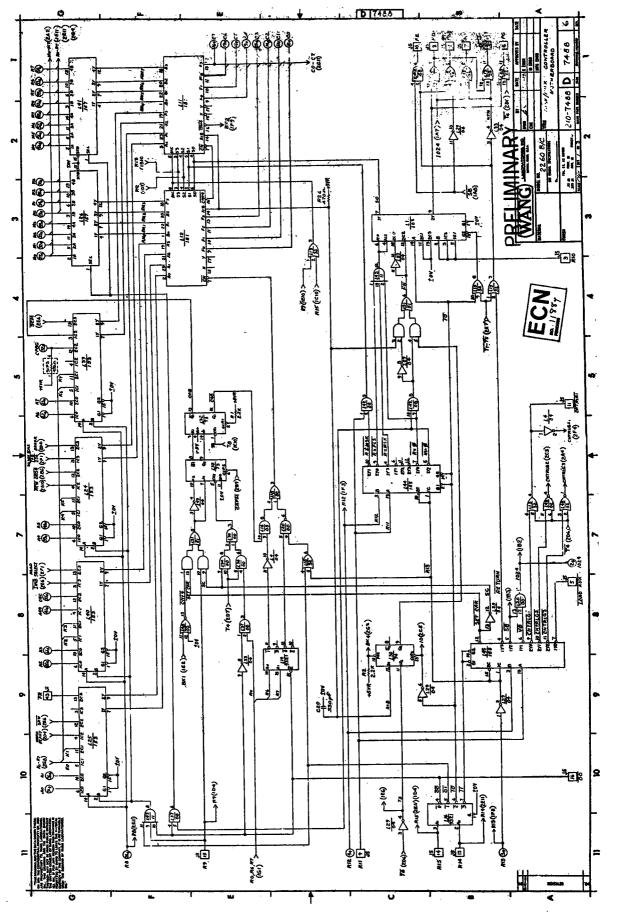

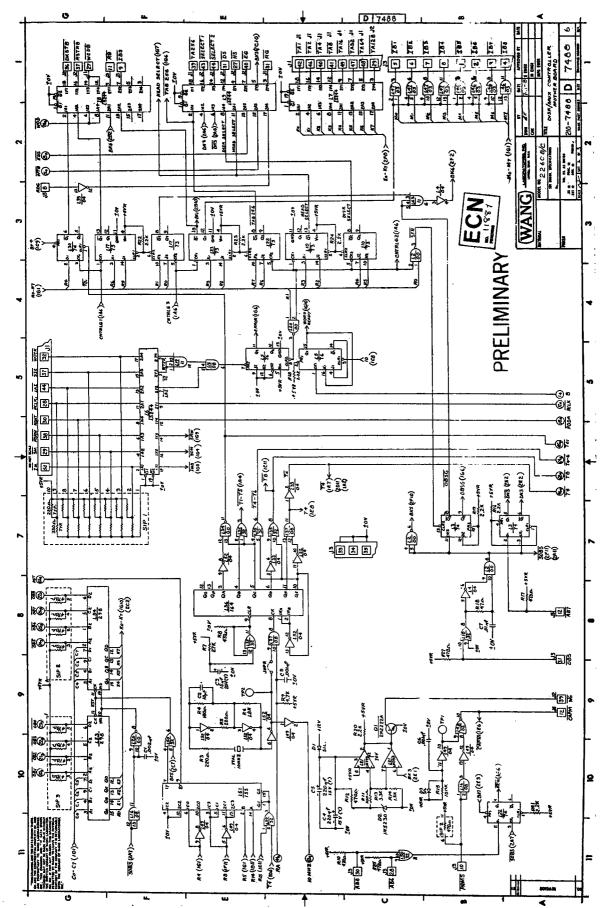

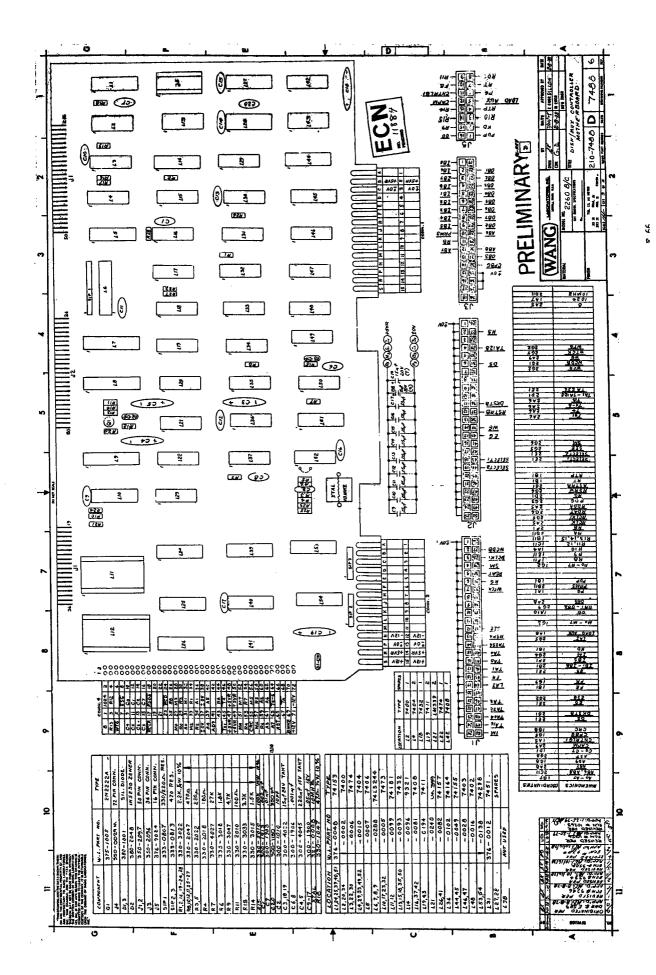

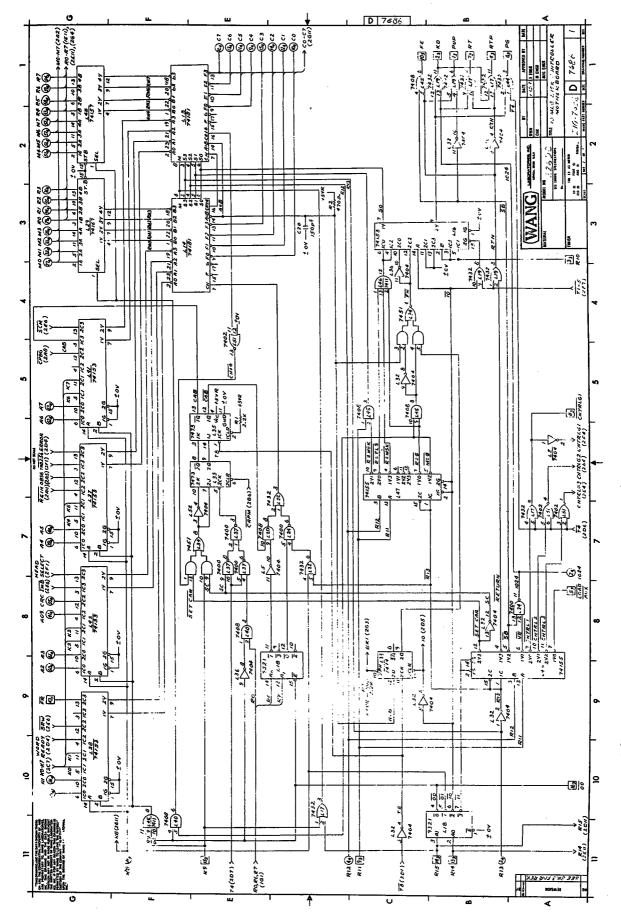

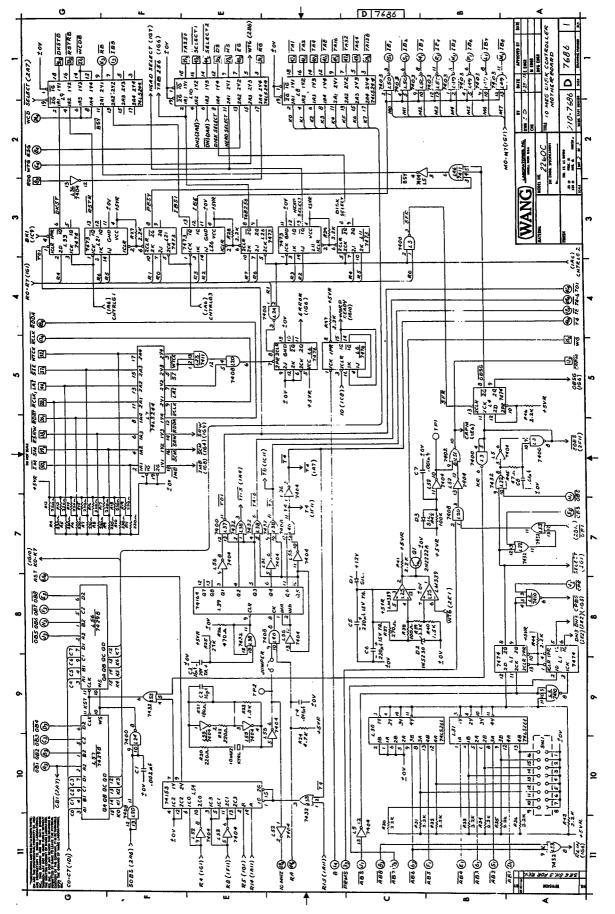

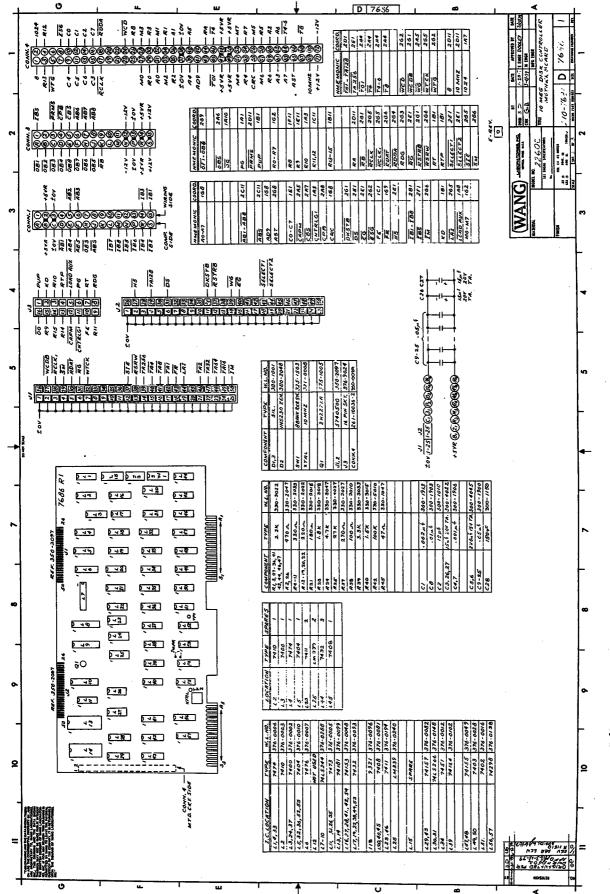

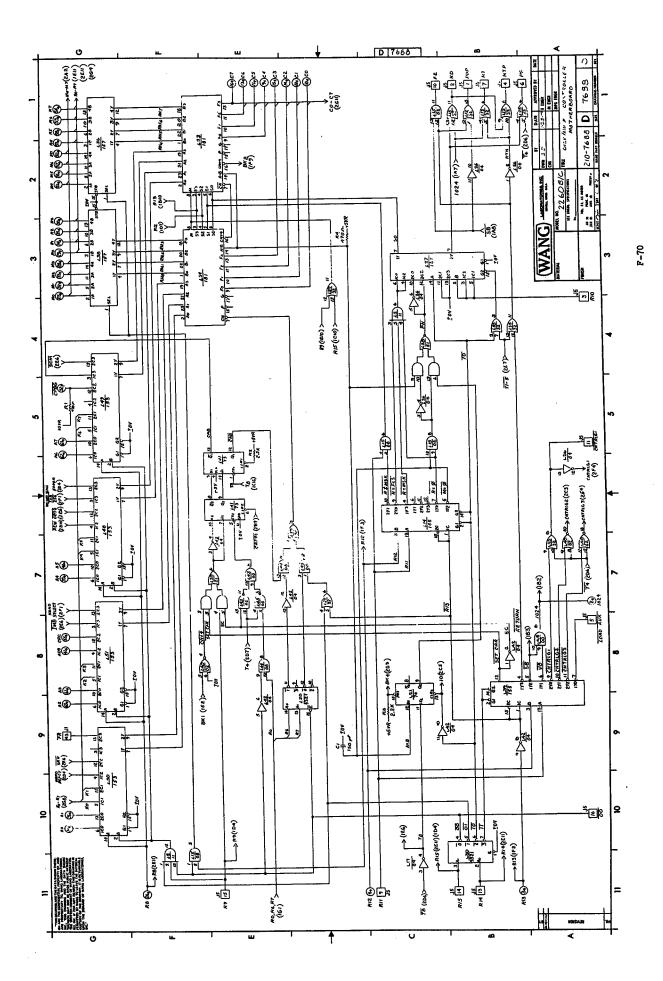

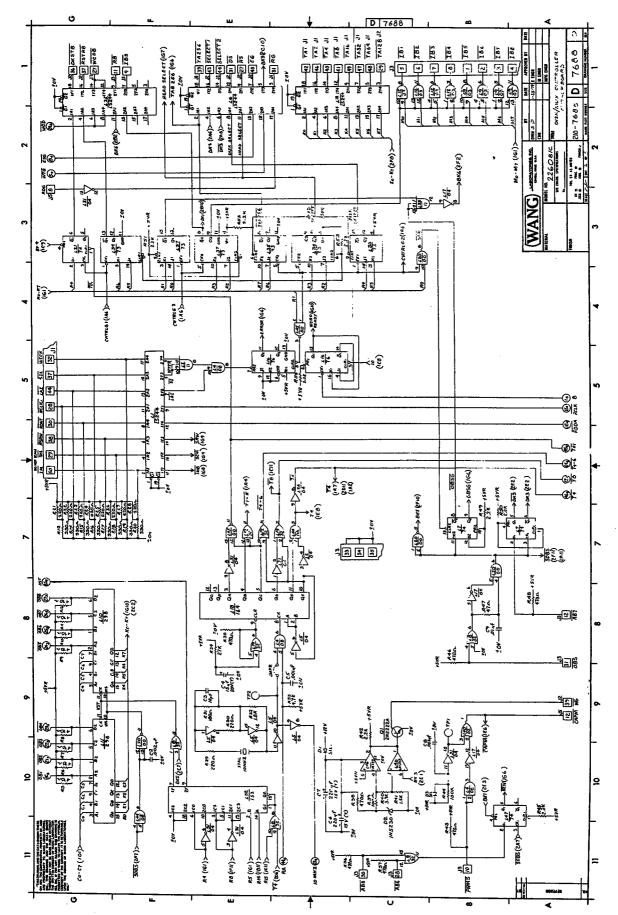

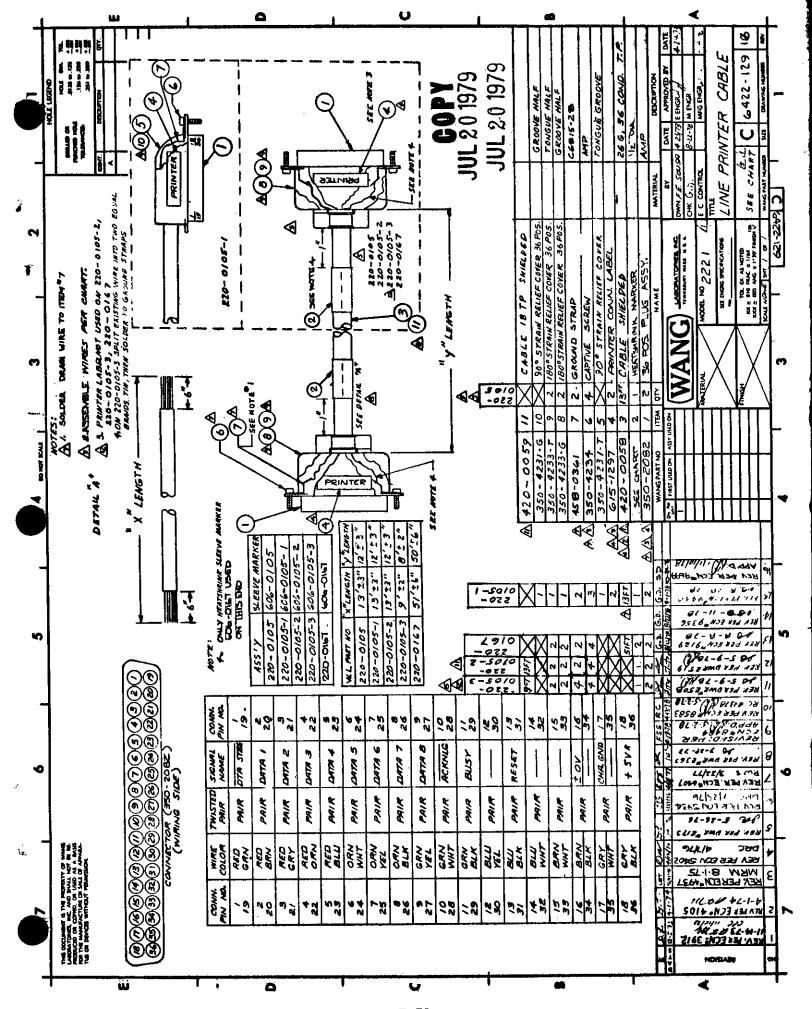

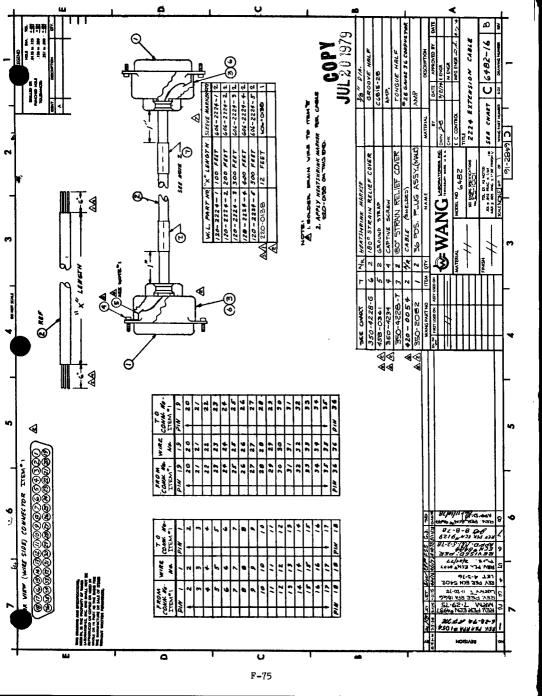

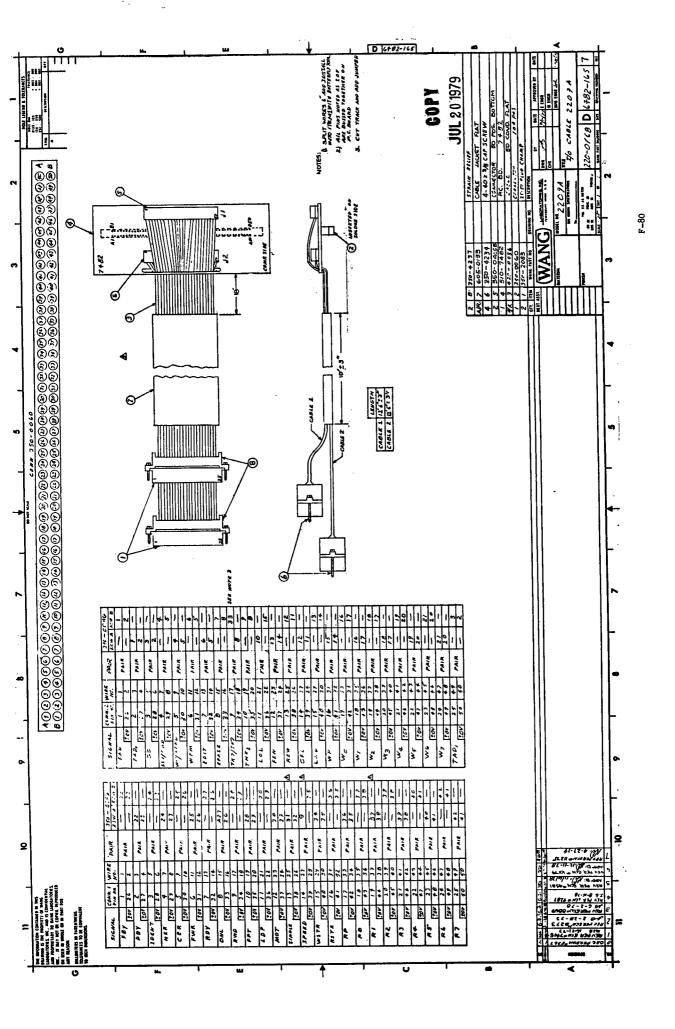

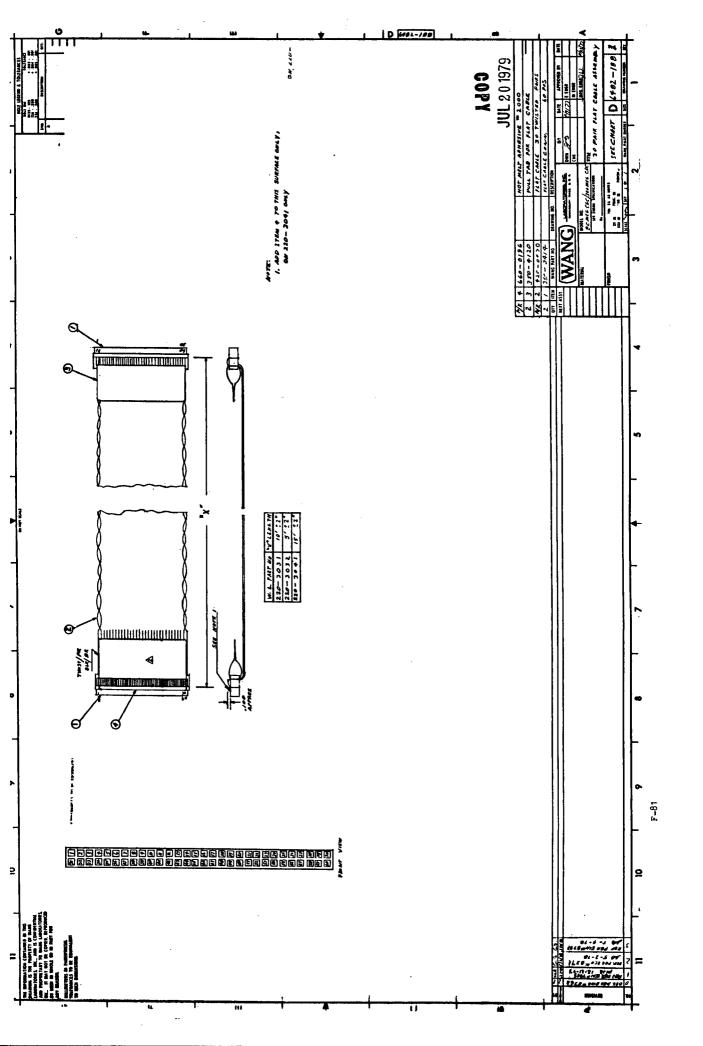

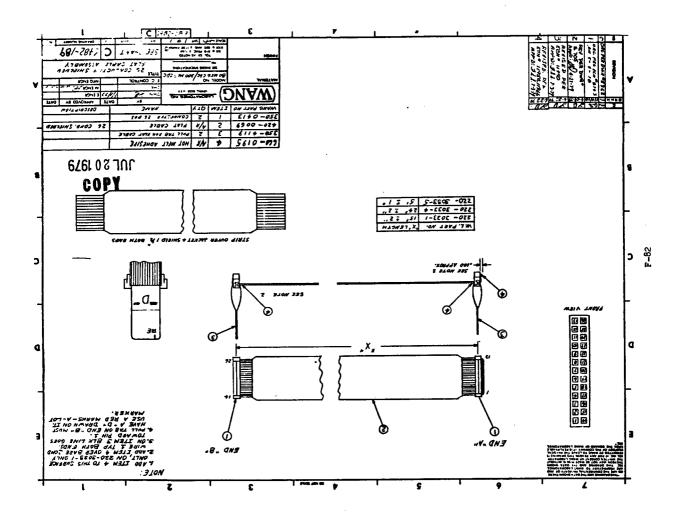

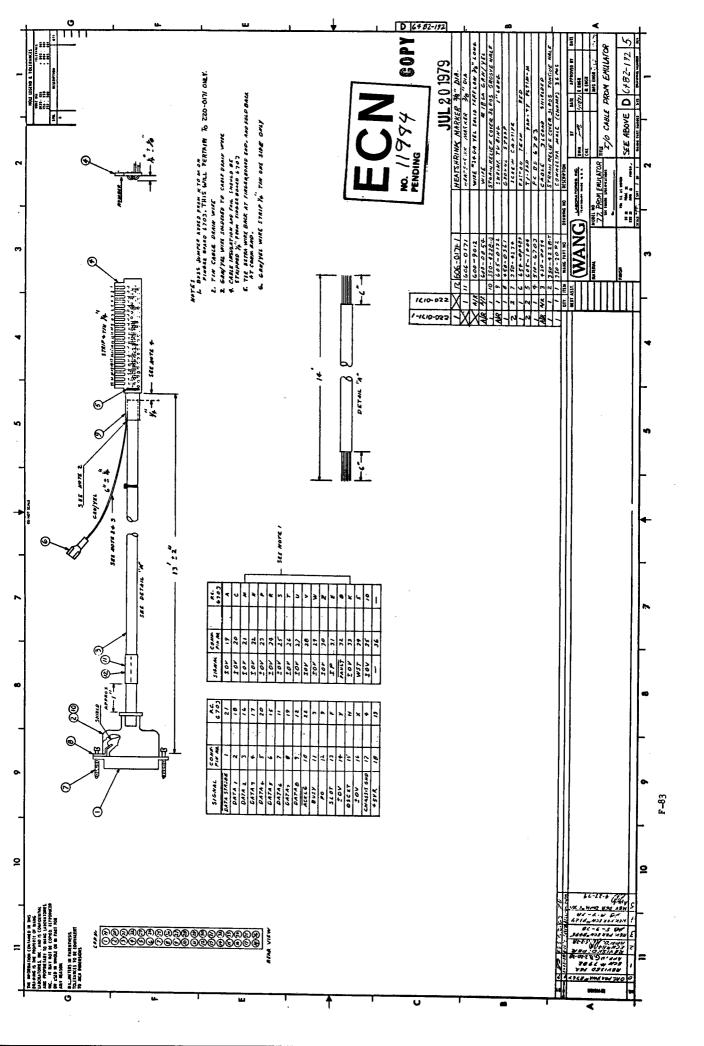

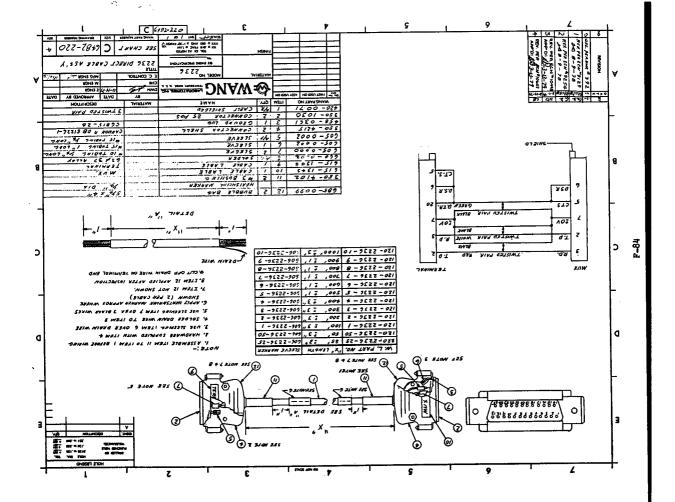

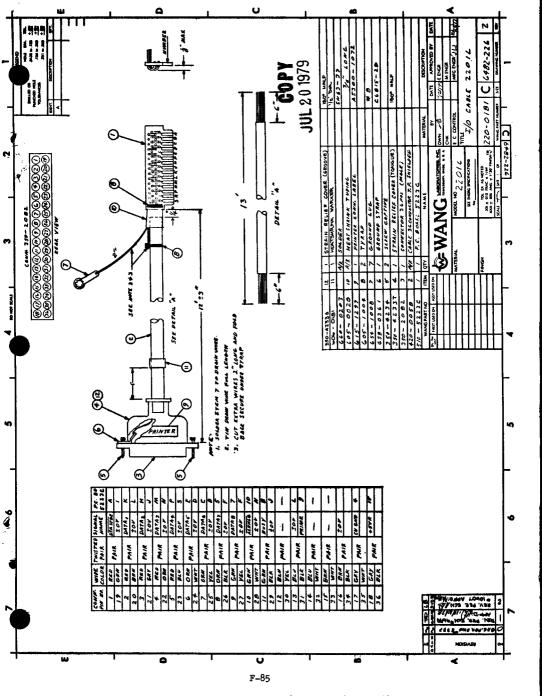

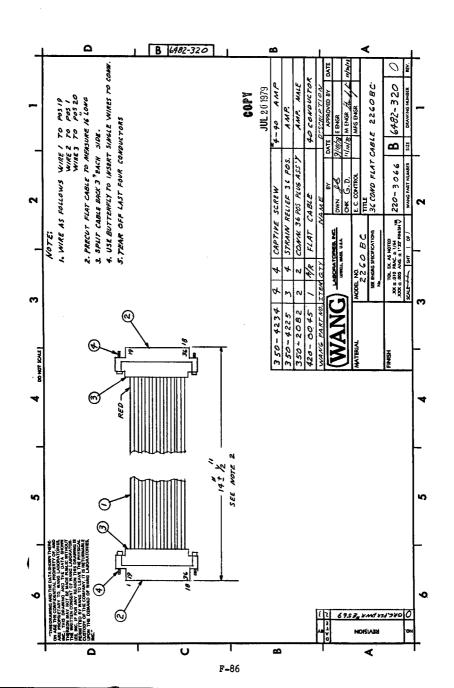

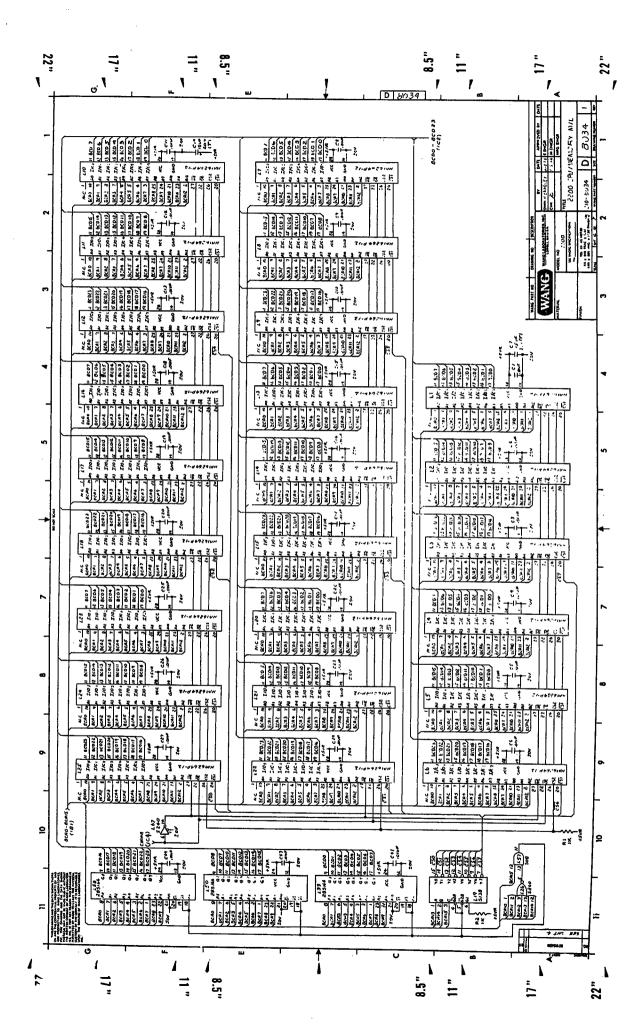

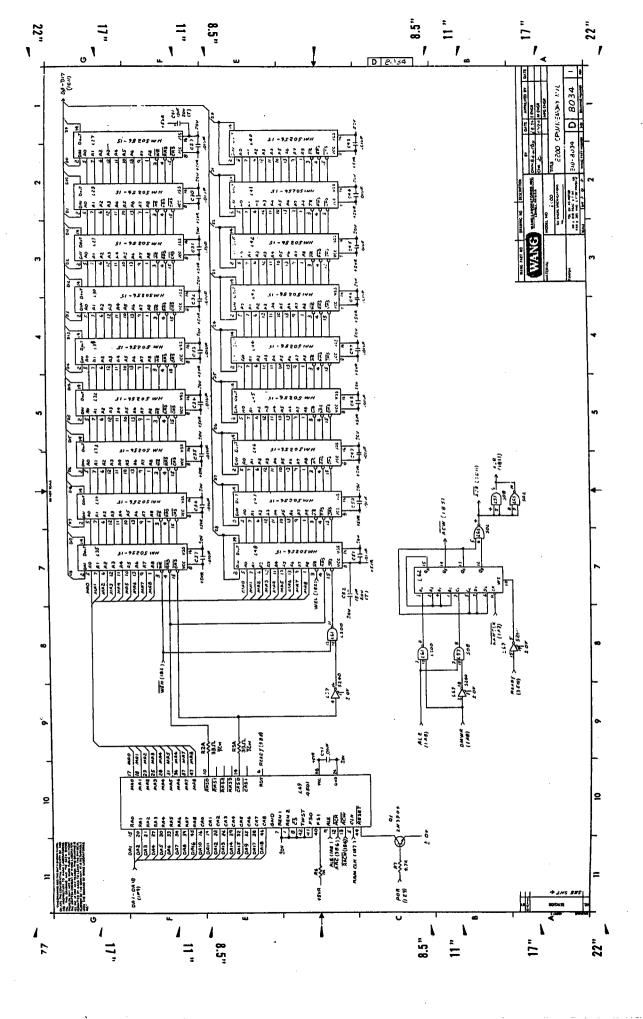

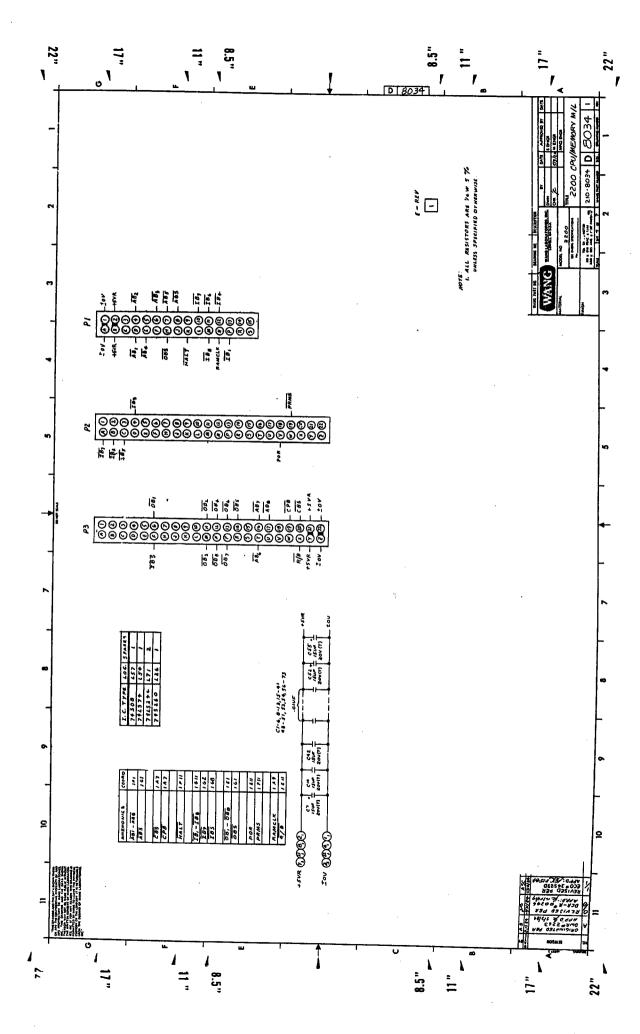

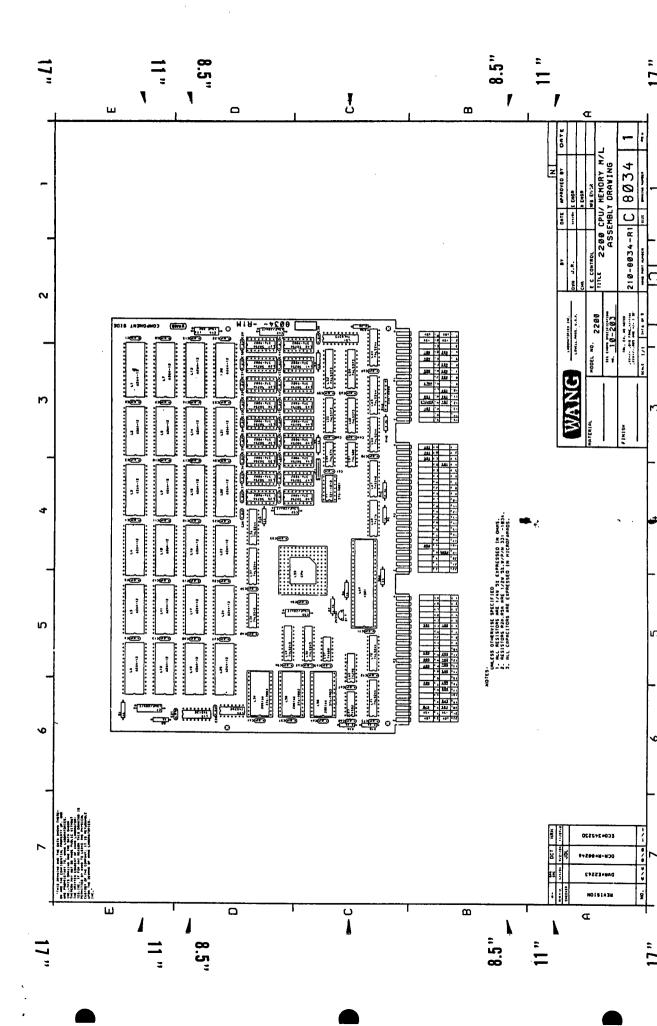

|         | IX F ELECTRICAL SCHEMATICS AND ASSEMBLY DRAWINGS F-1                                                                                                                                                                                 |

|         | IX G 2200MVP-128/512 G-1                                                                                                                                                                                                             |

|         | IX H 2275 MULTIPLEXER/MULTIPLEXER EXTENDER OPTION                                                                                                                                                                                    |

| APPEND: | IX I CPU/MEMORY PCB UPGRADE OPTIONS I-1                                                                                                                                                                                              |

# SECTION 3 SYSTEM INSTALLATION

#### 3.1 GENERAL

This section contains installation, checkout, and system interconnection instructions for the Model 2200MVP computer system. Because of the wide range of peripherals available to this system, it would be impractical to present here a full installation procedure for each. All available peripherals are fully documented in other Wang or OEM publications. For complete information on any specific peripherals, refer to the 2200MVP SYSTEM-LEVEL DOCUMENTATION list, contained in the preface of this manual.

### 3.2 UNPACKING AND INCOMING INSPECTION

Each peripheral model has its own inspection procedure. Refer to the maintenance publications named in the 2200MVP System-Level Documentation list for specific unpacking and inspection procedures. In all cases, the critical assemblies must be inspected, first for damage and then for proper adjustment.

The following general guidelines for unpacking and inspection apply to all 2200MVP system units:

- A. Check to be certain that all equipment (peripherals, cables, stands, etc.) has been delivered.

- B. Unpack each unit, using extreme caution, especially with the workstations. For shipping, larger peripherals are generally bolted to wooden skids and enclosed in cardboard shipping boxes. Carefully remove these packing containers, using pry bars and open-end wrenches as needed.

- C. Inspect each unit for shipping damage. Immediately report any physical damage to the shipping carrier and the Home Office.

- D. Move the units to their permanent locations. During transit, protect the cabinets from scratches, keeping the protective wrapping on the units until they are in their final positions.

- E. Remove the covers from the CPU and other peripheral devices.

Remove any shipping clamps. Inspect the units for damaged or loosened assemblies. Also check for loose hardware. Ensure that the units are throughly clean. Be certain that each printed circuit board, including the power supply board, is in its proper location and fully seated.

- F. Assemble the peripherals, as necessary. For workstations, this step will include the installation of PC boards; for other peripherals, this step will include the installation of accessories, such as paper racks for printers.

- G. Inspect the storage media (diskettes, tapes, etc.) for damage.

- H. Check the electrical wiring of the computer room to ensure that the electrical requirements of the 2200MVP system will be met. Pay particular attention to grounding. This topic is covered in detail in Section 2.

- H. Set the device switches and baud rate switches where applicable, as described in the following paragraphs. Also where applicable, set the AC voltage (115/230) and line frequency (50Hz/60Hz) switches.

- I. Route peripheral cables to the CPU as described in section 3.5.

#### 3.3 BAUD RATE SELECTION

Four 2236D Terminals can be attached to one 2236MXD controller, and a maximum of two 2236MXD controllers may be used in a 2200MVP system.

The baud rate setting of the each port of the 2236MXD controller must match the baud rate setting of its corresponding terminal. For systems used in local operation (without modem), the baud rate may be set as high as 19.2K baud, regardless of cable length. For remote operation, the baud rate of the terminal must be set to match the baud rate of the modem. Asynchronous communications modems are available for transmission speeds as high as 2400 baud.

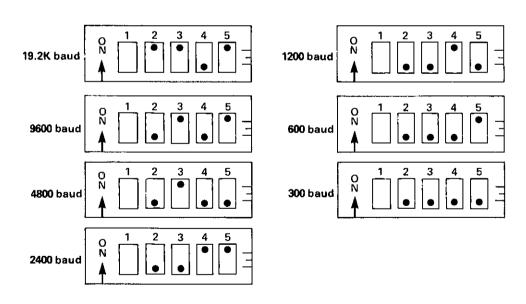

#### 3.3.1 2236D TERMINAL 5-BANK BAUD RATE SWITCH

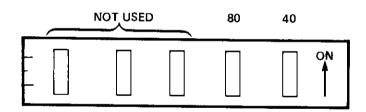

Set the baud rate switch on the 7292-1 board of each 2236D Terminal. When the terminal cover is on, access to the baud rate switch is through the large plug-button on the rear of the cover. See Figures 3-1 and 3-2. Set the switches of the five-bank switch as follows:

| Switch: | 1  | 2   | 3   | 4   | 5   | Baud Rate |

|---------|----|-----|-----|-----|-----|-----------|

|         | ON | OFF | OFF | OFF | OFF | 300       |

|         | ON | OFF | OFF | OFF | ON  | 600       |

|         | ON | OFF | OFF | ON  | OFF | 1200      |

|         | ON | OFF | OFF | ON  | ON  | 2400      |

|         | ON | OFF | ON  | OFF | OFF | 4800      |

|         | ON | OFF | ON  | OFF | ON  | 9600      |

|         | ON | ON  | ON  | OFF | ON  | 19.2K     |

|         |    |     |     |     |     |           |

In all cases switch 1 is ON to enable parity error detection. Switch 1 must always be ON for proper operation.

FIGURE 3-1 ACCESS TO THE BAUD RATE SWITCH

FIGURE 3-2 BAUD RATE SWITCH SETTINGS FOR THE 2236D TERMINAL

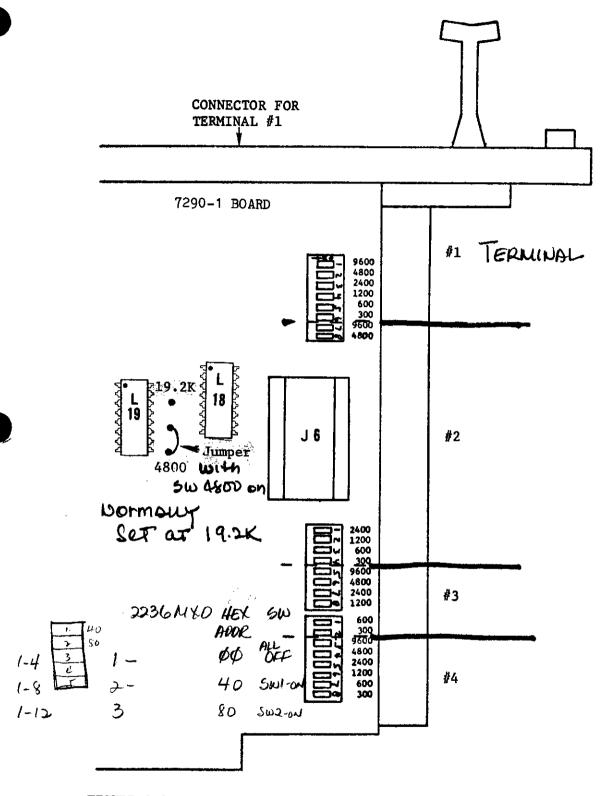

FIGURE 3-3 2236MXD CONTROLLER - BAUD RATE SWITCH IDENTIFICATION

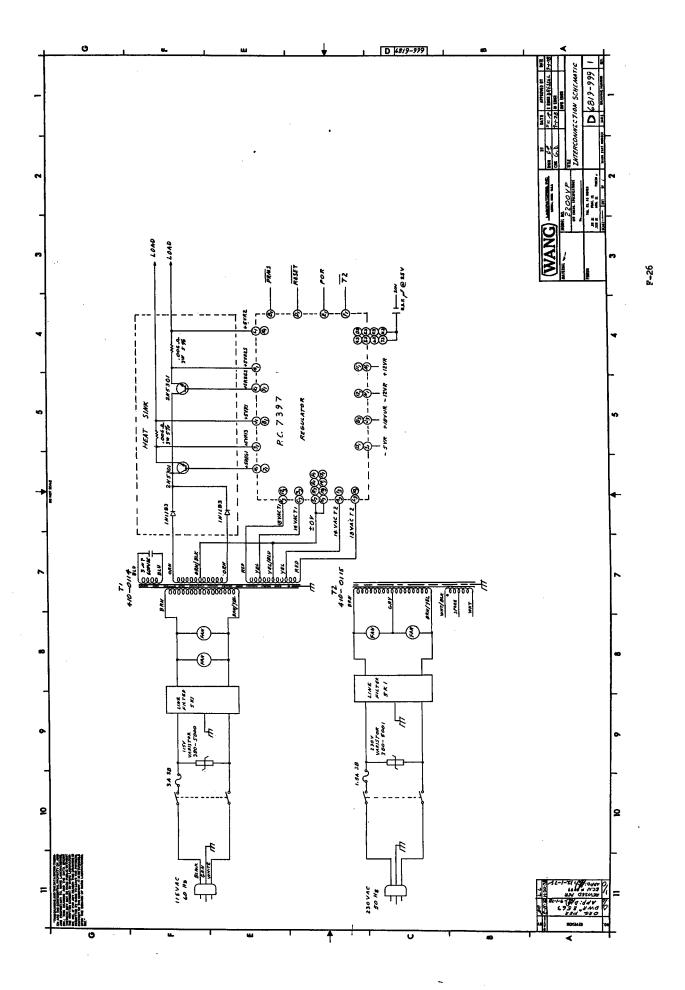

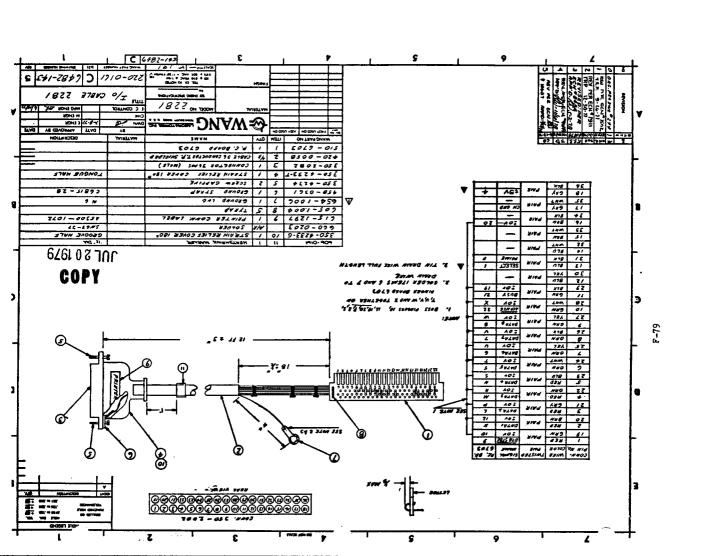

#### 3.3.2 2236MXD CONTROLLER BAUD RATE SWITCHES

For baud rate selection, there are three 8-bank switches (a total of 24 individual switches) located on the 7290-1 controller board. These switches comprise four groups of six switches each, with each group corresponding to a RS-232-C connector on the top panel. The switches in each group are labeled for specific baud rates: 300, 600, 1200, 2400, 4800, or 9600. See Figure 3-3.

Set the controller baud rate switches. Only one switch in any group of six may be ON at any one time. Remember that the baud rate setting for each connector must match the baud rate setting of the corresponding terminal.

#### NOTE:

The \$800 switch setting is used for both 4800 and 19.2K baud. The selected rate depends on the position of jumper A13, located between IC's L18 and L19. See Figure 3-3.

#### 3.4 DEVICE ADDRESSES

During system installation, a two-digit (HEX) device address must be set on the controller card for each peripheral device. The following paragraphs pertain to device selection. The first part of this section presents background information about device selection codes; the last part of the section is devoted to the actual procedures for setting device addresses.

#### 3.4.1 DEVICE SELECTION CODES

The controller for each peripheral attached to the CPU is assigned a unique Device Selection Code, consisting of three hexadecimal digits. The device selection code is in the form  $XY_1Y_2$ , where X is the Device Type (or Device Class) and  $Y_1Y_2$  is the Device Address (also called unit address or hardware address).

TABLE 3-1 SUMMARY OF DEVICE-TYPE CODES (DEVICE CLASSES)

| 1 <sup>st</sup> HEX DIGIT (X) | CATEGORY                                                                                                                                                                                                                    |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                             | Used with workstations (CRT and keyboard). Outputs a line feed (HEX OA) after each carriage return. Also used with nine-track tape drives.                                                                                  |

| 1                             | Not used.                                                                                                                                                                                                                   |

| 2                             | Used with printers and output writers that internally generate a line feed following a carriage return. Outputs a null character (HEX 00) after each carriage return.                                                       |

| 3,B                           | Used with disk drives and diskette drives.                                                                                                                                                                                  |

| 4                             | Used with plotters and plotting writers.  Plotting writers normally use type 4 (to plot) or type 2 (to print). System generated Carriage Return (HEX OD),  Line-Feed (HEX OA), and Null (HEX OO) characters are suppressed. |

| 5                             | Not used.                                                                                                                                                                                                                   |

| 6                             | Reserved for card readers; not used in MVP.                                                                                                                                                                                 |

| 7                             | Reserved for certain output applications;<br>not used in MVP. Does not output any extra<br>character after a Carriage Return (HEX OD)<br>is output.                                                                         |

| С                             | Used with certain plotter operations.                                                                                                                                                                                       |

TABLE 3-2 SUMMARY OF DEVICE-ADDRESS CODES

|                   | MODEL #                   | DESCRIPTION                                                                                                   | USUAL HEX<br>ADDRESS | ALTERNATIVE<br>HEX ADDRESSES |

|-------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|------------------------------|

| CRT's             | 2236D*                    | Interactive Terminal CRT Keyboard Local Printer/Plotter                                                       | 05<br>01<br>04       | 111                          |

|                   | 2282                      | Graphic CRT                                                                                                   | 13                   | 14, 15                       |

| Printers          | 2221W                     | Matrix Line Printer: 132 col/200 cps                                                                          | 15                   | 16                           |

|                   | 2231W-1<br>-2<br>-3<br>-6 | Matrix Line Printers: 112 col/120 cps<br>132 col/120 cps<br>132 col/120 cps<br>132 col/70 cps                 | · 元                  | 16                           |

|                   | 2251                      | Matrix Line Printer: 40 col/110 cps                                                                           | 15                   | 16                           |

|                   | 2261W                     | Matrix Line Printer: 220 LPM                                                                                  | 15                   | 16                           |

| ·                 | 2263-1<br>-2              | Chain Line Printers: 400 LPM<br>600 LPM                                                                       | 15                   | 16                           |

| Plotters          | 2232B                     | Digital Flatbed Plotter (31"x48")                                                                             | 13                   | 11                           |

|                   | 2272-2                    | Triple Pen Drum Plotter                                                                                       | 13                   | 14, 15                       |

| Output<br>Writers | 2201L<br>2271<br>2271P    | Output Writer: 156 col/15 cps<br>Bidirectional Output Writer: 15 cps<br>Bidirectional Plotting Output Writer: | 51<br>51             | 16<br>16                     |

|                   | 2281                      | 15 cps<br>Daisy Output Writer: 30 cps                                                                         | <del>2</del> 5       | 16<br>16                     |

|                   | 2281P                     | Daisy Plotting Output Writer: 30 cps                                                                          | 15                   | 16                           |

# These addresses are not user modifiable.

TABLE 3-2 SUMMARY OF DEVICE-ADDRESS CODES (continued)

|                    | MODEL #                                             | DESCRIPTION                                                                                                                                                                                                                   | USUAL HEX<br>ADDRESS | ALTERNATIVE<br>HEX ADDRESSES      |

|--------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------|

| Controllers 2227B  | 2227B                                               | Buffered Asynchronous Communications<br>Controller                                                                                                                                                                            | 10                   | 1A-1F                             |

|                    | 2228B                                               | Synchronous/Asynchronous<br>Communications Controller                                                                                                                                                                         | 51                   | 1A-1F                             |

|                    | 2228C                                               | Synchronous/Asynchronous<br>Communications Controller                                                                                                                                                                         | 51                   | 1A-1F                             |

|                    | 2230MXA-1<br>MXB-1                                  | Disk Multiplexer Controllers                                                                                                                                                                                                  | 10                   | 10-70                             |

|                    | 2236MXD*                                            | Interactive Terminal Multiplexer                                                                                                                                                                                              | 01-07                | 41-47                             |

| Storage<br>Devices | 2209A<br>2260BC<br>2260C<br>2280<br>2270A-1D<br>-2D | Nine-Track Tape (1600 BPI-PE) F/R Disk Drives (2.5, 5, 10 or 20 Mbytes) F/R Disk Drives (2.5, 5, 10 or 20 Mbytes) F/R Disk Drives (30, 60, or 90 Mbytes) Wang-IBM 3740 Compatible Diskette Drives .25 Megabytes .50 Megabytes | 7B<br>10<br>10<br>10 | 7D, 7F<br>10-70<br>10-70<br>10-70 |

\* All listed addresses are used by one device.

The device-type digit is used by the Operating System to determine which internal system I/O routines will be used to control the peripheral. This digit is needed because the various peripheral devices on the system often require different control procedures for performing an input/output operation. For example, a device-type digit of 3 indicates to the Operating System that the peripheral is a disk. Device type codes are summarized in Table 3-1.

The last two digits correspond to the actual unit's device address, which must be set on each device controller card in the 2200MVP CPU. The device address is used to electronically select the peripheral for operation. A unique device address must be assigned to each peripheral attached to the system.

When the 2200MVP is first turned on (Master Initialized), a set of default device addresses are supplied to the Master Device Table by the Operating System. These addresses will be valid in the system until changed in the Master Device Table or in the user's Local Device Table. Some addresses, like the local printer address of 204, are not modifiable by the user. See Table 3-2.

A system with one device belonging to a particular device class uses the first address for that class. Additional devices belonging to the same class are assigned the alternative address, as listed in Table 3-2.

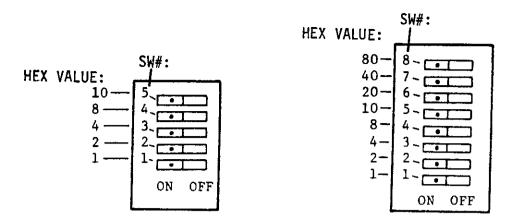

#### 3.4.2 SETTING THE DEVICE ADDRESS SWITCHES

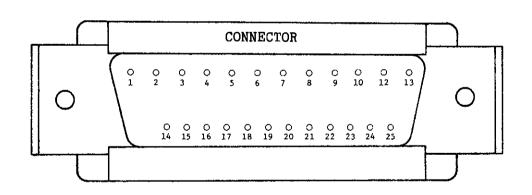

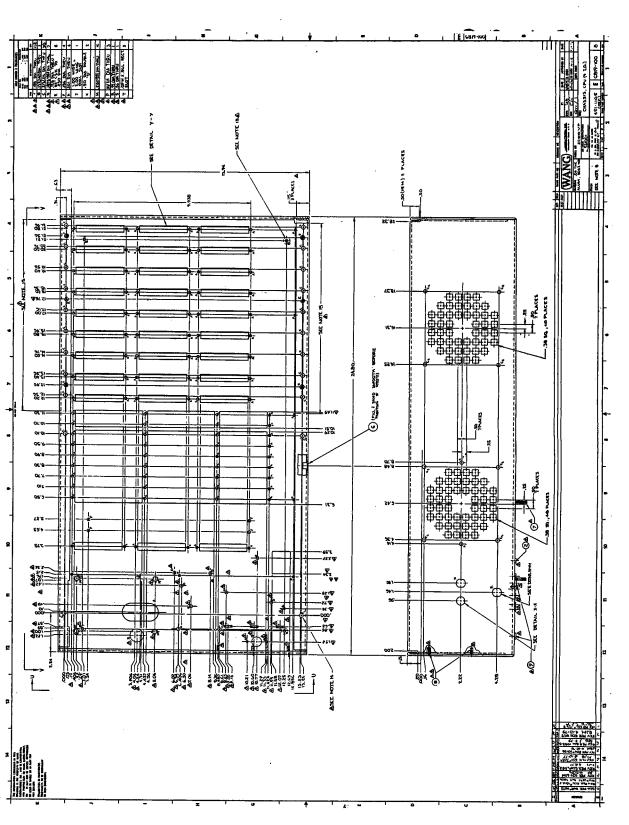

Controller boards generally have device address switches like the ones shown in Figure 3-4.

The three-digit device selection code  $(XY_1Y_2)$  is treated as follows:

FIGURE 3-4 TYPES OF CONTROLLER ADDRESS SWITCHES

TABLE 3-3 HIGH ORDER SWITCHES

| HEX VALUE | 80  | 40  | 20       | 10  |

|-----------|-----|-----|----------|-----|

| SWITCH #  | SW8 | SW7 | SW6      | SW5 |

| HEX DIGIT |     |     |          |     |

|           |     |     |          |     |

|           | İ   |     | <u> </u> |     |

| 0         | 0   | 0   | 0        | 0   |

| 1         | 0   | 0   | 0        | 1   |

| 2         | 0   | 0   | 1        | 0   |

| 3         | 0   | 0   | 1        | 1   |

| 4         | 0   | 1   | 0        | 0   |

| 5         | 0   | 1   | 0        | 1   |

| 6         | 0   | 1   | 1        | 0   |

| 7         | 0   | 1   | 1        | 1 1 |

| 8         | 1   | 0   | 0        | 0   |

| 9         | 1   | 0   | 0        | 1   |

| A         | 1   | 0   | 1        | 0   |

| В         | 1   | 0   | 1        | 1   |

| С         | 1   | 1   | 0        | 0   |

| D         | 1   | 1   | 0        | 1   |

| E         | 1   | 1   | 1        | 0   |

| F         | 1   | 1   | . 1      | 1   |

1 = Switch is ON; 0 = Switch is OFF

- X The most significant digit of the hex address. It is used by the Operating System to identify the device type of the peripheral. This digit is not used in device-address switch settings.

- Y<sub>1</sub> The next most significant digit of the hex address. This digit, broken down into four binary bits, determines the setting of switches 8 through 5. See Table 3-3.

- Y<sub>2</sub> The least most significant digit of the hex address. This digit, broken down into four binary bits, determines the settings of switches 4 through 1. See Table 3-4.

TABLE 3-4 LOW ORDER SWITCHES

|           | TABLE 3-4 | FOM OVDEV | DMTICUED |     |

|-----------|-----------|-----------|----------|-----|

| HEX VALUE | 8         | 4         | 2        | 1   |

| SWITCH #  | SW4       | SW3       | SW2      | SW1 |

| HEX DIGIT |           |           |          |     |

|           |           |           | r.       |     |

|           |           |           | ;        | 1   |

| 0         | 0         | 0         | 0        | 0   |

| 1         | 0         | 0         | Ò        | 1   |

| 2         | o         | 0         | 1        | 0   |

| 3         | 0         | 0         | 1        | 1   |

| 4         | o         | 1         | 0        | 0   |

| 5         | 0         | 1         | 0        | 1   |

| 6         | 0         | 1         | 1        | 0   |

| 7         | o         | 1         | 1        | 1 1 |

| 8         | 1         | 0         | 0        | 0   |

| 9         | 1         | 0         | 0        | 1   |

| A         | 1         | 0         | 1        | 0   |

| В         | 1         | 0         | 1        | 1   |

| С         | 1         | 1         | o        | 0   |

| D         | 1         | 1         | o        | 1   |

| E         | 1         | 1         | 1        | 0   |

| F         | 1         | 1         | 1        | 1   |

1 = Switch is ON; 0 = Switch is OFF

The device address conventions used in the 2200MVP system are as follows:

#### 2236MXD TERMINAL CONTROLLERS

Each 2236MXD Terminal Controller can support a maximum of four 2236D Interactive Terminals. When the system has four or less 2236D terminals, one 2236MXD controller is used. When the system has five to eight 2236D terminals, two 2236MXD controllers are used.

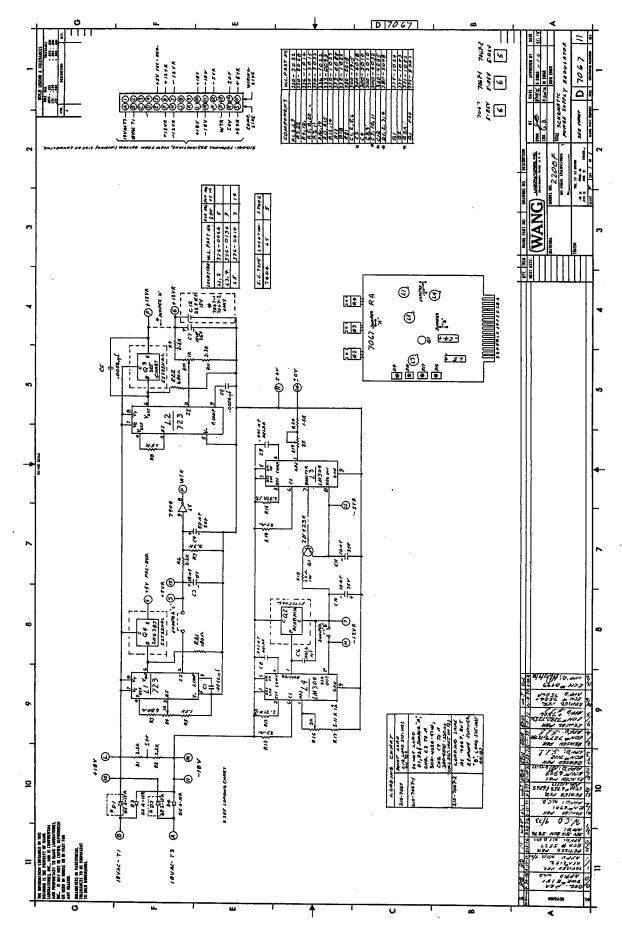

The 2236MXD controller address is set by means of a five-bank switch. See Figure 3-5. For systems with a single 2236MXD controller, set the controller address switches to 00; that is, all five switches in the bank must be OFF.

In systems using two 2236MXD controllers, set the address switches of the primary controller (the one with the system terminal in connector #1) to 00 (all switches OFF). Set the address switches of the other controller to 40 (switch #1 is ON; all others are OFF).

FIGURE 3-5 SETTING THE DEVICE ADDRESS OF THE 2236MXD CONTROLLER

Note that the physical device address set on the controller is not the address specified in a program for access to the 2236D terminal CRT, keyboard, and local printer. The programmable device addresses for all terminals are: 005 for a CRT; 001 for a keyboard; and 204 for a local printer. The Operating System translates these programmable addresses into the appropriate physical controller addresses.

#### **PRINTERS**

The system printer normally has the program address 215; therefore, the unit address switches of the 7079 Printer Controller must be set to HEX 15. In a configuration with two system printers, the address switches of the second printer controller would be set to HEX 16. As stated earlier, local printers (printers connected to the back of a 2236D Terminal) do not have any address switches but respond to an address of 204 under program control.

#### DISKS

If the diskette drive is the only disk unit on the system, the first (or leftmost) drive slot normally has the address 310, while the second drive slot has address B10. A third diskette drive slot will be addressed by 350.

If there are two separate disk drives in the system, one 6541-2 Disk Controller is to be set at 310 and the other at 320. For drives containing fixed (F) and removable (R) disk cartridges, device type 3 designates the fixed platter and the device type B designates the removable platter. In a configuration with two drives, the programmable addresses would thus be: 310 & B10 for the first drive; and 320 & B20 for the second drive.

The procedures for addressing disks when more than one s contained in the system are fully discussed in the 2200VP/MVP Disk Reference Manual.

#### **PLOTTERS**

Plotters are normally addressed by 413 or 414. For more specific addressing instructions, refer to the maintenance manuals listed in the preface of this manual.

#### 3.5 SYSTEM CABLE INSTALLATION

A comprehensive listing of system cables is presented in Section 1 of this manual. For complete information on the installation of specific peripherals, refer to the 2200MVP System-Level Documentation list.

If peripheral I/O cables are routed through conduit, ceilings, walls, or floors, it will may be necessary to install connectors on the ends of these cables. This procedure is given in the next paragraph.

#### 3.5.1 I/O CABLE CONNECTOR INSTALLATION

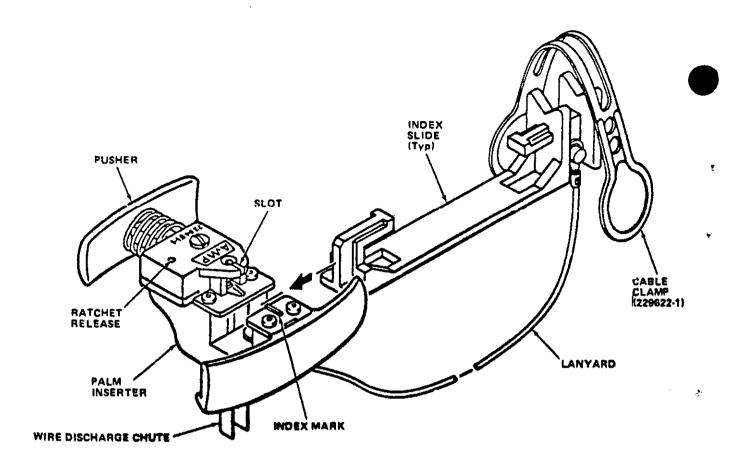

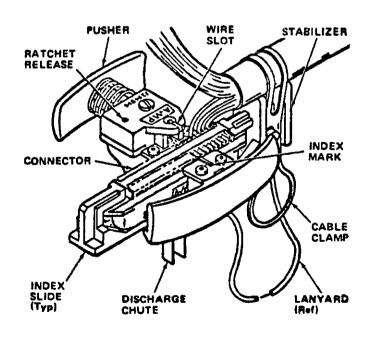

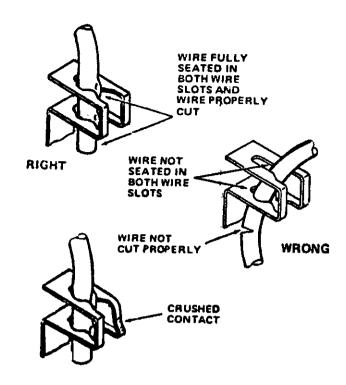

To install the I/O connectors, use a Champ Palm Grip Insertion Tool (PN 726-9412). The tool consists of a palm inserter, a lanyard, and an index slide. See Figure 3-6.

1. Position the connector in the index slide, attach the I/O cable to the slide, and then slide it into the palm inserter as indicated in Figure 3-7.

The I/O cable should be placed so as to allow 1/2 inch of sheathing to extend beyond the stabilizer. Four inches of unsheathed twisted pairs should be allowed for correct use of this tool.

- 2. Orient the palm inserter with the connector, making certain that a contact about to receive a wire is on the same side as the wire slot in the inserter.

- 3. Align the contact to be terminated with the index mark on the palm inserter.

- 4. Place the palm inserter so that the pusher faces towards the heel of your hand, and your fingers should grip the base (allow the wire discharge chute to extend through your fingers).

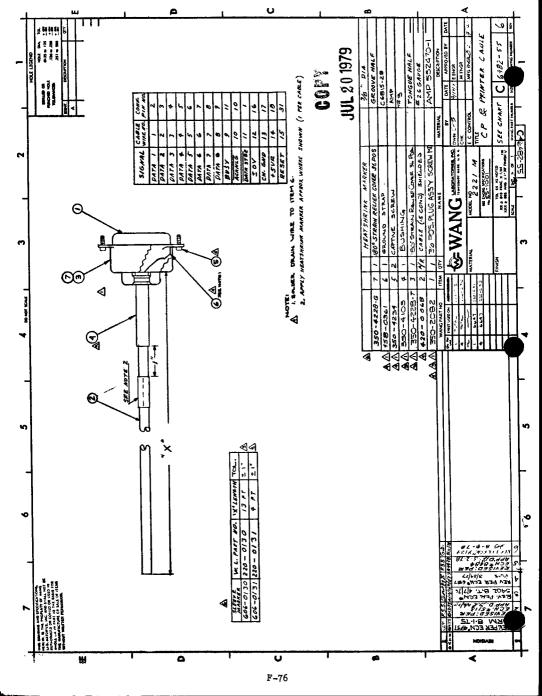

FIGURE 3-6 INSERTION TOOL

FIGURE 3-7 CONNECTOR INSTALLATION

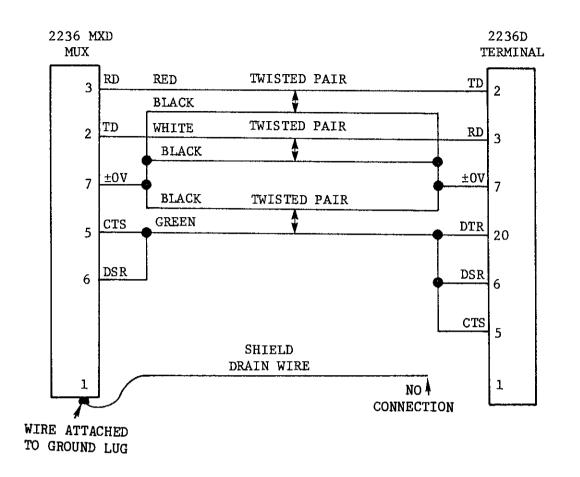

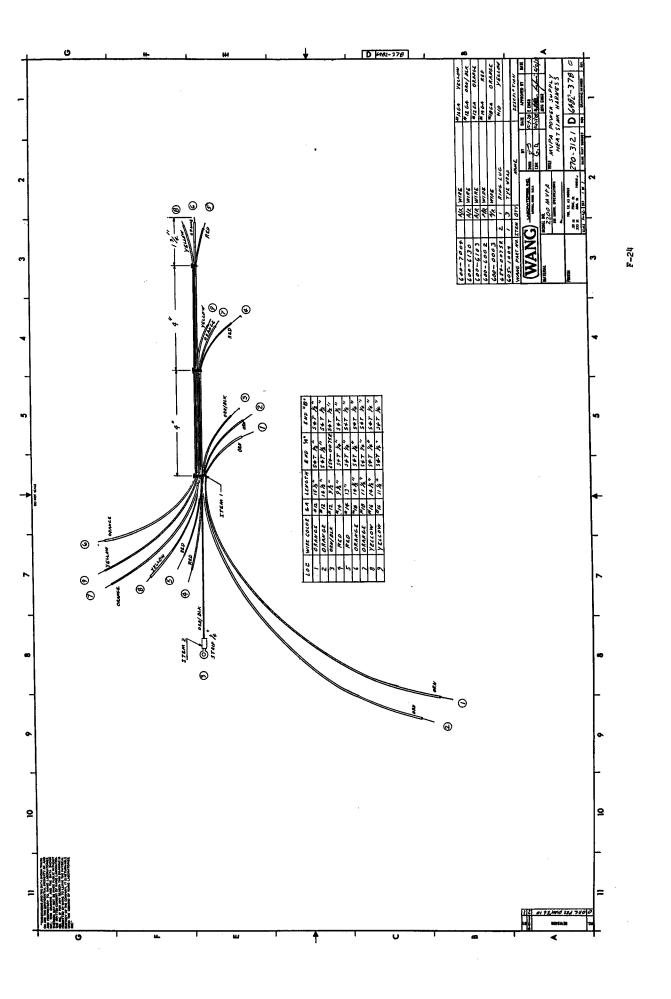

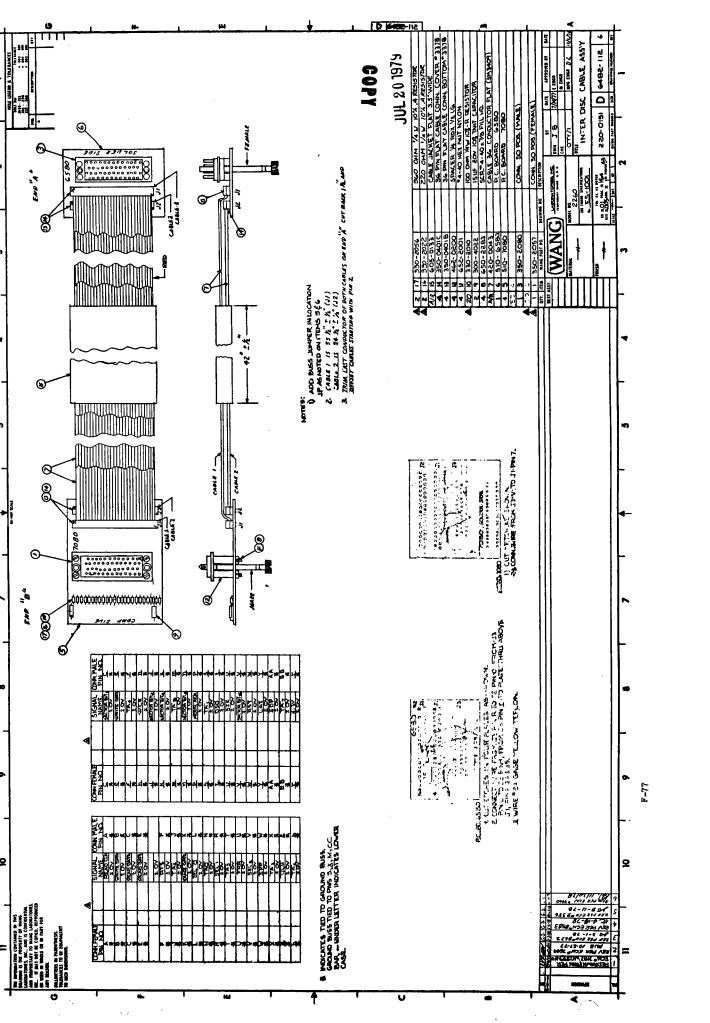

FIGURE 3-9 WIRING OF THE 2236 (RS-232-C) CABLE CONNECTOR

- 5. Select a wire of the proper color or number (see the cable assembly diagrams in the rear of this manual) and insert the wire through the wire slot and discharge chute; do this until all slack is out of the wire.

- 6. Make certain the contact and wire are centered on the index mark, and then squeeze the palm inserter until the pusher is bottomed.

- 7. Release your grip, allowing the pusher to retract.

#### NOTE:

If the palm inserter jams during this step, rotate the ratchet release in a clockwise direction with a hex wrench (supplied with the kit); this should effect release.

- 8. Remove the scrap wire from the discharge chute.

- 9. Repeat steps 1 through 8 until all contacts have been terminated on that side of the connector.

- 10. With the pusher released, remove the index slide and connector from the palm inserter.

- 11. Perform steps 1 through 10 for contacts on the other side of the connector.

- 12. After all contacts have been terminated, loosen the cable clamp and remove the index slide.

- 13. Inspect each termination, making sure that each wire has been FULLY inserted into BOTH wire slots of its contact (See Figure 3-8) and that all wires have been cut to the proper length (no exposed wire strands should be visible). Also, make sure that the insulation is NOT cut in any area other than the slot insertion area. Finally, make sure that the contacts are not crushed or deformed.

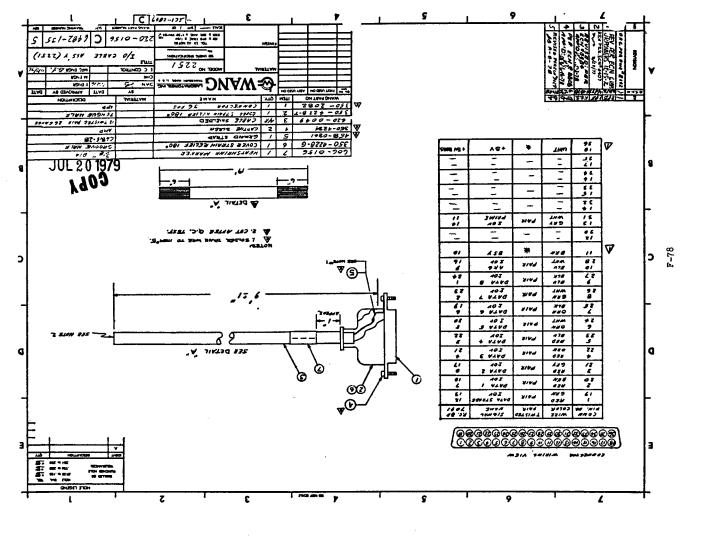

FIGURE 3-8 INSPECTING THE TERMINATIONS

If a faulty termination is found, carefully remove the wire and contact from its connector. Install another contact, trim 1/8 inch off the end of the faulty wire, and reinstall that wire, using steps 2 through 8.

- 14. Before the cover is installed on the 2236MXD connector, the I/O cable ground shield must be soldered to a ground lug, and that lug must be attached to the connector by one of the two screws.

- 15. Install a connector cover over the finished connector.

- 16. Connector installation is now completed.

#### NOTE:

The connectors for the 2236D Interactive Terminal are soldered on, and the cable insertion tool is not needed. The wiring diagram for the RS-232-C connector is shown in Figure 3-9.

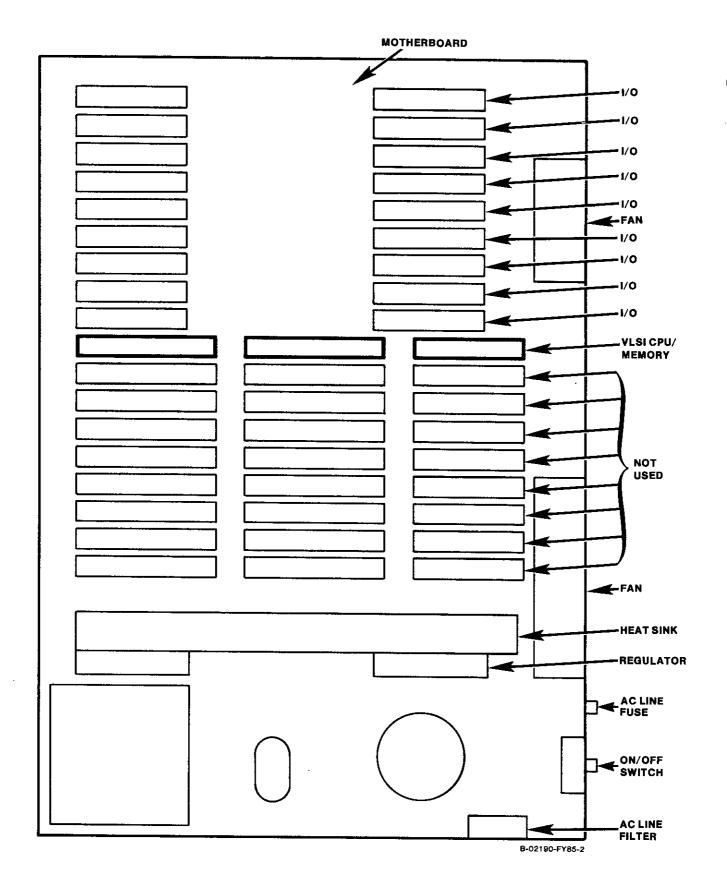

#### 3.6 MVP-A CHASSIS REQUIREMENT

The following paragraphs present a simplified method for determining whether or not the proper CPU chassis has been selected; that is, whether the system configuration requires the MVP Standard Chassis or the MVP-A Chassis. Ideally, this calculation should have been performed at the time the system was sold to the customer. Yet, because power supply damage will result if the total current demand of the controllers exceeds the rating of the chassis, it is important to perform this handy check prior to power-on testing of the system.

In this procedure, each peripheral controller is assigned a "configuration weight". All of the individual peripheral configuration weights are then added together to arrive at a "system configuration weight". The standard 2200MVP CPU will support a maximum system configuration weight of 100. If the system configuration weight exceeds 100, an MVP-A Chassis must be used.

The following listing specifies the configuration weights of most of the available 2200MVP peripherals.

|                | DESCRIPTION          | CONTROLLER | RATING |

|----------------|----------------------|------------|--------|

| CRT's          |                      |            |        |

| 2236D          | Interactive Terminal | 2236MXD    | 18     |

| 2282           | Graphic CRT          | 22002      | 6      |

| Mass Storage I | Devices              |            |        |

| 2209A          | Buffered 9-Track     |            | 17     |

|                | 1600 BPI             |            |        |

| 2260BC 1       | Disk Drive           | 22013      | 28     |

| 2260BC ½       | Disk Drive           | 22013      | 28     |

| 2260BC         | Disk Drive           | 22013      | 28     |

| 2260BC-2       | Disk Drive (dual)    | 22013      | 28     |

|                 | DESCRIPTION             | CONTROLLER | RATING |

|-----------------|-------------------------|------------|--------|

| Mass Storage I  | Devices (cont.)         |            |        |

|                 |                         |            |        |

| 2260C ‡         | Disk Drive              | 22C12      | 28     |

| 2260C ½         | Disk Drive              | 22C12      | 28     |

| 2260C           | Disk Drive              | 22012      | 28     |

| 2260C-2         | Disk Drive (dual)       | 22C12      | 28     |

| 2270A-D         | Diskette Drive          | 22003      | 4      |

| 2280-1,-2,-3    | Disk Drives             | 22C14      | 5      |

|                 |                         |            |        |

| Output Devices  | <u>s</u>                |            |        |

| 2201L           | Output Writer           | 22002      | 6      |

| 2221W           | Matrix Printer          | 22002      | 6      |

| 2231W (All)     | Matrix Printer          | 22002      | 6      |

| 2232B           | Flatbed Plotter         | 22001      | 8      |

| 2251            | Matrix Printer          | 22002      | 6      |

| 2261W           | High Speed Matrix       | 22002      | 6      |

| 2263-1,-2       | High Speed Matrix       | 22002      | 6      |

| 2271 & 2271P    | Bidirectional Printer   | 22002      | 6      |

| 2272-2          | Drum Plotter            | 22002      | 6      |

| 2281 & 2281P    | Daisy Wheel Printer     | 22C02      | 6      |

| Interfaces      |                         |            |        |

| 2227 <b>-</b> B | Async TC                |            | 8      |

| 2228-B          | Bisyne TC               |            | 16     |

| 2228-C          | Bisyne TC               |            | 18     |

| 2220-0          | Disylic 10              |            | 10     |

| Multiplexer Co  | ontrollers              |            |        |

| 22C11           | MVP Dual Controller     |            | 5      |

|                 | (Printer, Diskettes)    |            |        |

| 2230MXA-1       | Disk Multiplexer Contro | oller      | 8      |

| 2230MXB-1       | Disk Multiplexer Contro | oller      | 5      |

This list should be used in the following manner. First, make a list of all the peripherals that the system configuration contains, along with their ratings. Secondly, determine if dual controllers are being used. When these controllers are used, substitute their ratings in place of the ratings for the single peripheral controllers. Add together the ratings of all devices in the system configuration. If the sum is over 100, be certain that an MVP-A Chassis is being used. Good judgement must be used on any configurations bordering the maximum. Some allowance should be left for future system upgrades.

#### Notes on the above listing:

- a. Four Model 2236D Interactive Terminals may use a single 2236MXD Controller, which has a rating of 18.

- b. Local printers, which are connected to 2236D Terminals, do not contribute to the total system configuration weight.

- c. Note that the 2260BC disk drive might include a 2230MXA-1 (rating of 8).

- d. Memory size of the 2200MVP CPU does not contribute any configuration weight, even for systems that contain the maximum memory size of 256 Kilobytes.

- e. One other consideration is the use of 2228B or 2228C and 2236D controllers. A system should never be configured which contains more than three of the these controllers in a standard MVP chassis, or five of these controllers in an MVP-A chassis.

#### NOTE:

For system upgrades, the MVP chassis must be exchanged for an MVP-A chassis, WL# 270-0451 (50Hz) or WL# 270-0452 (60Hz). A conversion kit (WLI #200-0322) is available containing an MVP-A chassis and a 210-7397 regulator (to replace the standard 210-6797). The MVP-A makes 20 amps available to the I/O.

## Sample Calculations

# 1. Average MVP System

| Component          |                 | Configured Weight |

|--------------------|-----------------|-------------------|

| MVP-8 CPU          |                 | 0                 |

| 2236MXD Terminal M | ultiplexer      | 18                |

| (for three 2236D   | Terminals)      |                   |

| 2270A-1D Diskette  | Dual Controller | 5                 |

| 2261W Printer      | Dual Controller |                   |

| 2260BC Disk        | 22C13           | <u>28</u>         |

| Total Config       | ured Weight     | 51                |

| Total Number       | of I/O slots    | Ħ                 |

## MVP-A Chassis is not required

### 2. Large MVP System

| Component                      | Configured Weight |

|--------------------------------|-------------------|

| MVP-64 CPU                     | 0                 |

| 2 2236MXD Terminal Controllers | 36                |

| (for eight 2236D Terminals)    |                   |

| 2280 Disk Drive                | 5                 |

| 2260BC Disk Drive              | 28                |

| 2230 MXA-1 Disk Multiplexer    | 8                 |

| 2228B Bisynchronous TC         | 16                |

| 2209A 9 Track Tape Drive       | 17                |

| 2261W Matrix Printer           | 6                 |

| Total Configured Weight        | 116               |

| Total Number of I/O slots      | 8                 |

| Required                       |                   |

# MVP-A Chassis is required

#### 3.7 INSTALLATION/POWER-ON PROCEDURE

- 1. Be certain that the customer site has been prepared according to the the guidelines given in Section 2, and then place the system units in their assigned physical locations.

- 2. Set address switches on all I/O controllers per Section 3.4.2. Initially, plug only the first 2236MXD controller (address set to 00) and one disk controller into the CPU. Make sure the controllers are seated firmly. The system disk (or diskette) drive must be at address 310 or 320. Other peripherals and their respective controllers will be installed and tested in a later part of this procedure.

#### NOTE:

Set the baud rate switches in the 2236D terminals to match the baud rate switches in the 2236MXD controller.

3. Connect the 2236D terminals and system disk to their respective I/O controllers. Ensure that the peripheral cable connectors are securely fastened.

#### NOTE:

Be certain that the 2236D/2236MXD cable is installed correctly. One end of the cable is labeled MUX and the other end is labeled TER. Always insert the MUX end into the 2236MXD Controller and the TER end into the 2236D Terminal.

4. Make sure the AC power switches of all system units are in the OFF position, and then plug in all AC power cords.

#### NOTE:

Check peripherals to see that all (115/230) AC voltage switches and (50Hz/60Hz) line frequency switches are set to match the wiring at the customer site.

- 5. One at a time, turn on the AC power switch for each unit in this minimal system configuration, using the correct power-up sequence: first the CPU, then the disk, and then the terminals.

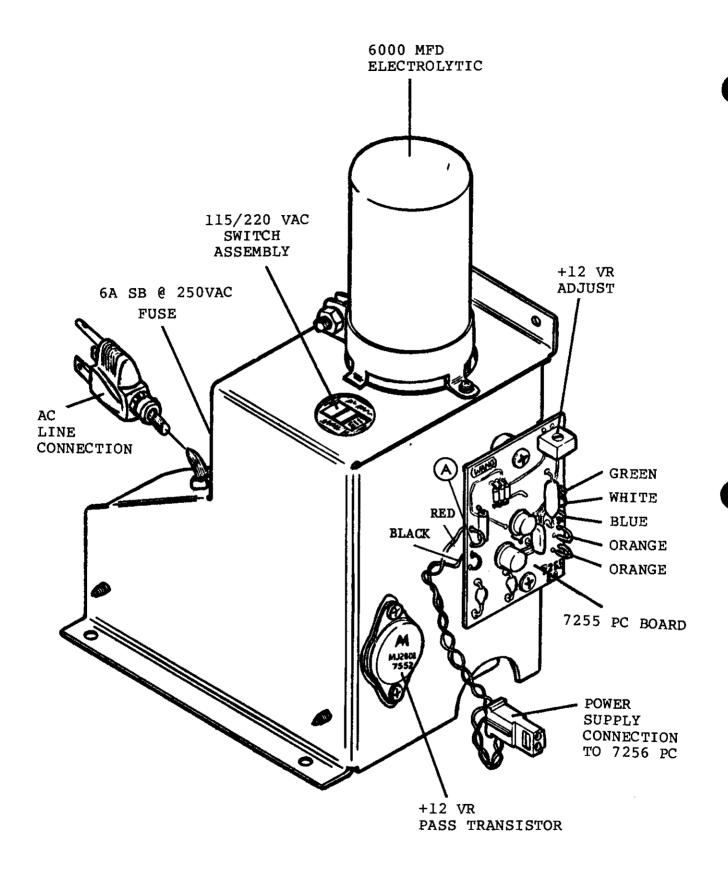

- 6. Check, and adjust if necessary, the voltages in the CPU and 2236D terminals per voltage adjust procedure in section 7.3.2. Replace the top covers when this has been completed.

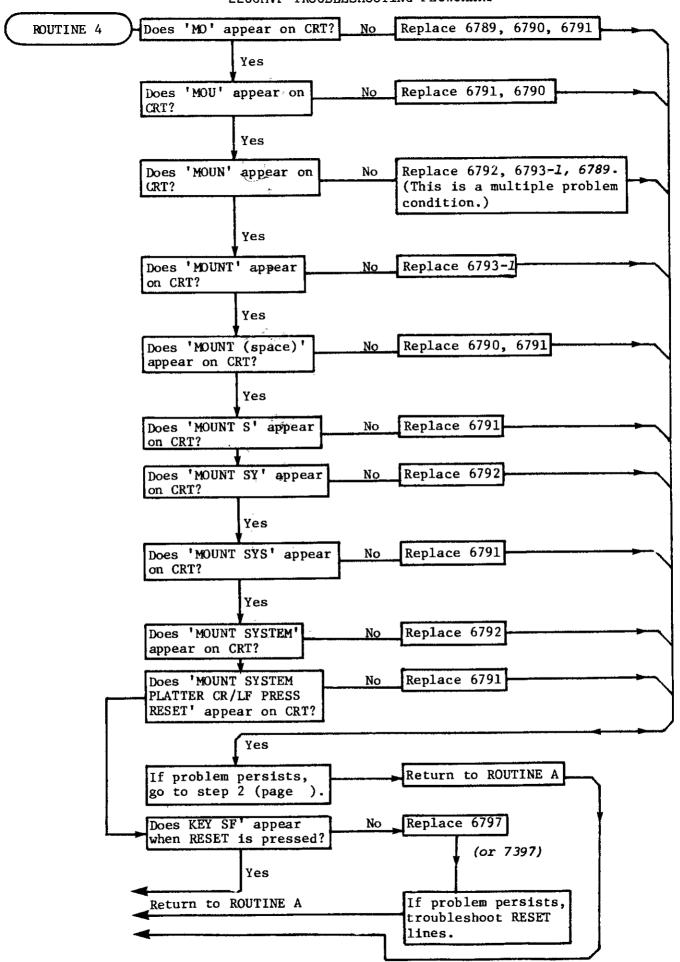

- 7. At this point, the 2236D Terminal connected to port #1 of the 2236MXD should be displaying in the upper left corner:

MOUNT SYSTEM PLATTER PRESS RESET

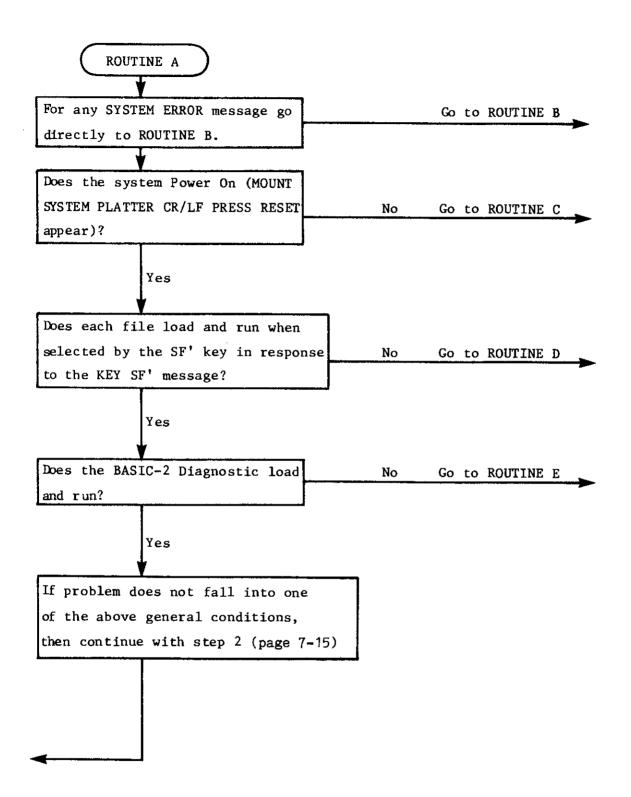

If this message is not displayed, turn the AC power switch of the CPU to OFF. After 4 or 5 seconds, turn the switch back on. If the message is still not displayed, refer to sections 3.9.1 and 7.4.1.

8. When the message:

MOUNT SYSTEM PLATTER PRESS RESET

is displayed, place the System Platter Diskette (701-2294H) into the system diskette drive and press the RESET key on the keyboard.

- 9. The message "KEY SF'?" should now be displayed.

- 10. There are only three selections that can be made with the function keys when the "KEY SF'?" message is displayed. BASIC-2 can be loaded, the User Menu of diagnostics can be loaded or the Field Service Menu of diagnostics can be loaded. The operator should now select the User menu (SF'16 SF'19 for disk address of 310, B10, 320, or B20, respectively). Refer to sections 3.9.2 and 7.4.1 in case of trouble.

The following should be displayed:

KEY SF'

USER DIAGNOSTIC MENU

'00 CPU DIAGNOSTIC

'02 DATA MEMORY DIAGNOSTIC

'O1 CONTROL MEMORY DIAGNOSTIC

#### 11. Press SF'00

LOADING CPU DIAGNOSTIC (DATE)

should be displayed for approximately 5 seconds;

then,

CPU DIAG PASS LLLL

IMMED REG XX

REG INSTR XX

X-REG INSTR XX

MASK BR XX

REG BR XX

IMMED R/W XX

REG R/W XX

AUX/STACK R/W XX

should be displayed. See section 6.3.1 for interpretations of the CPU Diagnostic.

This test runs continuously until either an error occurs or RESET is keyed.

When satisfied that a sufficient number of successful test passes have occurred (5 to 10 minutes), key RESET. The User Menu is reselected by pressing the appropriate SF Key after each diagnostic; any other diagnostic may then be selected.

#### 12. Press SF'01

LOADING CONTROL MEMORY DIAG (DATE)

should be displayed for approximately 5 seconds; then,

\*\*\* CONTROL MEMORY DIAGNOSTIC\*\*\* MEMORY SIZE = OXXXK

NO ERR'S PRESS 'P' TO PRINT ERRORS at ('T' FOR /204)

PRESS 'CONTINUE' TO START-

should be displayed. Press "CONTINUE" and the last line of the display should change to:

ADDRESSING TEST (PASS 0001)

Upon completion of this test, the prompt will be changed to:

MAT C&S TEST (PASS 0001)

Upon completion of this test, the last line of the display will change to:

ROWPAT TEST (PASS 0001)

These SF'01 tests are repeated in sequence until either an error occurs or RESET is keyed. When satisfied that a sufficient number of successful test passes have occurred (5 to 10 passes), key RESET. The User Menu should once again be reselected. See paragraph 6.3.2 for interpretations of the Control Memory diagnostic.

13. Press SF'02 (Data Memory Diagnostic)

The display should be similar to the one for the Control Memory diagnostic except that "CONTROL" will be replaced by "DATA" and the memory size will change.

SF'02 Data Memory Tests are also repeated in sequence until either an error occurs, or RESET is keyed. When satisfied that a sufficient number of successful test passes have occurred (5 to 10 passes), key RESET. See section 6.3.3 for interpretations of the Data Memory Diagnostic.

14. When all diagnostics listed in the User Menu have been completed, key RESET and select the Field Service Menu.

To load the Field Service Diagnostic Menu, key SF'28, SF'29, SF'30 or SF'31 for disk addresses of Hex 310, Bl0, 320, or B20, respectively.

After the appropriate SF' Key is pressed, the following will be displayed:

KEY SF'?

#### FIELD SERVICE DIAGNOSTIC MENU

| 00          | CPU DIAGNOSTIC | 105 | MAT C & S 8         |

|-------------|----------------|-----|---------------------|

| '01         | ADDRESS 24     | 106 | ROWPAT 8            |

| 102         | MAT C & S 24   | '07 | REGISTERS           |

| 103         | ROWPAT 24      | 108 | AUXILIARY REGISTERS |

| <b>'</b> 04 | ADDRESS 8      | 109 | STACK REGISTER      |

Note that User Diagnostics comprise merely the individual Field Service Diagnostic tests, not including the Field Service Register tests. Therefore, Register tests must be accessed from the Field Service Menu and run for any power-up and/or installation.

Tests initiated from the Field Service Menu are normally used for troubleshooting purposes.

15. Key SF'07. Once the Register Diagnostic is loaded and begins to execute, key RESET and then function key 15. The Register Diagnostics are chained together by this operation and will run sequentially just as the diagnostics in the User Menu did, stopping only on an error or RESET.

See section 6.3.4 for interpretations of the Register Diagnostics.

- 16. After running the Field Service Register diagnostics, key RESET and load BASIC-2. BASIC-2 is loaded by keying the coresponding SF' key ('00 for 310, '01 for B10, '02 for 320, '03 for B20).

- 17. Once BASIC-2 is loaded and "READY (BASIC-2)" is displayed, the system platter should be removed from the disk drive.

- 18. Place the disk which contains the BASIC-2 Language Diagnostic (701-2261) in the disk drive and key LOAD, RUN EXECUTE, at each 2236D Terminal.

- 19. When satisfied that a sufficient number of successful test passes have occurred, key HALT/STEP.

- 20. After the microcode diagnostics and the BASIC-2 Language Diagnostics have been executed without failure, turn the CPU power OFF and insert all remaining I/O Controllers.

- 21. Install all the remaining peripherals in the system configuration. Check and adjust the voltages of the other peripherals as described in their specific maintenance manuals, making mechanical checks and adjustments where applicable.

- 22. Power up the system. Again run the diagnostics in this section to check for proper system operation. Execute the peripheral diagnostics described in section 6.

#### 3.8 BOOTSTRAP

A BOOTSTRAP, by definition, is a "technique or device designed to bring itself into a desired state by means of its own action."

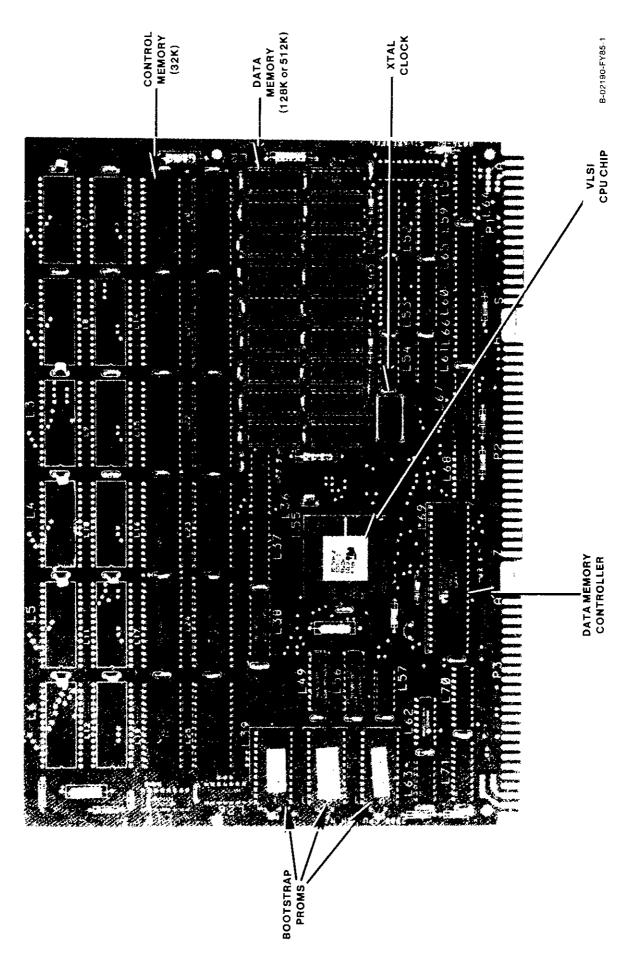

In general, the Wang MVP BOOTSTRAP, is a set of microcoded routines loaded in three 1024 x 8 bit Intel 2708 PROMs. The purpose of the BOOTSTRAP is to handle four system functions and make available certain subroutines which are used for I/O operations.

#### IMPORTANT:

The BOOTSTRAP described is release 2.2 (R1 PROMS) of the VP/MVP Bootstrap, implemented in all MVP Systems on September 1, 1978.

The four system functions handled by BOOTSTRAP are:

- 1) Master Initialization (Power-On).

- 2) Reset (Initiated by depressing the RESET key on the keyboard).

- 3) Control and Data Memory Parity Error Detection.

- 4) Loading the desired system software (i.e., diagnostics, or BASIC-2) from disk and initiating their execution.

An explanation of each of the above functions follows.

#### 3.8.1 MASTER INITIALIZATION

Master Initialization begins by turning the CPU power switch to the ON position. A branch to Control Memory address 8003 (HEX), located in the BOOTSTRAP PROMs, is executed and the BOOTSTRAP routine begins controlling and performing its various tasks.

The tasks performed by the Master Initialization routine in BOOTSTRAP are:

- a) To exercise the CPU to determine if any obvious malfunctions exist.

- b) To verify the BOOTSTRAP PROMs still maintain the desired data.

- c) To write zeros to all locations in Data Memory in preparation for subsequent Data Memory Reads.

If all Master Initialization tasks are completed satisfactorily, the prompt "MOUNT SYSTEM PLATTER CR/LF PRESS RESET" will be displayed.

#### 3.8.2 RESET

Reset is initiated by depressing the RESET key located in the upper right hand corner of the keyboard. This action causes the execution of a branch to Control Memory address 8001 (HEX), located in BOOTSTRAP PROMs.

The tasks performed by Reset are:

- (a) To pass control to the loaded system program currently loaded, located in Control Memory (BOOTSTRAP, Microcode Diagnostics, or BASIC-2).

- (b) To allow the user to recover from any of the various system error conditions which may be encountered.

- (c) To abort a BOOTSTRAP load.

Should task a) be called for, the user may expect those messages and/or actions designed into the particular system program, that is, a display a menu of user-selectable software (key Special Function), or for instance, a return to a starting point in the current software in Data Memory.

Otherwise, whenever task b) is to be performed, the user is expected to inform the BOOTSTRAP of what action to take (by keying a Special Function, for instance).

If the expected response does not occur on RESET, consult section 3.9.2 and 7.4.1.

#### 3.8.3 CONTROL AND DATA MEMORY PARITY ERRORS

In both Data and Control Memory a bit has been set aside, called the parity bit, to aid in error detection.

In Control Memory, bit 24 is set aside for parity; it is turned on whenever the even number of the remaining bits turns on. This is called ODD Parity. This bit must be properly set when writing the instruction into Control Memory.

In Data Memory, a ninth bit is used in the same manner as described above. However, the hardware determines and sets this bit, whenever a write is executed into Data Memory.

Whenever the system detects bad parity in Control Memory, during an instruction fetch, a branch is made to location 8000, located in the BOOTSTRAP PROMS. The BOOTSTRAP will then perform its designated task.

Similarly, whenever the system detects bad parity in Data Memory, during a read from Data Memory, a branch is made to location 8002, located in the BOOTSTRAP PROMS. The BOOTSTRAP will then perform its designated task.

Whenever a trap to location 8000 and 8002 is executed by the system, the appropriate display is made.

### 3.8.4 LOAD SYSTEM FILES

Whenever the operator has made a response to the BOOTSTRAP requesting a system file to be loaded, the following tasks are performed.

- a) Check if the disk is ready.

- b) Verify whether the file exists on the mounted platter.

- c) Load the file into Control and/or Data Memory.

- d) Verify Control Memory checking instruction parity and built in CRC and LRC checksums.

- e) Check Data Memory Parity.

- f) Pass control to the newly loaded system file.

### 3.9 BOOTSTRAP ERROR MESSAGES AND RECOVERY

Three types of errors and five possible error messages can be reported by BOOTSTRAP. These error types--initalization, reset, and system--are discussed below.

### 3.9.1 INITIALIZATION ERRORS

The BOOTSTRAP, during Master Initialization, fails to display the complete

MOUNT SYSTEM PLATTER PRESS RESET

message upon the CRT.

This error implies that some function of the MVP has failed. This may be either a CPU-related error or an I/O-related error.

In some cases, a device address may need to be corrected and the system powered on again.

The Master Initialization sequence is described on the following pages.

MASTER INITIALIZATION

# Step-By-Step Breakdown of Function

| CRT DISPLAY      | SEQUENCE OF OPERATIONS                                                  | POSSIBLE FAILURES                                                                                                                                                              |                      |

|------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                  | 1. Power On Trap to 8003.                                               | <ol> <li>Hardware Trap Failure.</li> <li>Branch Instruction Failure.</li> </ol>                                                                                                |                      |

| CLEAR SCREEN     | 2. Enable CRT, Clear Screen and Display "M".                            | 2. CRT Address is wrong.<br>I/O Register Pailure.<br>I/O Lines are Bad.<br>CIO Instruction Failure.                                                                            |                      |

| ±W <sub>11</sub> | 3. Test 24-Bit Parity Trap.<br>Execute IC 800F which has<br>Bad Parity. | Parity Checking Logic Failure. Hardware Trap Failure. TSP Instruction Failure (IC + 1 stored in stack) PC's may not hold IC retrieved from Stack. Compare Instruction Failure. | rom Stack.           |

| "OM"             | 4. Test Subroutine Branch and Subroutine Return Instructions.           | 4. Subroutine Branch Instruction Fallure.<br>Subroutine Return Instruction Fallure.<br>Stack Failure.                                                                          | Fallure.<br>Fallure. |

| #UOM#            | 5. Clear CH, CL Parity Bits.                                            | 5. Write/Read Data Memory Fallure.                                                                                                                                             |                      |

| "MOUN"           | 6. Check File Registers.                                                | 6. Register Instruction Fallure.<br>Register Chip Fallure.<br>Compare Instruction Fallure.                                                                                     |                      |

| "HOUNT"          | 7. Check PC Incrementing on the A-BUS.                                  | 7. PC Chip Failure. LPI Instruction Failure. Register Instruction Failure. A-Bus Increment Hardware Failure. Compare Instruction Failure.                                      |                      |

| "S TNUOM"        | 8. Test Auxiliary Registers.                                            | 8. Auxiliary/Stack Chip Failure.<br>PC Chip Failure.<br>Auxiliary Register Instruction F<br>Compare Instruction Failure.                                                       | Fallure.             |

MASTER INITIALIZATION Step-By-Step Breakdown of Function (Continued)

| CRT DISPLAY                          | SEQUENCE OF OPERATION          | POSSIBLE FAILURES                                                                                                                                 |

|--------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| "MOUNT SY"                           | 9. Test Binary ALU.            | 9. Binary ALU Failure.<br>AC, ACX, AI, SC or SCX Instruction Failure.<br>Compare Instruction Failure.                                             |

| "Mount sys"                          | 10. Test Stack.                | <pre>10. Auxiliary/Stack Chip Failure. PC Chip Failure. Stack Instruction Failure. Compare Instruction Failure.</pre>                             |

| "MOUNT SYST"                         | ll. Test Decimal ALU.          | 11. Decimal ALU Failure.<br>DAC, DACI, DACX, DSC, DSCI or DSCX                                                                                    |

| "MOUNT SYSTE"                        | 12. Test Binary Multiply.      | Instruction Failure. Compare Instruction Failure. 12. Multiply Hardware Logic Failure. M OR MI Instruction Failure. Compare Instruction Failure.  |

| "MOUNT SYSTEM"                       | 13. Test Shift.                | 13. Shift Logic Error.<br>Compare Instruction Failure.                                                                                            |

| "MOUNT SYSTEM "                      | 14. Verify PROM.               | 14. PROM Chip Failure.                                                                                                                            |

| "MOUNT SYSTEM P"                     | 15. Zero 8-Bit Data Memory.    | 15. SR Failure.<br>Bad IC's.                                                                                                                      |

| "MOUNT SYSTEM PLATTER" "PRESS RESET" |                                |                                                                                                                                                   |

|                                      | 16. Write/Read Control Memory. | 16. WCM/RCM Instruction Failure. Stack Failure. Auxiliary Register Failure. PC Chip Failure. SB Instruction Failure. Compare Instruction Failure. |

MASTER INITIALIZATION Step-By-Step Breakdown of Function (Continued)

| 17. System Loops, diagnosing data and control memory. To resume depress RESET. (This aids in initializing the disk). | CRT DISPLAY | SEQUENCE OF OPERATIONS                                                                                               | POSSIBLE FAILURES |

|----------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                                                                      |             | 17. System Loops, diagnosing data and control memory. To resume depress RESET. (This aids in initializing the disk). |                   |

### 3.9.2 RESET ERRORS

During the Reset function, when the operator has properly responded to the "KEY SF'?" message by keying the desired special function key:

The hexdigit display of the keyed special function did not appear upon the CRT.

This implies that the special function key was not depressed sufficiently, or the 2236D or 2236MXD may be defective, or an SF' key not defined was depressed.

### NOTE:

During the RESET function, several of the SYSTEM ERROR messages may appear. If one does, consult the recovery procedure for that particular message, given in section 3.9.3.

The system reset sequence is described on the following pages.

SYSTEM RESET Step-By-Step Breakdown of Function

| CRT DISPLAY              | SEQUENCE OF OPERATIONS                                                                                              | POSSIBLE FAILURES                                                                                                                                    |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | 1. Reset has been keyed while<br>BOOTSTRAP is in control.                                                           | 1. Reset Trap Error.                                                                                                                                 |

| Clear Screen             |                                                                                                                     |                                                                                                                                                      |

|                          | 2. Enable Keyboard (address = 01) and accept Special Function key input. Operator keys the desired SF key.          | <ul><li>2. Inactive SF 1s keyed. Keyboard address 01.</li><li>I/O Register Failure.</li><li>I/O Lines Failure.</li><li>CRB or KFN Failure.</li></ul> |

|                          | NOTE: if any undefined SF'<br>key is despressed, the "KEY<br>SF" message re-appears and<br>step 2 must be repeated. | Keyboard Failure.                                                                                                                                    |

| *"KEY SF'?" name platter |                                                                                                                     |                                                                                                                                                      |

|                          | 3. Enable specified disk.                                                                                           | 3. Improper disk address. I/O Register Failure. I/O Lines Failure. Disk Not Powered On. Disk Not Ready.                                              |

|                          | 4. Search disk for desired<br>file. If file cannot be<br>found, Step 2 is repeated.                                 | <pre>4. Wrong Special Function key   depressed. Wrong disk mounted.</pre>                                                                            |

\*The name of the file to load and the platter to load from is displayed.

SYSTEM RESET

Step-By-Step Breakdown of Function

(Continued)

|             |                        | <del>                                    </del>                                                                                                                                                                                                                                                                                                                                              | <del></del>                                                                                                                                             |                                                                                                                                      |                                                                                                                                     |

|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|             | POSSIBLE FAILURES      | 5. I/O Register Failure.<br>I/O Lines Failure.<br>Disk Problems.                                                                                                                                                                                                                                                                                                                             | 6. Memory Failure.<br>WCM/RCM Instruction Failure.                                                                                                      | 7. Memory Fallure.<br>Read/Write Instruction Failure.                                                                                |                                                                                                                                     |

| (Continued) | SEQUENCE OF OPERATIONS | 5. Load desired file from disk into Memory NOTE: System files should contain a comment block containing file date.  If a disk error results, the system error message will appear. Consult Error Recovery, for proper procedure. If a parity error occurs during loading 'P' will be displayed and the previous sector will be reloaded. If no control memory data is found, skip to step 9. | 6. Verify Control Memory. (Parity, LRC & CRC). If an error results, the system error message will appear. Consult Error Recovery, for proper procedure. | 7. Check 8-Bit Data Memory. If an error results, the system error message will appear. Consult Error Recovery, for proper procedure. | 8. Control is passed to loaded system file which now takes over control. Consult proper system file documentation. (Address = 3000) |

|             | CRT DISPLAY            | "KEY SF1?" name platter                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                         |                                                                                                                                      |                                                                                                                                     |

SYSTEM RESET

Step-By-Step Breakdown of Function

(Continued)

| CRT DISPLAY             | SEQUENCE OF OPERATIONS                                                                                                        | POSSIBLE FAILURES                                                                                                                |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                         | 9. Display Diagnostic Menu<br>listing upon CRT.                                                                               |                                                                                                                                  |

| "KEY SF'?"              |                                                                                                                               |                                                                                                                                  |

|                         | 10. Enable Keyboard (address = 01) and accept Special Function key input. Operator keys the SF key of the desired diagnostic. | 10. Inactive SF is keyed. Keyboard (address = 01) I/O Register Failure. I/O Lines Failure. CRB OR KFN Failure. Keyboard Failure. |

| "KEY SF'?" name platter |                                                                                                                               |                                                                                                                                  |

|                         | 11. Go to Step 4.                                                                                                             |                                                                                                                                  |

### 3.9.3 SYSTEM ERRORS

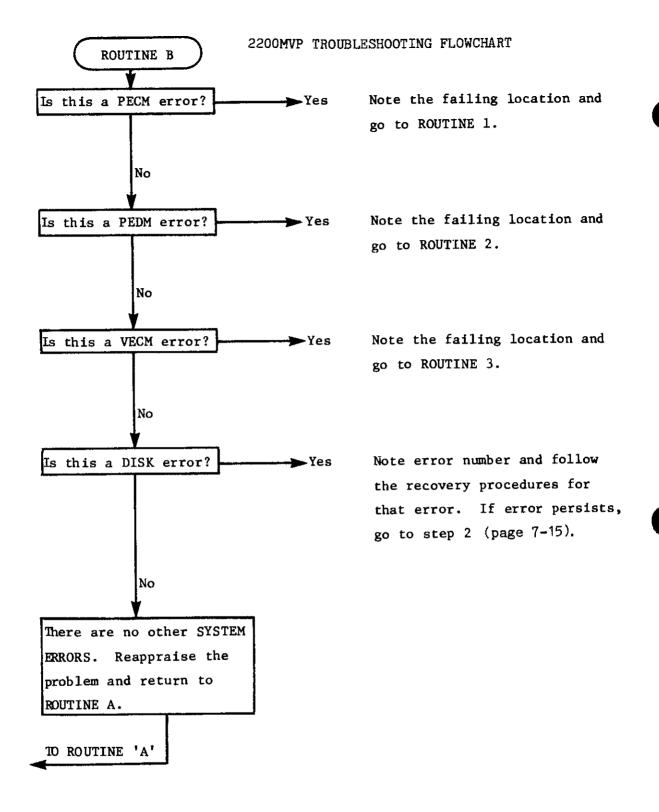

The third grouping of error conditions is reported to the operator via a SYSTEM ERROR message on the CRT.

First, should memory fail, the following message will appear:

\*\*\* SYSTEM ERROR MMMM XXXX \*\*\*

PRESS RESET

where MMMM - PECM = Parity Error Control Memory

PEDM = Parity Error Data Memory

VECM = Verify Error Control Memory

VEDM = Verify Error Data Memory

XXXX - Various error information pertinent to the type of error.

Secondly, a disk error will result in the following message being displayed:

\*\*\* SYSTEM ERROR DISK OOXX \*\*\*

PRESS RESET

where OOXX - is the Disk Error Code

The procedure used to recover from these SYSTEM ERRORS is similar. Therefore, the general procedure will be outlined and each error will be discussed.

The general procedure is:

- a) Key RESET in response to the "PRESS RESET" message on line 2 of the CRT.

- b) Choose one of the four following courses of action.

- 1. Key SF'15 to resume, using the currently loaded system program (usually BASIC-2).

- 2. Key SF'00-'05, '08-'013 to load BASIC-2 from disk 310, B10, 320, B20, 330, B30, 350, B50, 360, B60, 370 or B70.

- 3. Key SF'16-'19 to load a diagnostic menu from disk 310, Bl0, 320, or B20, respectively.

- 4. Key SF'28-'31 to load the Field Service Diagnostic menu from 310, B10, 320, or B20, respectively.

Use special caution when you choose #1 above: depending on what type of error and where it occured, BASIC-2 may not function properly in all cases.

The following discussion will outline each of the SYSTEM ERRORS and what may be done, in particular, to recover from them.

### 3.9.3.1 CONTROL MEMORY ERRORS

And Section

In both Data Memory and Control Memory, one bit has been set aside for parity error detection.

In Control Memory, the 24th bit (bit #23) of every micro-instruction is set aside for parity (it is turned ON whenever an even number of the remaining 23 bits turns on). This is called ODD Parity. This bit must be properly set when writing the instruction into Control Memory.

### \*\*\* SYSTEM ERROR (PECM aaaa dddddd) \*\*\*

This error implies that bad parity was detected while the system was trying to execute an instruction from Control or BOOTSTRAP Memory.

Whenever the system detects bad parity in Control Memory (PECM message) during an instruction fetch, a branch is made to Control Memory address 8000 (HEX), located in the BOOTSTRAP PROMs. The BOOTSTRAP then performs its designated error routine and displays PECM aaaa, dddddd.

Bad parity may be the result of:

- a) dropping of bits by Control/BOOTSTRAP Memory

- b) picking up of bits by Control/BOOTSTRAP Memory